一种正装LED芯片制备方法与流程

一种正装led芯片制备方法

技术领域

1.本发明涉及半导体技术领域,特别涉及一种正装led芯片制备方法。

背景技术:

2.常规正装led芯片一般包括msa、tcl、cbl、pad、psv以及msa的作用是刻蚀掉部分p型gan露出部分n型gan,tcl是作为电流扩展层,cbl作为电流阻挡层使电流扩散的更加均匀,pad则作为led的正负极以形成正常的导电导通来点亮led芯片,psv则作为保护层,防止外界的水汽等对led芯片造成失效影响,还得露出部分pad便于正装打线的操作。

3.现有技术当中,为了防止金属迁移采取p型gan外延层、n型gan外延层接触的电极位置相对较远、或者缩小电极的尺寸,也就是相当于变相增大正负极的距离来,可以有效解决金属迁移的问题,但是当正装led芯片尺寸越来越小时正负极之间的距离已缩无可缩,而且为了打线电极的大小又不可太小,不然后续在进行封装时难度又会过高,增大正装led芯片的封装成本,没有办法兼顾金属迁移问题的同时,又保证后续封装的正常进行。

技术实现要素:

4.基于此,本发明的目的是提供一种正装led芯片制备方法,以至少解决现有技术当中的不足。

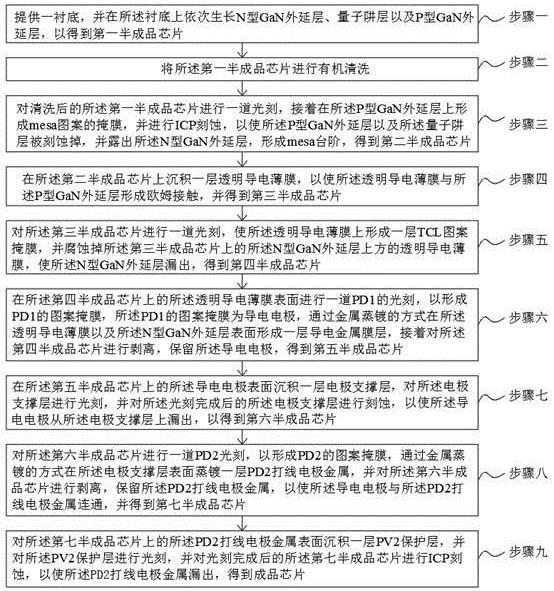

5.本发明提供以下技术方案,一种正装led芯片制备方法,所述制备方法包括:步骤一,提供一衬底,并在所述衬底上依次生长n型gan外延层、量子阱层以及p型gan外延层,以得到第一半成品芯片;步骤二,将所述第一半成品芯片进行有机清洗;步骤三,对清洗后的所述第一半成品芯片进行一道光刻,接着在所述p型gan外延层上形成mesa图案的掩膜,并进行icp刻蚀,以使所述p型gan外延层以及所述量子阱层被刻蚀掉,并露出所述n型gan外延层,形成mesa台阶,得到第二半成品芯片;步骤四,在所述第二半成品芯片上沉积一层透明导电薄膜,以使所述透明导电薄膜与所述p型gan外延层形成欧姆接触,并得到第三半成品芯片;步骤五,对所述第三半成品芯片进行一道光刻,使所述透明导电薄膜上形成一层tcl图案掩膜,并腐蚀掉所述第三半成品芯片上的所述n型gan外延层上方的透明导电薄膜,使所述n型gan外延层漏出,得到第四半成品芯片;步骤六,在所述第四半成品芯片上的所述透明导电薄膜表面进行一道pd1的光刻,以形成pd1的图案掩膜,所述pd1的图案掩膜为导电电极,通过金属蒸镀的方式在所述透明导电薄膜以及所述n型gan外延层表面形成一层导电金属膜层,接着对所述第四半成品芯片进行剥离,保留所述导电电极,得到第五半成品芯片;步骤七,在所述第五半成品芯片上的所述导电电极表面沉积一层电极支撑层,对所述电极支撑层进行光刻,并对所述光刻完成后的所述电极支撑层进行刻蚀,以使所述导电电极从所述电极支撑层上漏出,以得到第六半成品芯片;

步骤八,对所述第六半成品芯片进行一道pd2光刻,以形成pd2的图案掩膜,通过金属蒸镀的方式在所述电极支撑层表面蒸镀一层pd2打线电极金属,并对所述第六半成品芯片进行剥离,保留所述pd2打线电极金属,以使所述导电电极与所述pd2打线电极金属连通,并得到第七半成品芯片;步骤九,对所述第七半成品芯片上的所述pd2打线电极金属表面沉积一层pv2保护层,并对所述pv2保护层进行光刻,并对光刻完成后的所述第七半成品芯片进行icp刻蚀,以使所述pd2打线电极金属漏出,得到成品芯片。

6.与现有技术相比,本发明的有益效果是:通过在第四半成品芯片上的透明导电薄膜上进行一道光刻,形成pd1的图案掩膜,并且pd1的图案掩膜具体为导电电极,pd1的图案掩膜相比于常规图案掩膜较小,且由于导电电极只起到欧姆接触的作用,并且pd1的图案掩膜相比于常规图案掩膜较小,因此可以有效的防止金属迁移,并通过在第五半成品芯片上沉积电极支撑层,电极支撑层不仅能够起到绝缘保护的作用,也可以对导电电极的金属迁移进行进一步的抑制,从而提升该芯片的可靠性。

7.进一步的,在所述步骤三中,所述一道光刻依次包括涂胶、曝光、显影以及烘烤,所述涂胶具体为在所述第一半成品芯片表面旋涂一层厚度为2.5um-10um的光刻胶,所述曝光具体为将所述涂胶完成后的所述第一半成品芯片放入曝光机进行曝光,所述曝光的能量为150mj-1000mj,所述显影具体为对曝光完成后的所述第一半成品芯片通过显隐液进行显影,所述显影时间为50s-250s,所述烘烤的温度为120℃,所述烘烤时间为120s。

8.进一步的,在所述步骤三中,所述icp刻蚀的过程当中的温度为0℃-5℃,所述icp刻蚀过程中采用的刻蚀气体为cl2、bcl3以及cf4中的一种,刻蚀时间为100s-2000s。

9.进一步的,在所述步骤四中,通过磁控溅射沉积在所述第二半成品芯片上沉积一层所述透明导电薄膜,所述透明导电薄膜采用氧化铟锡制成,所述透明导电薄膜的厚度为200a-12000a,对沉积所述透明导电薄膜后的所述第二半成品芯片进行退火,所述退火的温度为550℃,所述退火的时间为3min。

10.进一步的,在所述步骤五中,将所述第三半成品芯片浸入盐酸和氯化铁的混合溶液中进行腐蚀,以使所述盐酸和氯化铁溶液腐蚀掉所述第三半成品芯片上的所述n型gan外延层上方的透明导电薄膜,所述腐蚀时间为180s。

11.进一步的,在所述步骤六中,采用负性光刻胶在所述第四半成品芯片上的所述透明导电薄膜上进行所述一道pd1的光刻。

12.进一步的,在所述步骤七中,通过化学气相沉积在所述第五半成品芯片上的所述导电电极表面沉积一层所述电极支撑层,所述电极支撑层由sio2制成,所述电极支撑层的厚度为8000a-20000a,所述刻蚀采用icp等离子体刻蚀。

13.进一步的,在所述步骤八中,在所述金属蒸镀之前,先进行抽真空,并使真空度达到1x10-2

托,接着通过蒸发对应金属靶材,以使金属蒸镀到所述第六半成品芯片表面,在所述金属蒸镀的过程中,镀率为0.1a/s-10a/s。

14.进一步的,在所述步骤九中,通过化学气相沉积在所述第七半成品芯片上的所述pd2打线电极金属表面沉积一层所述pv2保护层,所述pv2保护层采用sio2制成,所述pv2保护层的厚度为3000a-8000a。

15.进一步的,所述导电电极以及所述pd2打线电极金属均采用cr、al、ti、pt、ni、au以

及cu中的一种制成。

附图说明

16.图1为本发明第一实施例中的正装led芯片的制备方法流程图。

17.如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

18.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的若干实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

19.需要说明的是,当元件被称为“固设于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

20.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

21.实施例一请参阅图1所示为本发明第一实施例中的正装led芯片制备方法,所述制备方法具体包括步骤一至步骤九:步骤一,提供一衬底,并在所述衬底上依次生长n型gan外延层、量子阱层以及p型gan外延层,以得到第一半成品芯片;在具体实施时,衬底采用蓝宝石衬底,在蓝宝石衬底上依次生长n型gan外延层、量子阱层以及p型gan外延层,从而得到第一半成品芯片。

22.步骤二,将所述第一半成品芯片进行有机清洗;在具体实施时,将第一半成品芯片进行有机清洗,以清除第一半成品芯片在生长n型gan外延层、量子阱层以及p型gan外延层的过程中以及转运过程中的其上附着的有机物,达到清除第一半成品芯片上的有机物的目的。

23.步骤三,对清洗后的所述第一半成品芯片进行一道光刻,接着在所述p型gan外延层上形成mesa图案的掩膜,并进行icp刻蚀,以使所述p型gan外延层以及所述量子阱层被刻蚀掉,并露出所述n型gan外延层,形成mesa台阶,得到第二半成品芯片;在具体实施时,一道光刻依次包括涂胶、曝光、显影以及烘烤,涂胶具体为在第一半成品芯片表面旋涂一层厚度为2.5um-10um的光刻胶,在本实施例中,光刻胶的厚度为3um,曝光具体为将涂胶完成后的第一半成品芯片放入曝光机进行曝光,曝光的能量为15mj-1000mj,显影具体为对曝光完成后的第一半成品芯片通过显隐液进行显影,显影时间为50s-250s,在本实施例中,曝光的能量为200mj,曝光时间为80s,所述烘烤的温度为120℃,所述烘烤时间为120s, icp刻蚀的过程当中的温度为0℃-5℃,采用的刻蚀气体为cl2、bcl3以及cf4中的一种,刻蚀时间为100s-2000s,在本实施例中,刻蚀过程当中的温度为0℃,

采用的刻蚀气体为cl2,刻蚀时间为900s。

24.需要解释的是,经过一道光刻之后的第一半成品芯片在其上的p型gan外延层上形成mesa特殊图案的掩膜,在icp刻蚀的过程中,刻蚀掉部分p型gan外延层以及量子阱层,以达到露出n型gan外延层的目的,并且在刻蚀过程中,刻蚀掉露出的p型gan外延层,刻蚀掉的p型gan外延层的厚度为1um,从而形成mesa台阶,值得说明的是,在形成mesa台阶之后,对第一半成品芯片进行去胶,得到第二半成品芯片。

25.步骤四,在所述第二半成品芯片上沉积一层透明导电薄膜,以使所述透明导电薄膜与所述p型gan外延层形成欧姆接触,并得到第三半成品芯片;在具体实施时,在第二半成品外延片上通过磁控溅射沉积一层透明导电薄膜,透明导电薄膜采用氧化铟锡制成,透明导电薄膜的厚度为200a-12000a,在本实施例中,透明导电薄膜的厚度为200a,值得说明的是,第二半成品芯片上在沉积透明导电薄膜后,需要进行退火,退火的温度为550℃,退火的时间为3min,从而使得透明导电薄膜与p型gan外延层形成欧姆接触。

26.步骤五,对所述第三半成品芯片进行一道光刻,使所述透明导电薄膜上形成一层tcl图案掩膜,并腐蚀掉所述第三半成品芯片上的所述n型gan外延层上方的透明导电薄膜,使所述n型gan外延层漏出,得到第四半成品芯片;在具体实施时,将第三半成品芯片浸入盐酸和氯化铁的混合溶液中进行腐蚀,以使盐酸和氯化铁溶液腐蚀掉第三半成品芯片上的n型gan外延层上方的透明导电薄膜,使得第三半成品芯片上的n型gan外延层的部分不被透明导电薄膜遮挡,漏出n型gan外延层,因为有tcl图案掩膜的保护可使透明导电薄膜腐蚀成预设的图案,在本实施例中,腐蚀的时间为180s。

27.值得说明的是,在腐蚀完成漏出n型gan外延层之后,需要对第三半成品芯片进行去胶,得到第四半成品芯片。

28.步骤六,在所述第四半成品芯片上的所述透明导电薄膜表面进行一道pd1的光刻,以形成pd1的图案掩膜,所述pd1的图案掩膜为导电电极,通过金属蒸镀的方式在所述透明导电薄膜以及所述n型gan外延层表面形成一层导电金属膜层,接着对所述第四半成品芯片进行剥离,保留所述导电电极,得到第五半成品芯片;在具体实施时,采用负性光刻胶在第四半成品芯片上的透明导电薄膜上进行一道pd1的光刻,从而形成pd1的图案掩膜,在本实施例中pd1的图案掩膜较为特殊图案掩膜,相比于常规电极图案掩膜要小,因此pd1上的导电电极只起到欧姆接触作用,电极小距离较远,可以有效的防止金属迁移,值得说明的是,在光刻完成后,对第四半成品芯片进行离子清洗,将第四半成品芯片上剩余的残渣清除,清洗完成后再将第四半成品芯片进行水洗和甩干,达到对第四半成品芯片的清洁,清洁完成后,通过金属蒸镀的方式在透明导电薄膜和n型gan外延层表面形成一层导电金属膜层,在本实施例中,金属蒸镀完成后,对第四半成品芯片进行剥离,将光刻胶以及不需要的金属剥离出去,使得第四半成品芯片上的透明导电薄膜以及n型gan外延层的表面只留下pd1的图案掩膜以及pd1的图案掩膜上的导电电极。

29.值得说明的是,导电电极采用cr、al、ti、pt、ni、au以及cu中的一种制成。

30.步骤七,在所述第五半成品芯片上的所述导电电极表面沉积一层电极支撑层,对所述电极支撑层进行光刻,并对所述光刻完成后的所述电极支撑层进行刻蚀,以使所述导

电电极从所述电极支撑层上漏出,以得到第六半成品芯片;在具体实施时,在第五半成品芯片上通过化学气相沉积的方式在导电电极的表面沉积一层电极支撑层,电极支撑层由sio2制成,所述电极支撑层的厚度为8000a-20000a,在本实施例中,电极支撑层的厚度为8000a,在本实施例中,所述刻蚀采用icp等离子体刻蚀。

31.值得说明的是,电极支撑层刻蚀完成后,对第五半成品芯片进行去胶,得到第六半成品芯片。

32.步骤八,对所述第六半成品芯片进行一道pd2光刻,以形成pd2的图案掩膜,通过金属蒸镀的方式在所述电极支撑层表面蒸镀一层pd2打线电极金属,并对所述第六半成品芯片进行剥离,保留所述pd2打线电极金属,以使所述导电电极与所述pd2打线电极金属连通,并得到第七半成品芯片;在具体实施时,对第六半成品芯片进行一道pd2光刻,从而形成pd2的图案掩膜,pd2的图案掩膜为特殊图案掩膜,在一道pd2光刻完成后,对第六半成品芯片进行离子清洗以及水洗,值得说明的是,在金属蒸镀前,先进行抽真空,并使真空度达到1x10-2

托,接着通过蒸发对应金属靶材,以使金属蒸镀到第六半成品芯片表面,在金属蒸镀的过程中,镀率为0.1a/s-10a/s,在本实施例中,镀率为0.1a/s,蒸镀完成后进行剥离,只保留pd2的图案掩膜,也就是只保留特殊图案掩膜的pd2打线电极金属,从而使得导电电极与pd2打线电极金属连通,可正常实现led芯片正负极的导电点亮。

33.值得说明的是,pd2打线电极金属采用cr、al、ti、pt、ni、au以及cu中的一种制成。

34.步骤九,对所述第七半成品芯片上的所述pd2打线电极金属表面沉积一层pv2保护层,并对所述pv2保护层进行光刻,并对光刻完成后的所述第七半成品芯片进行icp刻蚀,以使所述pd2打线电极金属漏出,得到成品芯片。

35.在具体实施时,通过化学气相沉积在第七半成品芯片上的pd2打线电极金属表面沉积一层pv2保护层,pv2保护层采用sio2制成,pv2保护层的厚度为3000a-8000a,在本实施例中,pv2保护层3000a,pv2保护层可以有效的防止水汽入侵led芯片内,避免造成led芯片的失效,在通过化学气相沉积后也可以对金属迁移的现象进行进一步遏制,光刻完成后进行icp刻蚀,使漏出来的部分pd2打线电极金属用于后续封装时的打线工艺,并实现led芯片的正常点亮。

36.值得说明的是,得到成品芯片后,对成品芯片进行研磨,以达到减薄衬底,以使成品芯片的厚度减薄至50um,并对减薄后的成品芯片进行蒸镀dbr工艺,以使成品芯片的背面发出的光能够从正面反射出去。

37.综上,本发明上述实施例当中的正装led芯片制备方法,通过在透明导电薄膜上形成pd1的图案掩模,pd1的图案掩模具体为导电电极,由于pd1的图案掩模相比于常规的电极图案掩模较小,并且导电电极只起到欧姆接触的作用,电极小距离远,从而可以有效的防止金属迁移,并且导电电极用于导电,不用为后续打线操作进行考虑,从而不用考虑电极的大小,可以做大尽可能变相增大电极之间的距离,并且p型gan外延层和n型gan外延层上的导电电极也可以相距较远,可以更好的抑制金属迁移,并且在导电电极上沉积一层电极支撑层,电极支撑层不仅能够起到绝缘保护的作用,还可以对导电电极的金属迁移进行进一步抑制,从而提高该芯片的可靠性。

38.实施例二

本发明第二实施例中的正装led芯片制备方法,本实施例当中的正装led芯片制备方法与第一实施例当中的led芯片的制备方法的不同之处在于:步骤三,对清洗后的所述第一半成品芯片进行一道光刻,接着在所述p型gan外延层上形成mesa图案的掩膜,并进行icp刻蚀,以使所述p型gan外延层以及所述量子阱层被刻蚀掉,并露出所述n型gan外延层,形成mesa台阶,得到第二半成品芯片;在本实施例中,一道光刻中的旋涂光刻胶的厚度为6um,一道光刻中的曝光,曝光能量为600mj,一道光刻中的显影时间为150s,icp刻蚀的过程当中的温度为3℃,采用的刻蚀气体为bcl3,刻蚀时间为1500s。

39.需要解释的是,通过将旋涂的光刻胶的厚度控制在6um,以使光刻胶的厚度影响led芯片制备的过程中,并且本实施例当中的曝光能量可以有效的对第一半成品芯片进行曝光。

40.步骤四,在所述第二半成品芯片上沉积一层透明导电薄膜,以使所述透明导电薄膜与所述p型gan外延层形成欧姆接触,并得到第三半成品芯片;在本实施例中,透明导电薄膜的厚度为6000a。

41.需要解释的是,透明导电薄膜的厚度可以有效的起到导电的作用,并且将透明导电薄膜的厚度设置为6000a,以保证透明导电薄膜的质量。

42.步骤七,在所述第五半成品芯片上的所述导电电极表面沉积一层电极支撑层,对所述电极支撑层进行光刻,并对所述光刻完成后的所述电极支撑层进行刻蚀,以使所述导电电极从所述电极支撑层上漏出,以得到第六半成品芯片;在本实施例中,电极支撑层的厚度为14000a。

43.步骤八,对所述第六半成品芯片进行一道pd2光刻,以形成pd2的图案掩膜,通过金属蒸镀的方式在所述电极支撑层表面蒸镀一层pd2打线电极金属,并对所述第六半成品芯片进行剥离,保留所述pd2打线电极金属,以使所述导电电极与所述pd2打线电极金属连通,并得到第七半成品芯片;在本实施例中,金属蒸镀的镀率为5a/s。

44.步骤九,对所述第七半成品芯片上的所述pd2打线电极金属表面沉积一层pv2保护层,并对所述pv2保护层进行光刻,并对光刻完成后的所述第七半成品芯片进行icp刻蚀,以使所述pd2打线电极金属漏出,得到成品芯片;在本实施例中,pv2保护层的厚度为5000a,以使pv2保护层能够更加有效的防止水汽入侵led芯片内。

45.实施例三本发明第三实施例中的正装led芯片制备方法,本实施例当中的正装led芯片制备方法与第一实施例与第二实施例当中的led芯片的制备方法的不同之处在于:步骤三,对清洗后的所述第一半成品芯片进行一道光刻,接着在所述p型gan外延层上形成mesa图案的掩膜,并进行icp刻蚀,以使所述p型gan外延层以及所述量子阱层被刻蚀掉,并露出所述n型gan外延层,形成mesa台阶,得到第二半成品芯片;在本实施例中,一道光刻中的旋涂光刻胶的厚度为10um,一道光刻中的曝光,曝光能量为1000mj,一道光刻中的显影时间为250s,icp刻蚀的过程当中的温度为5℃,采用的刻蚀气体为cf4,刻蚀时间为2000s。

46.需要解释的是,通过将旋涂的光刻胶的厚度设置为10um,以使光刻胶的厚度影响led芯片制备的过程中,并且本实施例当中的曝光能量可以有效的对第一半成品芯片进行曝光。

47.步骤四,在所述第二半成品芯片上沉积一层透明导电薄膜,以使所述透明导电薄膜与所述p型gan外延层形成欧姆接触,并得到第三半成品芯片;在本实施例中,透明导电薄膜的厚度为12000a。

48.需要解释的是,透明导电薄膜的厚度可以有效的起到导电的作用,并且将透明导电薄膜的厚度设置为12000a,以保证透明导电薄膜的质量,并且不会影响透明导电薄膜的导电性。

49.步骤七,在所述第五半成品芯片上的所述导电电极表面沉积一层电极支撑层,对所述电极支撑层进行光刻,并对所述光刻完成后的所述电极支撑层进行刻蚀,以使所述导电电极从所述电极支撑层上漏出,以得到第六半成品芯片;在本实施例中,电极支撑层的厚度为20000a。

50.步骤八,对所述第六半成品芯片进行一道pd2光刻,以形成pd2的图案掩膜,通过金属蒸镀的方式在所述电极支撑层表面蒸镀一层pd2打线电极金属,并对所述第六半成品芯片进行剥离,保留所述pd2打线电极金属,以使所述导电电极与所述pd2打线电极金属连通,并得到第七半成品芯片;在本实施例中,金属蒸镀的镀率为10a/s。

51.步骤九,对所述第七半成品芯片上的所述pd2打线电极金属表面沉积一层pv2保护层,并对所述pv2保护层进行光刻,并对光刻完成后的所述第七半成品芯片进行icp刻蚀,以使所述pd2打线电极金属漏出,得到成品芯片;在本实施例中,pv2保护层的厚度为8000a,以使pv2保护层能够更加有效的防止水汽入侵led芯片内。

52.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

53.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1