一种双极型晶体管结构及其制作方法与流程

本发明属于半导体制造领域,涉及一种双极型晶体管结构及其制作方法。

背景技术:

1、随着新能源汽车、智能电网、移动通讯等产业的飞速发展,大电流的高压开关电路越来越受到重视,目前的电子开关元件包括双极型晶体管(bipolar junctiontransistor,简称103bjt)、绝缘栅型双极晶体管(igbt)以及场效应晶体管(mosfet),与另外两种开关元件相比,bjt由于耐冲击性好,故障率低以及成本较低而应用广泛。为了获得较大的电流增益,bjt需要具备以下特性:(1)发射区掺杂浓度较高(多子数量大);(2)基区掺杂浓度较低(复合电流小),宽度较薄(复合电流小);(3)集电区面积较大,掺杂浓度低。在共发射极输出特性状态下,随着vce的继续增大,集电结反偏电压随之持续增大,使得集电结的势垒区(空间电荷区)宽度越来越大,基区的尺寸越来越小,基区的少子也就是从发射极过来的多子的浓度梯度会增加,从而增加了电流,当集电结反偏电压到达一个极限时,集电结电流急剧上升,导致集电结发生击穿,因此,请参阅图1,显示为一种双极结型晶体管的内部结构示意图,其中,图1中b代表基极、c代表集电极、e代表发射极,该双极型晶体管中包括基区101、集电区102及发射区103,受限于基区101的宽度和掺杂浓度限制,该双极型晶体管在大电流下容易发生集电结击穿,即在基极浮空的情况下,击穿电压较低,容易对开关电路造成损坏。

2、因此,如何提供一种双极型晶体管结构及其制作方法,以实现pnp管在施加集电结反偏电压产生的大电流下能够稳定工作而不会发生集电极击穿,防止造成电路损坏,成为本领域技术人员亟待解决的一个重要技术问题。

3、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种双极型晶体管结构,用于解决现有技术中双极管受限于及躯干宽度和掺杂浓度限制导致的双极型晶体管在大电流下容易发生集电极击穿的问题。

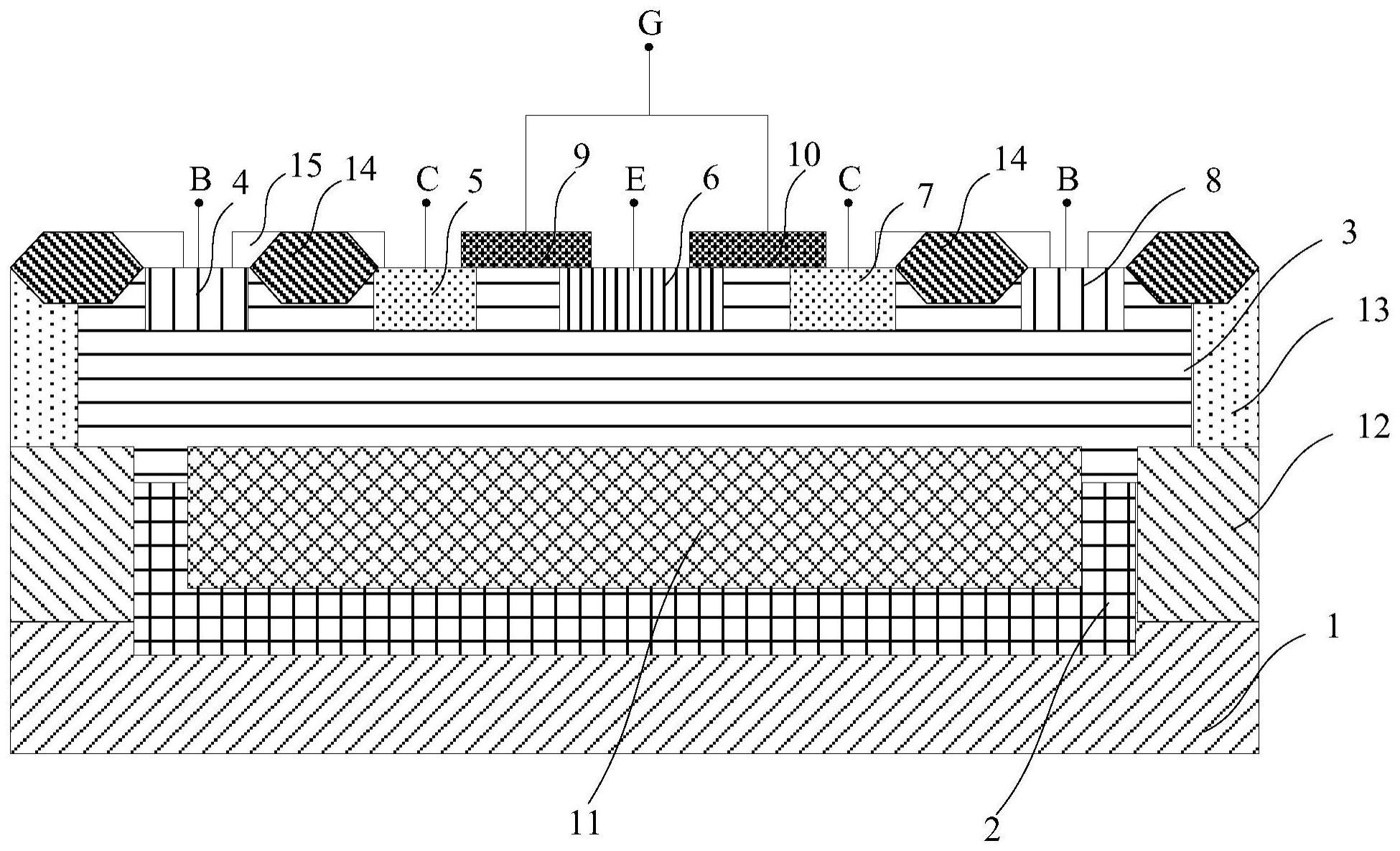

2、为实现上述目的及其他相关目的,本发明提供一种双极型晶体管结构,包括:

3、p型衬底;

4、深n阱,位于所述p型衬底中;

5、n型外延层,位于所述p型衬底上方;

6、电极引出端注入区,位于所述n型外延层中,所述电极引出端注入区包括在水平方向上依次间隔排列的第一基极引出端注入区、第一集电极引出端注入区、发射极引出端注入区、第二集电极引出端注入区及第二基极引出端注入区;

7、第一栅极结构及第二栅极结构,位于所述n型外延层上方,所述第一栅极结构横跨于所述第一集电极引出端注入区与所述发射极引出端注入区之间,所述第二栅极结构横跨于所述发射极引出端注入区与所述第二集电极引出端注入区之间;

8、电极引出端,包括基极引出端、集电极电极引出端、发射极电极引出端及栅极引出端,所述基极引出端与所述第一基极引出端注入区及所述第二基极引出端注入区电连接,所述集电极引出端与所述第一集电极引出端注入区及所述第二集电极引出端注入区电连接,所述发射极引出端与所述发射极引出端注入区电连接,所述栅极引出端与所述第一栅极结构及所述第二栅极结构电连接。

9、可选地,还包括n型埋层及p型埋层,所述n型埋层位于所述深n阱中,所述p型埋层位于所述p型衬底中与所述深n阱邻接。

10、可选地,所述n型埋层的掺杂浓度范围是8e17 cm-3~2e18 cm-3,所述p型埋层的掺杂浓度范围是8e17 cm-3~2e18 cm-3。

11、可选地,还包括第一隔离结构,所述第一隔离结构位于所述n型外延层中。

12、可选地,所述第一隔离结构包括深沟槽隔离结构。

13、可选地,还包括第二隔离结构,所述第二隔离结构位于所述n型外延层的上表层,所述第一基极引出端注入区与所述第一集电极引出端注入区之间通过所述第二隔离结构实现电隔离,所述第二基极引出端注入区与所述第二集电极引出端注入区之间通过所述第二隔离结构实现电隔离。

14、可选地,所述第二隔离结构包括locos隔离及sti隔离中的至少一种。

15、可选地,所述p型衬底的掺杂浓度范围是1e15 cm-3~3e15 cm-3,所述n型外延层的掺杂浓度范围是1e18 cm-3~5e18 cm-3,所述深n阱的掺杂浓度范围是8e16 cm-3~2e17 cm-3,所述基极引出端注入区的掺杂浓度范围是8e19 cm-3~2e20 cm-3,所述集电极引出端注入区的掺杂浓度范围是8e19 cm-3~2e20 cm-3,所述发射极引出端注入区的掺杂浓度范围是8e19 cm-3~2e20cm-3。

16、

17、

18、可选地,所述第一栅极结构包括第一栅介质层,所述第二栅极结构包括第二栅介质层,所述第一栅介质层的厚度大于3nm,所述第二栅介质层的厚度大于3nm。

19、本发明还一种双极型晶体管结构的制作方法,包括以下步骤:

20、提供一p型衬底;

21、形成深n阱于所述p型衬底中;

22、形成n型外延层于所述p型衬底上方;

23、形成电极引出端注入区于所述n型外延层中,所述电极引出端注入区包括在水平方向上依次间隔排列的第一基极引出端注入区、第一集电极引出端注入区、发射极引出端注入区、第二集电极引出端注入区及第二基极引出端注入区;

24、形成第一栅极结构及第二栅极结构于所述n型外延层上方,所述第一栅极结构横跨于所述第一集电极引出端注入区与所述发射极引出端注入区之间,所述第二栅极结构横跨于所述发射极引出端注入区与所述第二集电极引出端注入区之间;

25、形成电极引出端,包括基极引出端、集电极电极引出端、发射极电极引出端及栅极引出端,所述基极引出端与所述第一基极引出端注入区及所述第二基极引出端注入区电连接,所述集电极引出端与所述第一集电极引出端注入区及所述第二集电极引出端注入区电连接,所述发射极引出端与所述发射极引出端注入区电连接,所述栅极引出端与所述第一栅极结构及所述第二栅极结构电连接。

26、如上所述,本发明的双极型晶体管结构,通过在发射区与集电区之间增加栅极,用以调控横向pnp基区的电势,形成其与发射区、集电区构成的并联mos管,通过周期性施加栅极端的电压,可以形成正反馈,使pnp管在大电流下能够稳定工作并且不会发生击穿现象造成pnp管损坏,甚至造成开关电路损坏的现象,并且,本发明的双极型晶体管结构通过将基区隔离以形成局部浮体结构,减少大电流工作条件下衬底漏电情况的发生,提高器件工作时的性能稳定性。

技术特征:

1.一种双极型晶体管结构,其特征在于,包括:

2.根据权利要求1所述的双极型晶体管结构,其特征在于:还包括n型埋层及p型埋层,所述n型埋层位于所述深n阱中,所述p型埋层位于所述p型衬底中与所述深n阱邻接。

3.根据权利要求2所述的双极型晶体管结构,其特征在于:所述n型埋层的掺杂浓度范围是8e17 cm-3~2e18 cm-3,所述p型埋层的掺杂浓度范围是8e17 cm-3~2e18 cm-3。

4.根据权利要求1所述的双极型晶体管结构,其特征在于:还包括第一隔离结构,所述第一隔离结构位于所述n型外延层中。

5.根据权利要求4所述的双极型晶体管结构,其特征在于:所述第一隔离结构包括深沟槽隔离结构。

6.根据权利要求1所述的双极型晶体管结构,其特征在于:还包括第二隔离结构,所述第二隔离结构位于所述n型外延层的上表层,所述第一基极引出端注入区与所述第一集电极引出端注入区之间通过所述第二隔离结构实现电隔离,所述第二基极引出端注入区与所述第二集电极引出端注入区之间通过所述第二隔离结构实现电隔离。

7.根据权利要求6所述的双极型晶体管结构,其特征在于:所述第二隔离结构包括locos隔离及sti隔离中的至少一种。

8.根据权利要求1所述的双极型晶体管结构,其特征在于:所述p型衬底的掺杂浓度范围是1e15 cm-3~3e15 cm-3,所述n型外延层的掺杂浓度范围是1e18 cm-3~5e18 cm-3,所述深n阱的掺杂浓度范围是8e16 cm-3~2e17 cm-3,所述基极引出端注入区的掺杂浓度范围是8e19cm-3~2e20 cm-3,所述集电极引出端注入区的掺杂浓度范围是8e19 cm-3~2e20 cm-3,所述发射极引出端注入区的掺杂浓度范围是8e19 cm-3~2e20 cm-3。

9.根据权利要求1所述的双极型晶体管结构,其特征在于:所述第一栅极结构包括第一栅介质层,所述第二栅极结构包括第二栅介质层,所述第一栅介质层的厚度大于3nm,所述第二栅介质层的厚度大于3nm。

10.一种双极型晶体管结构的制作方法,其特征在于,包括以下步骤:

技术总结

本发明提供一种双极型晶体管结构及制作方法,包括P型衬底、深N阱、N型外延层、电极引出端注入区、栅极结构以及电极引出端,电极引出端注入区包括依次间隔排列的第一基极引出端注入区、第一集电极引出端注入区、发射极引出端注入区、第二集电极引出端注入区及第二基极引出端注入区,第一栅极结构横跨第一集电极引出端注入区与发射极引出端注入区,第二栅极结构横跨发射极引出端注入区与第二集电极引出端注入区。本发明的双极型晶体管通过在发射区与集电区之间增加栅极以调控横向PNP基区的电势,形成其与发射区、集电区构成的并联MOS管,通过周期性施加栅极端的电压,可以形成正反馈,使PNP管在大电流下稳定工作且不会发生击穿现象。

技术研发人员:刘尧,刘海彬,刘筱伟,陈达伟,舒刚剑,刘森

受保护的技术使用者:微龛(广州)半导体有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!