半导体器件的制备方法与流程

本发明属于半导体集成电路设计及制造领域,特别是涉及一种半导体器件的制备方法。

背景技术:

1、目前,主流的功率半导体器件(电力电子器件)依然以硅材料为主,但是硅材料耐击穿电压低,以及设计、工艺上已经到达其材料极限,成为制约其发展的主要问题。以sic、gan为代表的第三代半导体(又称宽禁带半导体)在功率半导体领域逐渐渗透到电动汽车、电源、消费类电子等行业中,实现了部分对硅基材料的替代,在小型化、低功耗、高频率等方面均有优异表现。

2、当前,gan功率器件主要有肖特基势垒二极管(schottky barrier diode,sbd),高电子迁移率晶体管(high electron mobility transistor,hemt)及金属氧化物半导体场效应晶体管(metal oxide semiconductor field effect transistor,mosfet)等。gan功率器件,比如hemt,的一大特点是具有二维电子气沟道(2dimension electron gas,2deg),使得其通常为常开型器件,而实际应用需求常关型器件。为实现常关性器件,提出了沟槽栅、氟离子注入栅及p型栅等结构。在这些结构中,沟槽栅的实现最简单,故而应用较广泛。现有沟槽栅的实现方法有三种:1)势垒层全去除;2)去除部分势垒层;3)选择性生长。在方法1)中,势垒层全去除可以获得具有较大阈值电压的功率器件,但势垒层全去除过程容易损伤沟道层,增大导通电阻,且清洗过程中引入的附着于栅极底部的杂质作为缺陷中心,在器件工作过程中吸附电荷,降低器件的工作频率并导致电流崩塌效应。在方法2)中,去除部分势垒层的过程不会损伤沟道层,但很难精确控制势垒层的去除深度,使得去除深度不一致,不同器件的阈值电压不一致,产生阈值电压漂移效应。在方法3)中,涉及到掩膜层的沉积及去除,同样会引入的附着于栅极底部的杂质作为缺陷中心,在器件工作过程中吸附电荷,降低器件的工作频率并导致电流崩塌效应。

3、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种半导体器件的制备方法,用于解决现有技术中栅极的制备过程中容易产生缺陷或/及阈值电压漂移的问题。

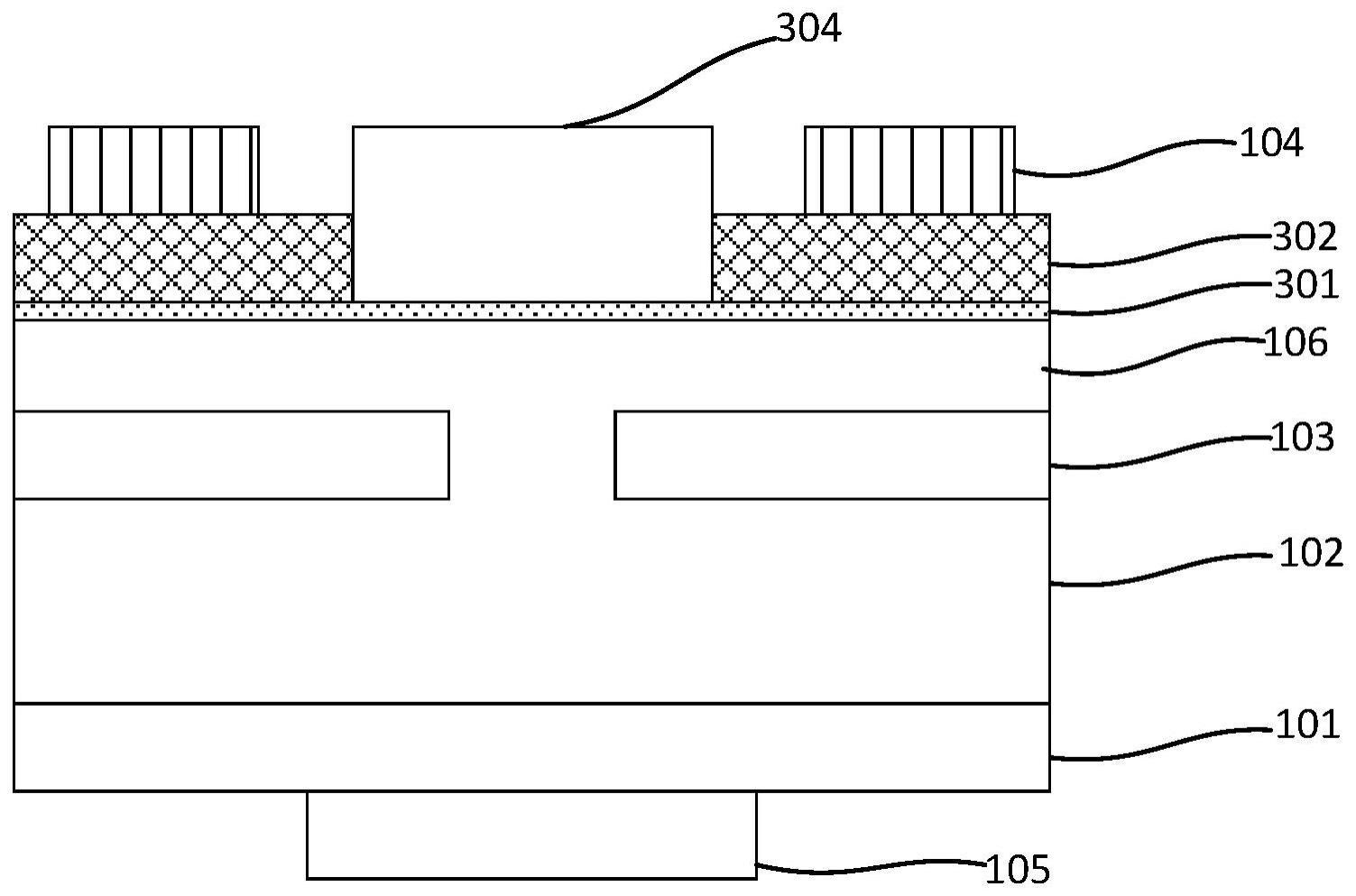

2、为实现上述目的及其他相关目的,本发明提供一种半导体器件的制备方法,所述制备方法包括:1)提供一半导体结构;2)在所述半导体结构上形成底部势垒层;3)在所述底部势垒层上形成顶部势垒层,所述顶部势垒层形成有栅极槽,所述栅极槽显露所述底部势垒层的顶面;4)在所述栅极槽中形成栅极结构。

3、可选地,步骤2)通过原子层沉积工艺在所述半导体结构上形成底部势垒层,所述底部势垒层的厚度为1纳米~5纳米。

4、可选地,所述底部势垒层包括氮化物薄膜,所述氮化物薄膜包括aln、algan、alingan、inn、ingan、及inaln中的一种。

5、可选地,步骤3)包括:3-1)在所述底部势垒层上形成生长阻挡层,所述生长阻挡层与栅极槽区域对应设置;3-2)通过金属有机物化学气相沉积工艺或原子层沉积工艺在所述底部势垒层上沉积顶部势垒层;3-2)去除所述生长阻挡层,以形成栅极槽。

6、可选地,步骤3)包括:3-1)通过金属有机物化学气相沉积工艺或原子层沉积工艺在所述底部势垒层上沉积顶部势垒层;3-2)通过光刻工艺和刻蚀工艺在所述顶部势垒层中形成栅极结构,所述底部势垒层和所述顶部势垒层设置为不同的材料,所述刻蚀停留在所述底部势垒层的顶面。

7、可选地,所述顶部势垒层包括氮化物薄膜,所述氮化物薄膜包括aln、algan、alingan和inaln中的一种。

8、可选地,所述半导体器件为电流孔径垂直电子晶体管,所述半导体结构包括:衬底;漂移层,形成于所述衬底上;电流阻挡层,设置于所述漂移层中,所述电流阻挡层中设有电流孔,所述电流孔用于限定电流路径;沟道层,设置于所述电流阻挡层之上;所述栅极对应设置于所述电流孔上方;所述半导体器件还包括:漏极,设置于所述衬底底面;源极,设置于所述顶部势垒层上,且设置于所述栅极结构外围。

9、可选地,所述衬底包括n型重掺杂gan层,所述漂移层包括n型轻掺杂gan层。

10、可选地,所述半导体器件为高电子迁移率晶体管,所述半导体结构包括:衬底;沟道层,设置于所述衬底上,所述底部势垒层设置于所述沟道层上,所述沟道层包括二维电子气沟道;所述半导体器还包括:源极和漏极,分别设置于所述栅极结构的两侧。

11、可选地,所述沟道层包括本征gan,所述gan沟道层和所述底部势垒层之间形成二维电子气沟道。

12、可选地,所述栅极结构包括p型gan层和设置于所述p型gan层上的金属栅,所述p型gan层进一步耗尽下方的所述gan沟道层和所述底部势垒层之间的二维电子气,以形成常关型的晶体管。

13、可选地,所述栅极结构包括设置于所述底部势垒层之上并与其肖特基接触的金属栅,所述金属栅耗尽下方的所述gan沟道层和所述底部势垒层之间的二维电子气,以形成常关型的晶体管。

14、如上所述,本发明的半导体器件的制备方法,具有以下有益效果:

15、本发明通过底部势垒层保护沟道层,一方面可以有效避免在清洗或刻蚀过程中在沟道层表面引入杂质,保证沟道层的质量,降低器件的导通电阻并保证导通电流的稳定性;另一方面本发明可以有效避免常规势垒层全去除方法损伤沟道层,降低沟道层的缺陷;又一方面本发明可以有效避免常规势垒层部分去除方法使得蚀刻深度不一致并难以精确控制的缺陷,本发明通过原子层沉积工艺形成超薄底部势垒层,可以精确控制沟槽栅深度,使得器件的保持阈值电压一致。

技术特征:

1.一种半导体器件的制备方法,其特征在于,所述制备方法包括:

2.根据权利要求1所述的半导体器件的制备方法,其特征在于:步骤2)通过原子层沉积工艺在所述半导体结构上形成底部势垒层,所述底部势垒层的厚度为1纳米~5纳米。

3.根据权利要求2所述的半导体器件的制备方法,其特征在于:所述底部势垒层包括氮化物薄膜,所述氮化物薄膜包括aln、algan、alingan、inn、ingan及inaln中的一种。

4.根据权利要求1所述的半导体器件的制备方法,其特征在于:步骤3)包括:

5.根据权利要求1所述的半导体器件的制备方法,其特征在于:步骤3)包括:

6.根据权利要求4或5所述的半导体器件的制备方法,其特征在于:所述顶部势垒层包括氮化物薄膜,所述氮化物薄膜包括aln、algan、alingan和inaln中的一种。

7.根据权利要求1所述的半导体器件的制备方法,其特征在于:所述半导体器件为电流孔径垂直电子晶体管,所述半导体结构包括:

8.根据权利要求7所述的半导体器件的制备方法,其特征在于:所述衬底包括n型重掺杂gan层,所述漂移层包括n型轻掺杂gan层。

9.根据权利要求1所述的半导体器件的制备方法,其特征在于:所述半导体器件为高电子迁移率晶体管,所述半导体结构包括:

10.根据权利要求9所述的半导体器件的制备方法,其特征在于:所述沟道层包括gan本征gan,所述gan沟道层和所述底部势垒层之间形成二维电子气沟道。

11.根据权利要求7或9所述的半导体器件的制备方法,其特征在于:所述栅极结构包括p型gan层和设置于所述p型gan层上的金属栅,所述p型gan层耗尽下方的所述沟道层和所述底部势垒层之间的二维电子气,以形成常关型的高电子迁移率晶体管。

12.根据权利要求7或9所述的半导体器件的制备方法,其特征在于:所述栅极结构包括设置于所述底部势垒层之上并与其肖特基接触的金属栅,所述金属栅耗尽下方的所述沟道层和所述底部势垒层之间的二维电子气,以形成常关型的高电子迁移率晶体管。

技术总结

本发明提供一种半导体器件的制备方法,包括步骤:1)提供一半导体结构;2)在半导体结构上形成底部势垒层;3)在底部势垒层上形成顶部势垒层,顶部势垒层形成有栅极槽,栅极槽显露底部势垒层的顶面;4)在栅极槽中形成栅极结构。本发明通过底部势垒层保护沟道层,一方面可以有效避免在清洗或刻蚀过程中在沟道层中引入杂质,保证沟道层的质量;另一方面本发明可以有效避免常规势垒层全去除方法损伤沟道层,降低沟道层的缺陷;又一方面本发明可以有效避免常规势垒层部分去除方法使得蚀刻深度不一致并难以精确控制的缺陷,本发明通过原子层沉积工艺形成超薄底部势垒层,可以精确控制沟槽栅深度,使得器件的保持阈值电压一致。

技术研发人员:卢敬权,殷淑仪

受保护的技术使用者:东莞市中镓半导体科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!