半导体器件、堆叠式复合沟槽结构的制作方法与流程

本发明涉及半导体制造,特别是涉及一种半导体器件、堆叠式复合沟槽结构的制作方法。

背景技术:

1、随着技术发展,纵向工艺技术在半导体制造中越来越受到关注。如图1所示,目前,平面mosfet(金属氧化物半导体场效应管)的工艺技术已经较为成熟,在14nm以下工艺中,鱼鳍mosfet(finfet)的工艺技术被广泛应用,gaafet(gate-all-around fet,全环绕栅极晶体管)也得到了深入研究。从平面mosfet到finfet、gaafet,是工艺技术从平面到纵向的一个发展过程。

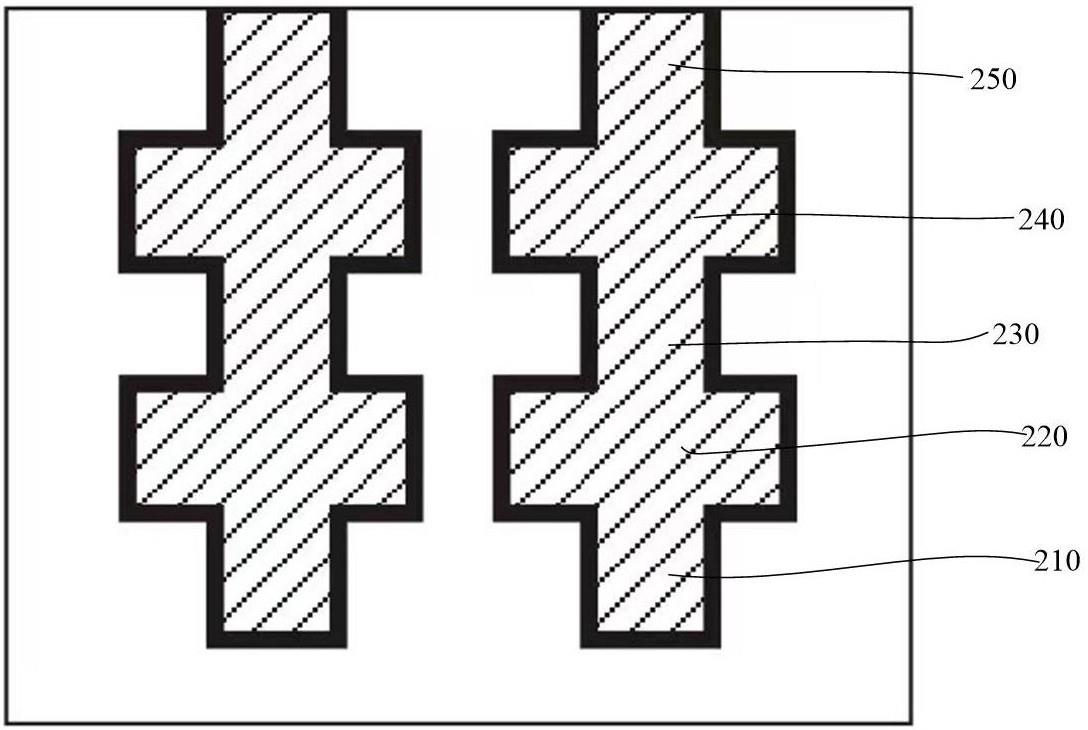

2、沟槽技术在半导体制造工艺中被广泛使用,例如浅沟槽隔离(sti)、深沟槽隔离(dti)、沟槽mos管的制造等均采用了沟槽技术。图2示出了一种堆叠式复合沟槽结构,其包括多级沟槽结构。该结构的工艺实现有利于纵向结构器件如gaafet等的制造。

3、传统的沟槽蚀刻工艺,无论是浅沟槽还是深沟槽,皆是沟槽顶部宽度与底部宽度相近,或底部宽度稍微大于顶部宽度,难以实现图2中堆叠式复合沟槽的结构。

技术实现思路

1、基于此,有必要提供一种能够实现上述堆叠式复合沟槽结构的制作方法,以及提供具有该堆叠式复合沟槽结构的半导体器件。

2、本发明的一个目的是提供一种半导体器件中堆叠式复合沟槽结构的制作方法,方案如下:

3、一种半导体器件中堆叠式复合沟槽结构的制作方法,其特征在于,所述堆叠式复合沟槽结构包括多级沟槽结构,所述制作方法是逐级进行沟槽结构的制作;

4、第一级沟槽结构的制作步骤包括:

5、获取基底;

6、在所述基底上制作第一级的沟槽;

7、在第一级的沟槽中填充形成第一级的半导体层;

8、第n级沟槽结构的制作步骤包括:

9、在第n-1级沟槽结构的基础上生长第n级的外延层;

10、在第n级的外延层上制作第n级的沟槽,第n级的沟槽贯穿所述外延层至露出第n-1级的半导体层,第n级的沟槽的宽度不同于第n-1级的沟槽的宽度;

11、在第n级的沟槽中填充形成第n级的半导体层;

12、其中,n为大于等于2的整数。

13、在其中一个实施例中,各级沟槽结构的制作步骤还包括:

14、在制作本级的沟槽之前,在所述基底或者本级的外延层上制作本级的第一热氧化层;

15、本级的沟槽贯穿本级的第一热氧化层至所述基底或者本级的外延层中。

16、在其中一个实施例中,各级沟槽结构的制作步骤还包括:

17、在形成本级的半导体层之后,清除本级的第一热氧化层。

18、在其中一个实施例中,各级沟槽结构的制作步骤还包括:

19、在制作本级的沟槽之后,且在形成本级的半导体层之前,在本级的沟槽的内壁制作本级的第二热氧化层。

20、在其中一个实施例中,各级的半导体层的材料独立地选自非掺杂多晶硅、杂质掺杂多晶硅中的至少一种。

21、在其中一个实施例中,各级沟槽结构的制作步骤还包括:

22、对本级的半导体层进行杂质离子注入。

23、在其中一个实施例中,各级的外延层的厚度为0.5μm~10μm。

24、在其中一个实施例中,各级的半导体层以同一对称轴呈轴对称。

25、在其中一个实施例中,奇数级的沟槽具有相同宽度,偶数级的沟槽具有相同宽度。

26、本发明的另一个目的是提供一种半导体器件,方案如下:

27、一种半导体器件,具有堆叠式复合沟槽结构,所述堆叠式复合沟槽结构是通过上述任一实施例所述的制作方法制作得到。

28、与现有方案相比,上述半导体器件、堆叠式复合沟槽结构的制作方法具有以下有益效果:

29、上述堆叠式复合沟槽结构的制作方法将堆叠式复合沟槽结构按照多级沟槽结构逐级进行制作,在第一级沟槽结构制作时,先在基底上制作沟槽,在沟槽中填充形成半导体层,随后各级沟槽结构制作时,先在前一级的沟槽结构的基础上生外延层,再在外延层上制作露出前一级的半导体层的沟槽,并且,前后两级中沟槽的宽度不同,然后在沟槽中填充形成半导体层,如此逐级形成堆叠的宽度变化的半导体层。上述制作方法能够通过常规工艺的组合制作得到堆叠式复合沟槽结构,工艺流程简单,材料选择范围更广。

30、上述半导体器件具有通过上述任一实施例所述的制作方法制作得到的堆叠式复合沟槽结构,因而能够获得相应的技术效果。

技术特征:

1.一种半导体器件中堆叠式复合沟槽结构的制作方法,其特征在于,所述堆叠式复合沟槽结构包括多级沟槽结构,所述制作方法是逐级进行沟槽结构的制作;

2.如权利要求1所述的制作方法,其特征在于,各级沟槽结构的制作步骤还包括:

3.如权利要求2所述的制作方法,其特征在于,各级沟槽结构的制作步骤还包括:

4.如权利要求1~3中任一项所述的制作方法,其特征在于,各级沟槽结构的制作步骤还包括:

5.如权利要求1~3中任一项所述的制作方法,其特征在于,各级的半导体层的材料独立地选择非掺杂多晶硅、杂质掺杂多晶硅中的至少一种。

6.如权利要求1~3中任一项所述的制作方法,其特征在于,各级沟槽结构的制作步骤还包括:

7.如权利要求1~3中任一项所述的制作方法,其特征在于,各级的外延层的厚度为0.5μm~10μm。

8.如权利要求1~3中任一项所述的制作方法,其特征在于,各级的半导体层以同一对称轴呈轴对称。

9.如权利要求8所述的制作方法,其特征在于,奇数级的沟槽具有相同宽度,偶数级的沟槽具有相同宽度。

10.一种半导体器件,其特征在于,具有堆叠式复合沟槽结构,所述堆叠式复合沟槽结构是通过如权利要求1~9中任一项所述的制作方法制作得到。

技术总结

本发明涉及一种半导体器件、堆叠式复合沟槽结构的制作方法。上述堆叠式复合沟槽结构的制作方法将堆叠式复合沟槽结构按照多级沟槽结构逐级进行制作,在第一级沟槽结构制作时,先在基底上制作沟槽,在沟槽中填充形成半导体层,随后各级沟槽结构制作时,先在前一级的沟槽结构的基础上生外延层,再在外延层上制作露出前一级的半导体层的沟槽,并且,前后两级中沟槽的宽度不同,然后在沟槽中填充形成半导体层,如此逐级形成堆叠的宽度变化的半导体层。上述制作方法能够通过常规工艺的组合制作得到堆叠式复合沟槽结构,工艺流程简单,材料选择范围更广。

技术研发人员:于绍欣

受保护的技术使用者:广州粤芯半导体技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!