半导体产品和用于生产半导体产品的方法与流程

本公开大体上涉及一种半导体产品。具体实施例涉及一种半导体产品、用于生产半导体产品的掩模、用于生产半导体产品的方法、和计算机程序。

背景技术:

1、碳化硅(sic)合并pin肖特基(mps)二极管对于开关电源应用显示出巨大的潜力。sic mps二极管通常包括在n型外延晶圆中的肖特基和p+注入区。考虑到碳化硅(sic)器件通常被设计为在高电压/电流条件下工作的事实,sic器件的可靠性值得器件设计者极大的关注。因为高电流脉冲在电器设备启动时或者在意外电路故障期间是常见的,所以浪涌电流能力(其代表功率器件在高电流脉冲下的可靠性)是器件耐用性(ruggedness)的关键参数之一。

2、sic mps二极管结合了在额定电流下的低正向电压降和高浪涌电流能力的优点。在浪涌事件期间,通常由于铝焊盘熔化,器件内会产生并耗散大量的热量,从而导致结温度的升高并最终导致器件故障。因此,提高mps二极管的浪涌能力的要点是限制结温度升高。这将通过优化制造工艺、结构和布局设计来实现,以降低浪涌过程期间的正向电压降,并因此减少所产生的热量。

3、浪涌现象的物理机制和提高浪涌能力的器件设计方法论仍然是关于sic mps二极管的一些主要研究课题。现成可用的大多数二极管或者文献中公开的大多数二极管表现出较差或者相当有限的浪涌电流能力性能。

4、图1(现有技术)中示出了现有技术的sic mps二极管的一个示例,并且其参考了rupp等人的proceedings of the 26th internationalsymposium on powersemiconductor devices&ic’s,2014,hawaii。在该图中,灰色“实心”六边形是p单元区,并且蜂窝框架限定了嵌入在n区中的p条状区。右侧宽的区域是二极管的终止区。包含六边形和蜂窝框架的左侧区域是有源区。具有这种布局的二极管被认为具有最先进的浪涌电流能力性能。图1以x、y、z参考系的俯视平面图示出了一个示例,其中肖特基二极管(深色的“空”六边形)和pn结(灰色的“实心”六边形)处于六边形形状的单元或点的形式。特别地,每个pn结元件(或等同地,每个p+岛状件)在单元的所有六个侧面上被相应的肖特基二极管完全包围。此外,每个肖特基二极管(在俯视图中)被p+区完全包围并通过p+区与相邻的肖特基二极管间隔开。所提出的设计使用不同大小的六边形。较大六边形中的相对边之间的距离在6μm至8μm的范围内,而较小六边形中的相对边之间的距离在3μm至4μm的范围内。较大的六边形通过较薄(约1μm宽)的p+条带彼此连接,该较薄的p+条带具有宽度约为1μm的蜂窝框架形状。较小的六边形通过肖特基二极管与其它p+掺杂区完全隔离。

技术实现思路

1、根据本公开的至少一些实施例的目的是增强ifsm(正向浪涌电流能力)性能。

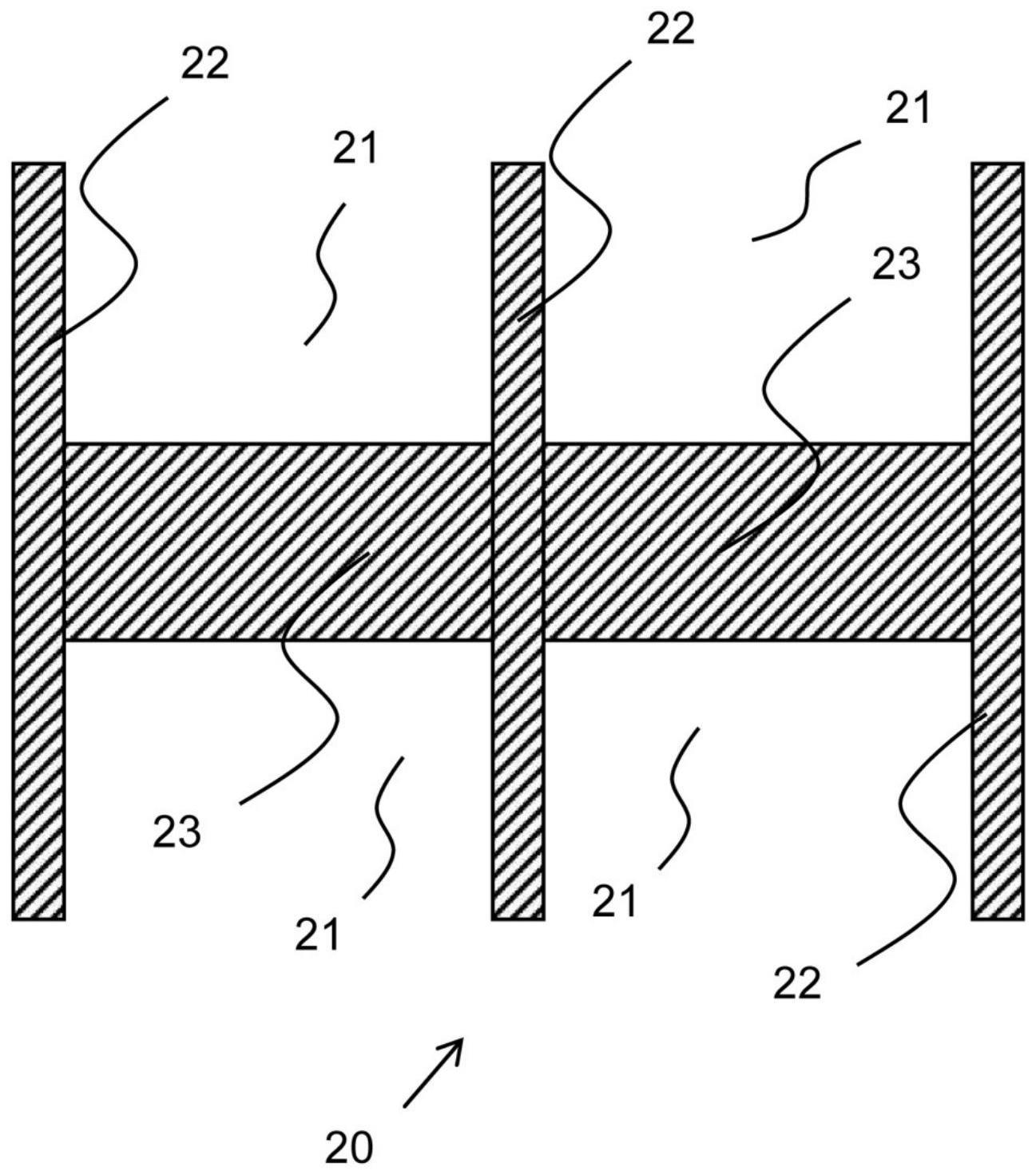

2、因此,在本公开的第一方面,提供了一种半导体产品。该半导体产品包括以下元件。掺杂有第一导电型的基部区。掺杂有第二导电类型的多个条状区,其设置在基部区的上表面上,其中第二导电类型不同于第一导电类型。掺杂有第二导电类型的多个单元区,其设置在基部区的上表面上。金属层,其布置在基部区的上表面上,使得金属层与基部区限定肖特基势垒,且金属层覆盖多个条状区和多个单元区。多个单元区中的大多数单元区中的每个单元区接触多个条状区中的至少一个相邻的条状区。

3、根据本公开的半导体产品至少部分基于发明人的见解,即,使多个单元区中的大多数单元区中的每个单元区接触多个条状区中的至少一个相邻的条状区,增强半导体产品的ifsm(正向浪涌电流能力)性能。这是因为相对大面积的单元区增加了pn结的面积,因此增加了它们附近肖特基电流分布的均匀性,允许它们在最低可能的正向电压值激活(由于电流效应),而条状区作为电流扩展(扩散)层,其是较薄的条带,以便补偿由于单元区和条状区周围的耗尽区引起的肖特基沟道的部分夹断而导致的肖特基面积的减小(结果是电压降的增加)。通过将各个单个单元区短路而产生的掺杂有第二导电类型的大的区域的产生提高了pn结在浪涌状态下增加双极电流的功能。在相对较大面积的单元区周围的肖特基电流分布的较高均匀性使得在早期电压(early voltage)下激活它们,从而增加二极管的浪涌电流能力。

4、换句话说,大多数或甚至所有的单元区接触至少一个相邻的条状区。在此上下文中,词语“大多数”可以被认为是指至少一半,优选地为至少三分之二,或更优选地为基本上全部。在该上下文中,“基本上全部”可以被认为是指半导体器件的有源区中的全部或几乎全部相关元件,但是排除半导体器件的终端区中或附近的元件。要注意的是,即使在终端区中或附近的所述元件原则上可以符合条件,它们也可以被简单地忽略。

5、在此,条状区可以理解为一种区域,该区域是细长的狭窄的区段,其材料与相邻的部分、尤其与设有该区域的基部区不同。

6、优选地,多个条状区可以在相关文献中常规使用的意义上互相交叉,即,作为交替的细长部分。在根据本公开的一些实施例中,条状区不需要平行——为了它们在本公开的上下文中的适当操作,表征条状区的相关参数是它们各自的宽度和它们彼此之间的距离。当然,优选具有相互平行的条状区,因为这更容易实现,并且相信与相互平行的条状区相比,其它布置几乎没有益处或没有益处。

7、要注意的是,金属层被布置在基部区的上表面上,使得金属层与基部区限定肖特基势垒,并且金属层覆盖多个条状区和多个单元区。换句话说,金属层形成用于多个条状区和多个单元区的导电覆盖层,确保这些区可以被电短路。在一些实施例中,金属层可以在不同位置处具有不同的金属成分,例如,在暴露于金属层的基部区的上表面部分的顶上的第一金属成分和在条状区和单元区的顶上的不同的第二金属成分。当然,作为选择,可以使用均匀的金属成分。

8、在一些实施例中,多个单元区中的大多数单元区中的每个单元区接触多个条状区中的至少两个相邻的条状区。

9、在一些实施例中,多个单元区中的每个单元区接触多个条状区中的至少一个相邻的条状区。

10、在一些实施例中,多个单元区中的每个单元区接触多个条状区中的至少两个相邻的条状区。

11、在一些实施方案中,多个单元区中的各个单元区与多个单元区中的至少一些其它单元区对准。

12、在一些实施例中,多个单元区中的各个单元区与多个单元区中的至少一些其它单元区交错。

13、在此上下文中,交错可被认为意味着以各种之字形位置、交替位置或重叠位置中的任一者布置。

14、在一些实施例中,多个条状区从半导体产品的一端延伸到半导体产品的另一端。

15、在一些实施例中,多个条状区和多个单元区延伸到基部区中的相应深度是不同的。

16、在一些实施例中,半导体产品是合并pin肖特基(mps)碳化硅(sic)二极管。当然,根据本公开的实施例的基本原理可应用于以其它半导体材料生产的所有种类的mps二极管。

17、在一些实施例中,基部区是n掺杂的,并且其中多个条状区和多个单元区是p掺杂的。

18、另外,在本公开的第二方面中,提供了一种用于生产根据上述实施例中的任一个的半导体产品的掩模。

19、本领域技术人员将理解,应用于根据本公开的半导体产品的实施例的特征和考虑事项也可以在作必要的修正后应用于根据本公开的掩模的实施例。

20、另外,在本公开的第三方面中,提供了一种用于生产半导体产品的方法。该方法包括以下步骤。布置掺杂有第一导电类型的基部区。在基部区的上表面上设置掺杂有不同于第一导电类型的第二导电类型的多个条状区。在基部区的上表面上设置掺杂有第二导电类型的多个单元区。在基部区的上表面上布置金属层,使得金属层与基部区限定肖特基势垒,且金属层覆盖多个条状区和多个单元区。这些步骤以这样的方式执行,使得多个单元区中的大多数单元区中的每个单元区接触多个条状区中的至少一个相邻的条状区。

21、本领域技术人员将理解,应用于根据本公开的半导体产品的实施例的特征和考虑事项在作必要的修正后也可以应用于根据本公开的方法的实施例。

22、在一些实施例中,多个单元区中的大多数单元区中的每个单元区接触多个条状区中的至少两个相邻的条状区。

23、在一些实施例中,多个单元区中的每个单元区接触多个条状区中的至少一个相邻的条状区。

24、在一些实施例中,多个单元区中的每个单元区接触多个条状区中的至少两个相邻的条状区。

25、在一些实施方案中,多个单元区中的各个单元区与多个单元区中的至少一些其它单元区对准。

26、在一些实施例中,多个单元区中的各个单元区与多个单元区中的至少一些其它单元区交错。

27、另外,在本发明的第四方面,提供了一种包括指令的计算机程序,该指令被配置用于当由光刻设备的处理器执行时,使得光刻设备执行根据本发明的方法的上述实施例中的任何一个的步骤。

28、本领域技术人员将理解,应用于根据本公开的半导体产品的实施例的特征和考虑事项也可以在作必要的修正后应用于根据本公开的计算机程序的实施例。

- 还没有人留言评论。精彩留言会获得点赞!