具有双侧冷却的功率模块封装的制作方法

本发明涉及损耗大量功率的集成电路的紧凑封装,且特定来说,涉及多功能装置。

背景技术:

1、一些集成电路具有无引线封装,例如将集成电路物理且电耦合到印刷电路板的四方扁平无引线(qfn)及双扁平无引线(dfn)装置。扁平无引线装置(也被称为微引线框(mlf)及小轮廓无引线(son)装置)是基于将集成电路连接到印刷电路板的表面而无需印刷电路板中的穿孔的表面安装技术。在一些实例中,扁平无引线封装是通常使用平面铜引线框衬底制造的准芯片级塑料囊封封装。封装上的周边凸面(land)提供与印刷电路板的电耦合。所述凸面用作接触件且可被称为集成电路内部的引线;然而,引线并未延伸超过集成电路封装的边界。

2、一些集成电路及其它电子装置具有耦合到所述电路及装置内的电子组件的导电夹片。所述夹片可处于一个平面上,且所述电路及装置的引线或接触件可处于第二平面上。夹片被焊接到引线或以其它方式被电及/或机械接合到引线。

技术实现思路

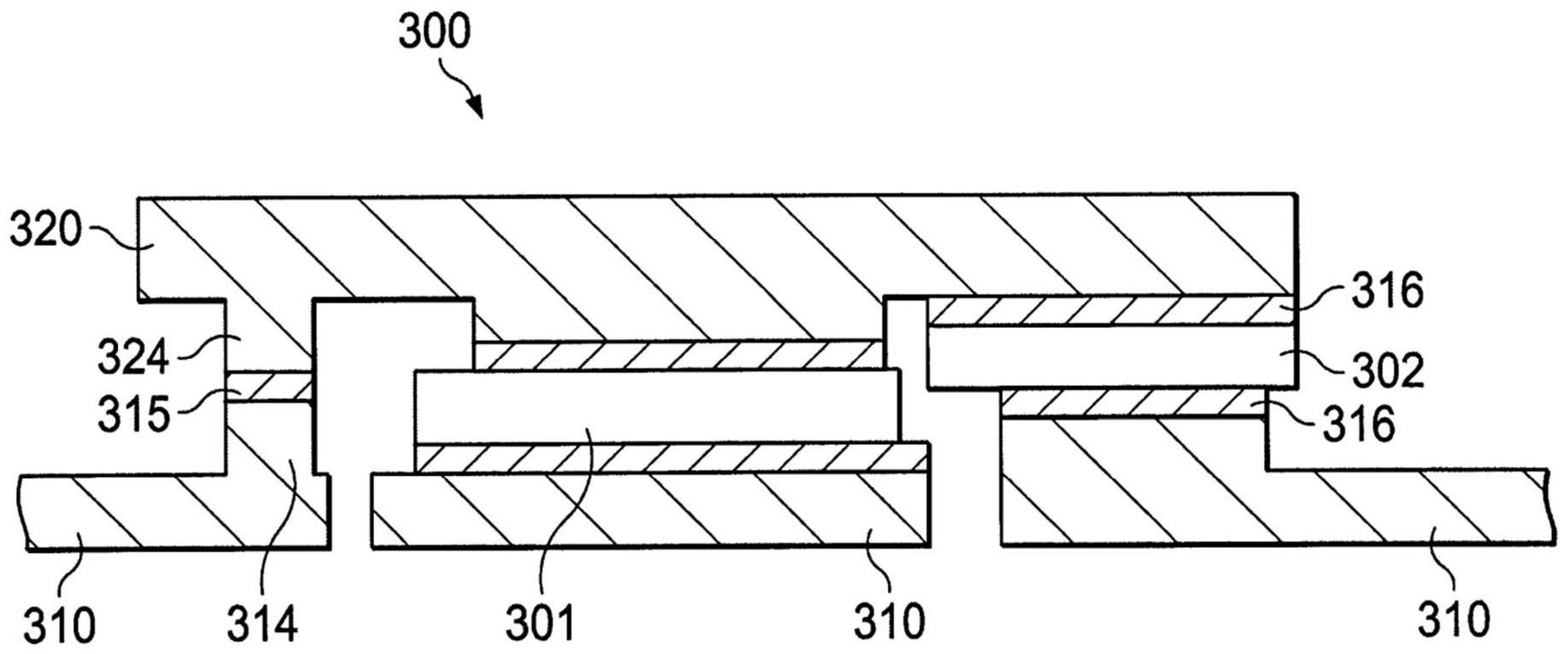

1、本发明中描述的标的物的一个新颖方面可被实施于一种多芯片封装中,所述多芯片封装包括:第一半导体装置,其被安装于第一引线框上,其中所述第一半导体装置的主要产热表面朝向所述第一引线框的散热区域定向且接触所述散热区域;第二半导体装置,其被安装于第二引线框上,其中所述第二半导体装置的主要产热表面朝向所述第二引线框的散热区域定向且接触所述散热区域;其中所述第一引线框是与突出接触区域共面的经蚀刻的引线框,且所述第二引线框是与接触所述第一引线框上的对应突出接触区域的突出接触区域共面的经蚀刻的引线框;且其中所述第一引线框的所述散热区域的表面被暴露于所述多芯片封装的第一侧上,且所述第二引线框的所述散热区域的表面被暴露于所述多芯片封装的与所述第一侧相对的第二侧上。

2、本发明中描述的标的物的另一新颖方面可被实施于一种用于制造多芯片封装的方法中,所述方法包括:通过蚀刻导电材料片材制造具有散热区域的上引线框及具有散热区域的下引线框;将第一芯片的第一侧附接到所述下引线框的所述散热区域;将第二芯片的第一侧附接到所述上引线框的所述散热区域;将所述上引线框叠加于所述下引线框上方,使得所述第一芯片的第二侧被附接到所述第二引线框的所述散热区域且所述第二芯片的第二侧被附接到所述第一引线框的所述散热区域以形成组合件;及使用模制化合物囊封所述组合件,使得所述上引线框的所述散热区域的表面及所述下引线框的所述散热区域的表面被暴露。

3、本发明中描述的标的物的另一新颖方面可被实施于一种多芯片封装中,其包括:第一半导体装置,其被安装于第一引线框上,其中所述第一半导体装置的漏极区域朝向所述第一引线框的散热区域定向且接触所述散热区域,且其中所述第一半导体装置的源极区域朝向第二引线框定向且接触所述第二引线框;第二半导体装置,其被安装于所述第二引线框上,其中所述第二半导体装置的漏极区域朝向所述第二引线框的散热区域定向且接触所述散热区域,且其中所述第二半导体装置的源极区域朝向所述第一引线框定向且接触所述第一引线框;且其中所述第一引线框的所述散热区域的表面被暴露于所述多芯片封装的第一侧,且所述第二引线框的所述散热区域的表面被暴露于所述多芯片封装的与所述第一侧相对的第二侧。

技术特征:

1.一种用于制造多芯片封装的方法,所述方法包括:

2.根据权利要求1所述的用于制造多芯片封装的方法,其进一步包含使用模制材料囊封所述第一半导体装置及所述第二半导体装置,使得所述第一引线框的所述散热区域的所述散热表面的所述表面及所述第二引线框的所述散热区域的所述表面保持被暴露。

3.根据权利要求2所述的用于制造多芯片封装的方法,其进一步包含通过所述第一引线框及所述第二引线框将第三半导体装置互连到所述第一半导体装置及所述第二半导体装置,且使用所述模制材料囊封所述第三半导体装置。

4.根据权利要求2或3所述的用于制造多芯片封装的方法,其进一步包含将散热器连接到所述第二引线框的所述散热区域。

5.根据权利要求2或3所述的用于制造多芯片封装的方法,其进一步包含附接到所述第一引线框的所述散热区域的衬底。

6.根据权利要求4所述的用于制造多芯片封装的方法,其进一步包含附接到所述第一引线框的所述散热区域的衬底。

7.根据权利要求5或6所述的用于制造多芯片封装的方法,其中所述衬底为印刷电路板。

8.一种制造多芯片封装的方法,所述方法包括:

9.根据权利要求8所述的制造多芯片封装的方法,其进一步包含使用模制材料囊封所述第一半导体装置及所述第二半导体装置,使得所述第一引线框的所述散热区域的所述散热表面的所述表面及所述第二引线框的所述散热区域的所述表面保持被暴露。

10.根据权利要求9所述的制造多芯片封装的方法,其进一步包含通过所述第一引线框及所述第二引线框将第三半导体装置互连到所述第一半导体装置及所述第二半导体装置,且使用所述模制材料囊封所述第三半导体装置。

11.根据权利要求9或10所述的制造多芯片封装的方法,其进一步包含将散热器连接到所述第二引线框的所述散热区域。

12.根据权利要求9、10或11所述的制造多芯片封装的方法,其进一步包含附接到所述第一引线框的所述散热区域的衬底。

13.根据权利要求12所述的制造多芯片封装的方法,其中所述衬底为印刷电路板。

14.一种用于制造多芯片封装的方法,所述方法包括:

15.根据权利要求14所述的制造多芯片封装的方法,其中所述第一引线框是与突出接触区域共面的经刻蚀的引线框,且所述第二引线框是与接触所述第一引线框上的对应突出接触区域的突出接触区域共面的经刻蚀的引线框。

16.根据权利要求14所述的制造多芯片封装的方法,其中所述第一引线框是与突出接触区域共面的经冲压的引线框,且所述第二引线框是与接触所述第一引线框上的对应突出接触区域的突出接触区域共面的经冲压的引线框。

17.根据权利要求14所述的制造多芯片封装的方法,其进一步包含用模制材料囊封所述第一半导体装置及所述第二半导体装置,使得所述第一引线框的所述散热区域的所述散热表面的所述表面及所述第二引线框的所述散热区域的所述表面保持被暴露。

18.根据权利要求14所述的制造多芯片封装的方法,其进一步包含通过所述第一引线框及所述第二引线框将第三半导体装置互连到所述第一半导体装置及所述第二半导体装置。

19.根据权利要求14所述的制造多芯片封装的方法,其中所述第一半导体装置及所述第二半导体装置两者都是垂直功率mosfet(金属氧化物半导体场效应晶体管)装置。

20.根据权利要求17所述的制造多芯片封装的方法,其进一步包含附接到所述第一引线框的所述散热区域的衬底。

21.根据权利要求20所述的制造多芯片封装的方法,其中所述衬底为印刷电路板。

技术总结

本发明涉及具有双侧冷却的功率模块封装。多芯片封装包含安装在第一引线框(310)上的第一半导体装置(301),其中所述第一半导体装置的主要产热表面朝向所述第一引线框的散热区域(312)定向且接触所述散热区域(312)。第二半导体装置(302)被安装于第二引线框(320)上,其中所述第二半导体装置的主要产热表面朝向所述第二引线框的散热区域(322)定向且接触所述散热区域(322)。

技术研发人员:涩谷诚

受保护的技术使用者:德州仪器公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!