阵列基板和阵列基板的制备方法与流程

本技术涉及显示,尤其是涉及一种阵列基板和阵列基板的制备方法。

背景技术:

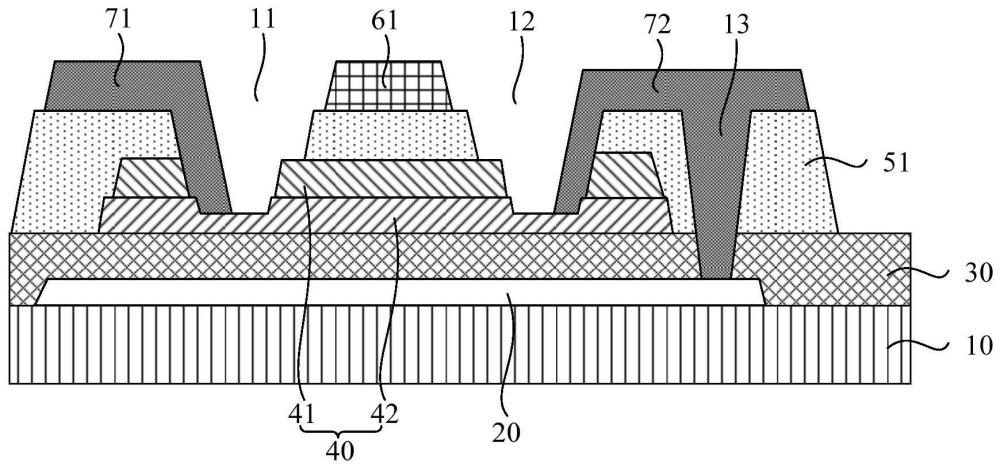

1、随着显示技术的发展,将igzo等金属氧化物半导体作为有源层材料应用于显示面板中已成为行业热门。现有技术中金属氧化物晶体管的结构如图1所示,包括层叠设置的衬底10、第一栅极21、第二缓冲层30、第一有源层40、栅极绝缘层51、第二栅极61、层间介质层52和源漏极层(图未示出),源漏极层与第一有源层40之间通过第一过孔11和第二过孔12连接,源漏极层与第一栅极21之间通过第三过孔13连接。

2、由于第三过孔13与其余两个过孔的深度不同,在当前的制备工艺中,各过孔主要通过分开刻蚀或半掩膜方式形成,半掩膜方式受设计规则限制,较难应用于高分辨率产品中,分开刻蚀方式为先对第三过孔13进行刻蚀,再对第一过孔11和第二过孔12进行刻蚀,此过程需要用到两道光罩,使得制作成本较高。如果可以用一道光罩同步刻蚀第一过孔11、第二过孔12和第三过孔13,则可以降低制作成本,但由于第三过孔13与其余两种过孔所需刻蚀的膜层厚度不同,同步刻蚀方式在第二缓冲层30的刻蚀时间内会使得第一有源层40出现过刻蚀情况,导致源漏极层与第一有源层40的接触电阻升高,开态电流降低,影响晶体管的稳定性。

3、因此,当前的阵列基板存在光罩数量减少和晶体管稳定性维持两者无法兼顾的技术问题,需要改进。

技术实现思路

1、本技术实施例提供一种阵列基板和阵列基板的制备方法,用以缓解现有阵列基板中光罩数量减少和晶体管稳定性维持两者无法兼顾的技术问题。

2、本技术实施例提供一种阵列基板,包括:

3、衬底;

4、第一金属层,形成在所述衬底一侧,所述第一金属层包括金属氧化物晶体管的第一栅极;

5、第二缓冲层,形成在所述第一金属层远离所述衬底的一侧;

6、金属氧化物半导体层,形成在所述第二缓冲层远离所述第一金属层的一侧,所述金属氧化物半导体层包括所述金属氧化物晶体管的第一有源层,所述第一有源层的迁移率大于阈值,且包括耐刻蚀材料;

7、绝缘层,形成在所述金属氧化物半导体层远离所述第二缓冲层的一侧;

8、源漏极层,形成在所述绝缘层远离所述金属氧化物半导体层的一侧,所述源漏极层包括所述金属氧化物晶体管的第一源极和第一漏极;

9、其中,所述绝缘层中形成第一过孔和第二过孔,所述第一源极和所述第一漏极分别通过所述第一过孔和所述第二过孔与所述第一有源层连接,所述绝缘层和所述第二缓冲层中共同形成第三过孔,所述第一源极和所述第一漏极中的其中一者通过所述第三过孔与所述第一栅极连接。

10、在一种实施例中,所述阵列基板还包括多晶硅层、第一缓冲层和第二金属层,所述多晶硅层形成在所述衬底一侧,包括低温多晶硅晶体管的第二有源层和信号走线,所述第一缓冲层形成在所述多晶硅层和所述第一金属层之间,所述第二金属层与所述源漏极层同层设置,所述第一金属层还包括所述低温多晶硅晶体管的第三栅极,所述第二金属层还包括金属氧化物晶体管的第二栅极和所述低温多晶硅晶体管的第四栅极,所述源漏极层还包括所述低温多晶硅晶体管的第二源极和第二漏极,所述绝缘层、所述第二缓冲层和所述第一缓冲层中共同形成第四过孔、第五过孔和第六过孔,所述第二源极和所述第二漏极分别通过所述第四过孔和所述第五过孔与所述第二有源层连接,所述第一源极和所述第一漏极中的另外一者通过所述第六过孔与所述信号走线连接。

11、在一种实施例中,所述第一有源层的材料为结晶金属氧化物半导体材料。

12、在一种实施例中,所述第一有源层包括层叠设置的第一子有源层和第二子有源层,所述第一子有源层的迁移率大于阈值,所述第二子有源层的材料为耐刻蚀材料。

13、在一种实施例中,所述第一有源层的材料为铟镓锌氧化物,所述第一子有源层和所述第二子有源层的材料满足以下条件中的至少一种:所述第一子有源层中铟含量大于所述第二子有源层中铟含量;所述第一子有源层中镓含量小于所述第二子有源层中镓含量;所述第二子有源层中掺杂锡且所述第一子有源层中未掺杂锡。

14、在一种实施例中,所述第二子有源层的厚度不小于所述第一子有源层的厚度。

15、本技术还提供一种阵列基板的制备方法,包括:

16、提供衬底;

17、在所述衬底上制备第一金属层,并对所述第一金属层图案化,形成金属氧化物晶体管的第一栅极,在所述第一金属层远离所述衬底的一侧制备第二缓冲层;

18、在所述第二缓冲层远离所述第一金属层的一侧制备金属氧化物半导体层,对所述金属氧化物半导体层图案化,形成所述金属氧化物晶体管的第一有源层,所述第一有源层的迁移率大于阈值,且包括耐刻蚀材料;

19、在所述金属氧化物半导体层远离所述第二缓冲层的一侧制备绝缘层,并同步刻蚀所述绝缘层和所述第二缓冲层,在所述绝缘层中单独形成第一过孔和第二过孔,在所述绝缘层和所述第二缓冲层共同形成第三过孔;

20、在所述绝缘层远离所述金属氧化物半导体层的一侧制备源漏极层,对所述源漏极层图案化形成所述金属氧化物晶体管的第一源极和第一漏极,所述第一源极和所述第一漏极分别通过所述第一过孔和所述第二过孔与所述第一有源层连接,所述第一源极和所述第一漏极中的其中一者通过所述第三过孔与所述第一栅极连接。

21、在一种实施例中,在所述衬底上制备第一金属层,并对所述第一金属层图案化的步骤,包括:

22、在所述衬底上制备多晶硅层,将所述多晶硅层图案化形成低温多晶硅晶体管的第二有源层和信号走线,在所述多晶硅层远离所述衬底的一侧制备第一缓冲层,在所述第一缓冲层远离所述多晶硅层的一侧制备第一金属层,并对所述第一金属层图案化,形成金属氧化物晶体管的第一栅极和低温多晶硅晶体管的第三栅极;

23、同步刻蚀所述绝缘层和所述第二缓冲层的步骤,包括:

24、同步刻蚀所述绝缘层、所述第二缓冲层和所述第一缓冲层,在所述绝缘层中单独形成第一过孔和第二过孔,在所述绝缘层和所述第二缓冲层共同形成第三过孔,在所述绝缘层、所述第二缓冲层和所述第一缓冲层中共同形成第四过孔、第五过孔和第六过孔;

25、在所述绝缘层远离所述金属氧化物半导体层的一侧制备源漏极层,对所述源漏极层图案化的步骤,包括:

26、在所述绝缘层远离所述金属氧化物半导体层的一侧制备同层的源漏极层和第二金属层,对所述第二金属层图案化,形成所述金属氧化物晶体管的第二栅极和所述低温多晶硅晶体管的第四栅极,同步对所述源漏极层图案化,形成所述金属氧化物晶体管的第一源极和第一漏极、以及所述低温多晶硅晶体管的第二源极和第二漏极,所述第一源极和所述第一漏极分别通过所述第一过孔和所述第二过孔与所述第一有源层连接,所述第二源极和所述第二漏极分别通过所述第四过孔和所述第五过孔与所述第二有源层连接,所述第一源极和所述第一漏极中的其中一者通过所述第三过孔与所述第一栅极连接,所述第一源极和所述第一漏极中的另外一者通过所述第六过孔与所述信号走线连接。

27、在一种实施例中,在所述第二缓冲层远离所述第一金属层的一侧制备金属氧化物半导体层,对所述金属氧化物半导体层图案化,形成所述金属氧化物晶体管的第一有源层的步骤,包括:

28、在所述第二缓冲层远离所述第一金属层的一侧制备金属氧化物半导体层,并图案化形成所述金属氧化物晶体管的第一有源层;

29、对所述第一有源层进行退火处理,得到结晶金属氧化物半导体材料。

30、在一种实施例中,在所述第二缓冲层远离所述第一金属层的一侧制备金属氧化物半导体层,对所述金属氧化物半导体层图案化,形成所述金属氧化物晶体管的第一有源层的步骤,包括:

31、在所述第二缓冲层远离所述第一金属层的一侧制备层叠的第一金属氧化物半导体层和第二金属氧化物半导体层,所述第一金属氧化物半导体层的迁移率大于阈值,所述第二金属氧化物半导体层的材料为耐刻蚀材料;

32、对所述第一金属氧化物半导体层和所述第二金属氧化物半导体层图案化,形成所述金属氧化物晶体管的第一子有源层和第二子有源层。

33、有益效果:本技术提供一种阵列基板和阵列基板的制备方法,阵列基板包括衬底、第一金属层、第二缓冲层、金属氧化物半导体层、绝缘层和源漏极层,第一金属层形成在所述衬底一侧,所述第一金属层包括金属氧化物晶体管的第一栅极,第二缓冲层形成在所述第一金属层远离所述衬底的一侧,金属氧化物半导体层形成在所述第二缓冲层远离所述第一金属层的一侧,所述金属氧化物半导体层包括所述金属氧化物晶体管的第一有源层,所述第一有源层的迁移率大于阈值,且包括耐刻蚀材料,绝缘层形成在所述金属氧化物半导体层远离所述第二缓冲层的一侧,源漏极层形成在所述绝缘层远离所述金属氧化物半导体层的一侧,所述源漏极层包括所述金属氧化物晶体管的第一源极和第一漏极,其中,所述绝缘层中形成第一过孔和第二过孔,所述第二源极和所述第二漏极分别通过所述第一过孔和所述第二过孔与所述第一有源层连接,所述绝缘层和所述第二缓冲层中共同形成第三过孔,所述第一源极和所述第一漏极中的其中一者通过所述第三过孔与所述第一栅极连接。本技术的阵列基板中,当采用同步刻蚀方式形成第一过孔、第二过孔和第三过孔时,由于第一有源层包括耐刻蚀材料,则发生过刻蚀的情况得到缓解,同时由于第一有源层的迁移率大于阈值,因此保证了金属氧化物晶体管的稳定性,即本技术的阵列基板可以实现减少光罩数量和维持晶体管稳定性的兼顾。

- 还没有人留言评论。精彩留言会获得点赞!