半导体封装方法及封装结构与流程

本申请涉及半导体封装,具体涉及一种半导体封装方法及封装结构。

背景技术:

1、芯片封装即半导体封装是一种将集成电路用绝缘的塑料或陶瓷材料打包的技术,是整个集成电路制造过程中的重要一环。芯片封装起到安放、固定、密封、保护芯片和增强散热性能的作用,可以隔绝外界污染及外力对芯片的破坏。

2、近年来半导体封装越来越趋于小型化,引线框架作为芯片封装结的一部分,也朝向小型化方向发展。一般的,引线框架包括基材及形成于基材中的基岛及管脚,基岛用于承载芯片,减少基岛的尺寸也是减小引线框架尺寸的一种方法。

3、在半导体封装工艺过程中,装片一般是使用粘合胶(例如导电胶)来将芯片装载并固定在引线框架的基岛上的过程,且传统工艺中多采用点胶或喷胶工艺实现装片过程。但对于小尺寸的基岛,由于基岛的尺寸仅是略大于芯片的尺寸(如芯片边界与基岛边界间的距离小于100um),因此在进行点胶或喷胶时粘合胶的胶量比较难控制,或胶量较少导致芯片与基岛结合力差,出现分层问题,或胶量较多导致粘合胶溢出基岛,出现桥接及粘附框架背面等问题,影响封装结构的可靠性或电性能。

4、因此,有必要提供改进的技术方案以克服现有技术中存在的以上技术问题。

技术实现思路

1、为了解决上述技术问题,本申请提供了一种半导体封装方法及封装结构,可以解决装片过程中的胶量控制问题,消除了胶量过多或过少对封装结构可靠性的不良影响。

2、根据本申请第一方面,提供了一种半导体封装方法,包括:

3、在引线框架的基岛表面涂设光刻胶;

4、在所述基岛表面涂设有所述光刻胶的位置贴装半导体芯片,并使多余的所述光刻胶溢出于所述半导体芯片外;

5、去除溢出于所述半导体芯片外的所述光刻胶;

6、对所述引线框架和所述半导体芯片进行电性耦接及塑封。

7、可选地,所述光刻胶为正性光刻胶。

8、可选地,去除溢出于所述半导体芯片外的所述光刻胶包括:

9、对贴装有所述半导体芯片的所述基岛表面进行曝光;

10、利用显影液溶解去除溢出于所述半导体芯片外的经曝光处理后的所述正性光刻胶。

11、可选地,所述光刻胶为负性光刻胶。

12、可选地,去除溢出于所述半导体芯片外的所述光刻胶包括:

13、利用显影液溶解去除溢出于所述半导体芯片外的未经曝光处理的所述负性光刻胶。

14、可选地,所述半导体芯片的第一表面贴装在所述基岛表面,且在所述引线框架的基岛表面涂设所述光刻胶时,设置涂设于所述基岛表面的所述光刻胶的表面尺寸大于所述第一表面的表面尺寸。

15、可选地,所述半导体芯片的第一表面贴装在所述基岛表面,且在所述引线框架的基岛表面涂设所述光刻胶时,设置涂设于所述基岛表面的所述光刻胶的体积大于所述第一表面的表面积与预定厚度的乘积。

16、可选地,所述半导体芯片的至少一个边界与所述基岛的对应边界之间的距离小于100um。

17、根据本申请第二方面,提供了一种半导体封装结构,包括:

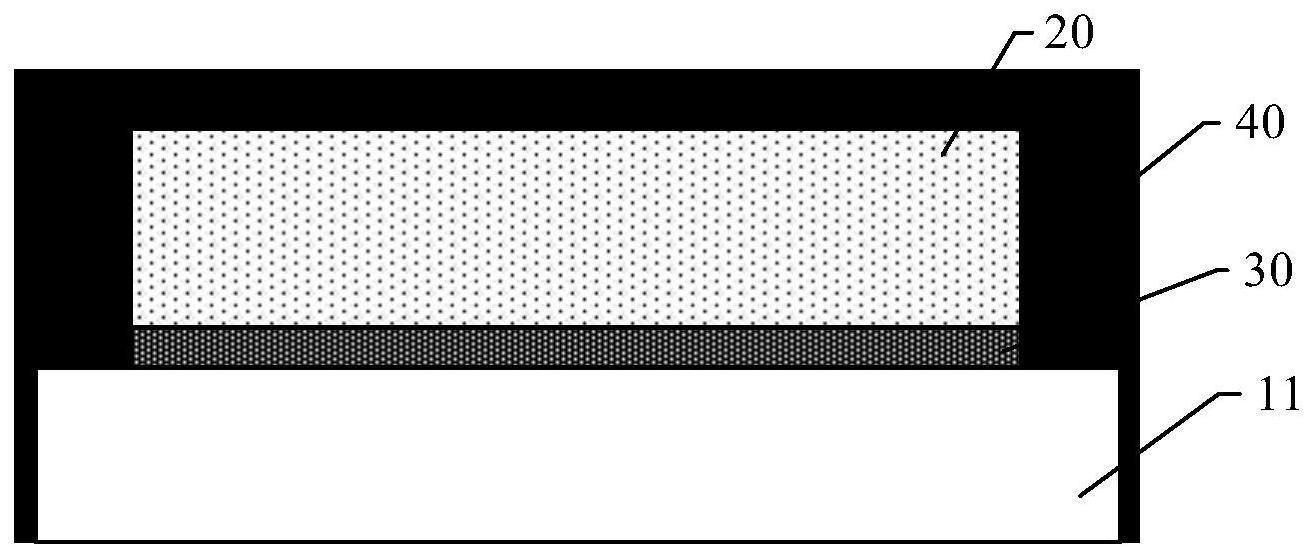

18、引线框架,包括基岛和与所述基岛隔离的多个引脚;

19、半导体芯片,通过光刻胶贴装在所述基岛表面,并与所述多个引脚电性耦接;

20、塑封体,封装所述引线框架和所述半导体芯片。

21、可选地,所述光刻胶为正性光刻胶或负性光刻胶。

22、可选地,所述半导体芯片的至少一个边界与所述基岛的对应边界之间的距离小于100um。

23、本申请技术方案的有益效果至少包括:

24、本申请实施例所提供的技术方案中,采用光刻胶来实现半导体芯片在基岛上的装片固定,相较于现有的装片方案,本申请在装片时可以通过涂设足量的光刻胶来确保半导体芯片与基岛之间的牢固结合,避免了分层问题,且对出胶量的精度要求更低,可以不必特意选用小的喷胶嘴,提高了生成效率;此外,基于光刻胶在一定条件可溶解的化学特性,使得光刻胶外溢于半导体芯片外的外溢部分也能够被轻易去除,解决了现有技术中因溢胶导致的发生桥接,粘附框架背面等问题,提高了封装结构的可靠性。

25、应当说明的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

技术特征:

1.一种半导体封装方法,其中,包括:

2.根据权利要求1所述的半导体封装方法,其中,所述光刻胶为正性光刻胶。

3.根据权利要求2所述的半导体封装方法,其中,去除溢出于所述半导体芯片外的所述光刻胶包括:

4.根据权利要求1所述的半导体封装方法,其中,所述光刻胶为负性光刻胶。

5.根据权利要求4所述的半导体封装方法,其中,去除溢出于所述半导体芯片外的所述光刻胶包括:

6.根据权利要求1-5中任一项所述的半导体封装方法,其中,所述半导体芯片的第一表面贴装在所述基岛表面,且在所述引线框架的基岛表面涂设所述光刻胶时,设置涂设于所述基岛表面的所述光刻胶的表面尺寸大于所述第一表面的表面尺寸。

7.根据权利要求1-5中任一项所述的半导体封装方法,其中,所述半导体芯片的第一表面贴装在所述基岛表面,且在所述引线框架的基岛表面涂设所述光刻胶时,设置涂设于所述基岛表面的所述光刻胶的体积大于所述第一表面的表面积与预定厚度的乘积。

8.根据权利要求1所述的半导体封装方法,其中,所述半导体芯片的至少一个边界与所述基岛的对应边界之间的距离小于100um。

9.一种半导体封装结构,其中,包括:

10.根据权利要求9所述的半导体封装结构,其中,所述光刻胶为正性光刻胶或负性光刻胶。

11.根据权利要求9所述的半导体封装结构,其中,所述半导体芯片的至少一个边界与所述基岛的对应边界之间的距离小于100um。

技术总结

本申请提供了一种半导体封装方法及封装结构,该封装方法包括:在引线框架的基岛表面涂设光刻胶;在基岛表面涂设有光刻胶的位置贴装半导体芯片,并使多余的光刻胶溢出于半导体芯片外;去除溢出于半导体芯片外的光刻胶;对引线框架和半导体芯片进行电性耦接及塑封。本申请解决了装片过程中的胶量控制问题,提高了封装结构的可靠性,且对出胶量的精度要求较低,也有利于提高生产效率。

技术研发人员:方航,涂正磊

受保护的技术使用者:杰华特微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!