一种LED垂直硅衬底外延片及其制备方法

本发明属于led领域,尤其涉及一种led垂直外延片及其制备方法。

背景技术:

1、随着led技术的发展、输出性能的提升、生产成本的降低,近年来也越来越受到半导体照明行业的关注。但是,目前在纳米图形化衬底模板、氮化物外延材料生长等过程中,由于外延层结构之间中存在着裂纹、晶格失配、内部残余应力,衬底和外延层之间存在着较大的晶格失配,而造成了晶体质量差等问题。特别是基于硅衬底的异质外延生长,由于硅衬底与异质外延层之间,存在着较大的晶格失配和热失配,使得外延片的成品率低。

2、相比于al2o3、sic或者gan衬底,si衬底由于具有价格低廉、大尺寸制备容易以及可与传统硅工艺相兼容的优势,是gan基hemt外延生长的首选衬底。但由于si(100)面原子不是六方对称排布,在si(100)衬底上外延生长高质量六方相氮化物薄膜极其困难,且gan外延层与硅衬底间存在大的晶格失配和热失配,使得生长出的gan外延层受到了极大的张应力,导致外延层中出现了高密度的裂纹、位错和衬底发生大的翘曲等现象。

技术实现思路

1、本发明提供了一种led垂直硅衬底外延片,用于解决现有技术中硅衬底的外延层结构之间中存在着裂纹、晶格失配、内部残余应力,衬底和外延层之间存在着较大的晶格失配,在外延层制备过程中温度的变化受到巨大张应力而导致外延片弯曲或者外延薄膜开裂,影响外延层的制备质量。

2、本发明所要解决的技术问题还在于,提供一种led垂直硅衬底外延片的制备方法,其工艺简单,能够稳定制得上述性能。良好的发光二极管外延片。

3、本发明的具体技术方案如下:

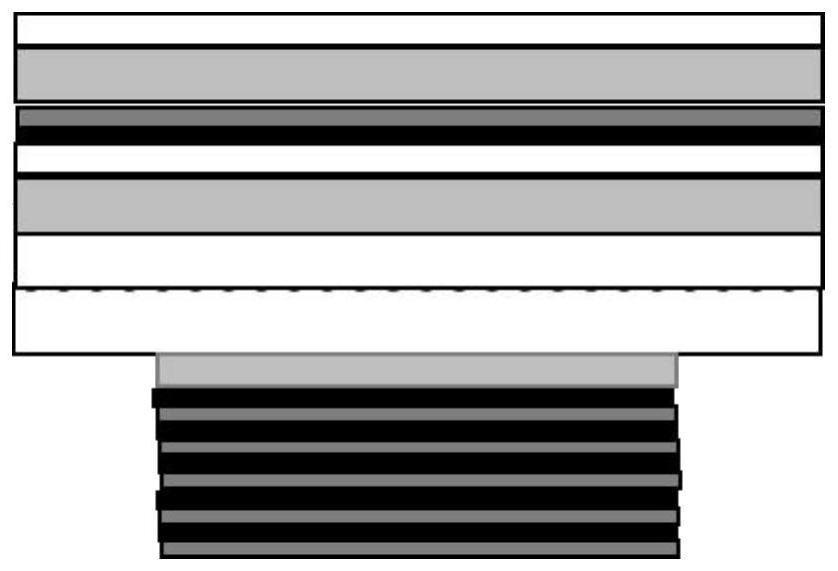

4、本发明提供了一种led垂直硅衬底外延片,包括依次层叠于所述硅衬底粗糙上表面制备外延层,所述外延层包含依次制备的缓冲层、本征gan层、n型gan层、多量子阱层、电子阻挡层、p型gan层,在所述硅衬底光滑下表面设置压应力支撑层,所述应力支撑层表面积小于衬底的表面积,分布在硅衬底中间;所述应力支撑层包含依次在硅衬底下表面制备的应力提供层和应力加强层。所述应力提供层为niznse层,所述应力加强层为alingan。

5、本发明中硅衬底上表面通过研磨或研磨在上表面上被粗糙化。通过损坏或粗糙化的上比抛光或未损坏的下表面收缩更少或具有更低的热膨胀系数。光学测量,在硅衬底升温和冷却之后,硅衬底上表面处于压缩应力下,因此,本发明通过引入粗糙化上表面引起的压应力减小了由外延层生长引起的张应力。

6、本发明中所述应力支撑层表面积小于衬底的表面积,分布在硅衬底中间,在硅衬底升温和冷却过程中硅衬底边缘因缺少支撑对硅衬底引入压应力,缓冲继续外延生长层的张应力,最终降至室温时外延层无翘曲,避免裂纹产生,得到了高质量的外延层。

7、本发明中应力提供niznse层的热膨胀系数比si大,在后期外延结构生长过程中提供压应力,补偿硅衬底在温度变化过程中收到的拉应力。

8、优选的,为了提高应力提供层产生的应力的作用,应力加强层由多层结构堆叠而成。应力加强层包括依次制备在应力提供niznse层上的第一应力加强层和第二应力加强层,其中,第一应力加强层与第二应力加强层的成分相同但含量不同,从而有加强对应力提供层中的压应力。

9、优选的,第二应力加强层的化学式为alx1iny1ga1-x1-y1n,其中,x1不大于0.5,y1不大于0.5;第一应力加强层的化学式为alx2iny2ga1-x2-y2n,其中,x2不大于0.5,y2不大于0.5。

10、优选的,为了更好的达到提供应力效果,第二应力加强层的禁带宽度大于第一应力加强层的禁带宽度,在厚度的设计上,第二应力加强层的厚度可以大于或等于第一应力加强层的厚度。

11、优选的,第二应力加强层的厚度为2~20nm,第一应力加强的厚度为1~3nm。第二应力加强层和第一应力加强层构成一个压应力加强单元,多个压应力加强单元堆叠循环,从而得到多层多周期应力加强层,实现衬底下表面的压应力提供。

12、优选的,循环堆叠的次数不大于10,多层多周期应力加强层的总厚度不大于230nm。

13、本发明还公开了一种led垂直硅衬底外延片的制备方法,其包括:

14、步骤(1):选择硅衬底,研磨所述硅衬底的上表面,形成具有机械残留应力的粗糙面;

15、步骤(2),在硅衬底抛光或未损坏的下表面的中间,依次制备应力提供层和应力加强层作为压应力支撑层,所述压应力支撑层的表面积小于硅衬底的表面积。

16、步骤3),在所述硅衬底的粗糙表上表面依次生长缓冲层、本征gan层、n型gan层、多量子阱层、电子阻挡层、p型gan层。

17、优选地,所述步骤(1)中使用颗粒粒径为3.0~7.0μm的研磨粉进行研磨si片的上表面,形成具有机械残留应力的粗糙面,经研磨后的si表面的粗糙度ra值为100nm~200nm。

18、优选地,所述步骤(2)包含以下步骤:

19、步骤(2.1)通过光刻胶在硅衬底抛光或未损坏的下表面形成图案化掩膜层,暴露出硅衬底的中间区域;

20、步骤(2.2):通过mocvd制备应力提供niznse层,生长温度为500℃~800℃,生长压力为50torr~300torr,生长时所采用的ni源为nimcp2,采用的zn源为dezn,采用的se源为dmse,采用的载气为ar。

21、步骤(2.3)继续通过mocvd生长应力加强alingan层,在在温度为700~100℃、反应室压力为150~200torr、转速为500转/分钟,h2载气下生长多周期的第一应力加强层/第二应力加强层(alx2iny2ga1-x2-y2n/alx1iny1ga1-x1-y1n),其中,x1不大于0.5,y1不大于0.5;的化学式为,其中,x2不大于0.5,y2不大于0.5。其中,第二应力加强层的厚度为2~20nm,第一应力加强的厚度为1~3nm。第二应力加强层和第一应力加强层构成一个压应力加强单元,多个压应力加强单元堆叠循环,从而得到多层多周期应力加强层,实现衬底下表面的压应力提供。优选的,循环堆叠的次数不大于10,多层多周期应力加强层的总厚度不大于230nm。

22、步骤(2.4)去除位于硅衬底边缘的图案化掩膜层。

23、优选地,所述步骤(3)包含以下步骤:

24、步骤(3.1)在所述衬底的上表面粗糙层上使用mocvd沉积所述缓冲层;

25、优选地,所述缓冲层为aln缓冲层,所述aln缓冲层采用下述方法制得:沉积aln缓冲层,其厚度为10nm-50nm。

26、步骤(3.2)在所述缓冲层上沉积所述本征gan层,将反应室温度控制在1050℃-1200℃,压力100torr-600torr,通入nh3作为n源,通入tmga作为ga源,完成在所述缓冲层上沉积所述本征gan层。

27、步骤(3.3)在所述本征gan层上沉积所述n型gan层,将反应室温度控制在1050℃-1200℃,压力100torr-600torr,通入sih4作为si源,通入nh3作为n源,通入tmga作为ga源,完成沉积所述n型gan层;

28、步骤(3.4)在所述n型gan层上沉积所述多量子阱层;具体地,在所述n型gan层上依次重复层叠ingan量子阱层和algan量子垒层,堆叠周期数6~12个。其中,所述ingan量子阱层生长温度为790℃-810℃,厚度为2nm-5nm,生长压力50torr-300torr;所述algan量子垒层生长温度为800℃-900℃,厚度为5nm-15nm,生长压力50torr-300torr,al组分为0.01-0.1。

29、步骤(3.5)在所述多量子阱层上沉积所述电子阻挡层。具体地,所述电子阻挡层为alingan;厚度为10nm-40nm;生长温度900℃-1000℃,压力100torr-300torr,其中al组分0.005<x<0.1,in组分浓度为0.01<y<0.2。

30、步骤(3.6)在所述电子阻挡层上沉积所述p型gan层。具体地,所述p型gan层生长温度900℃-1050℃,厚度10nm-50nm,生长压力100torr~600torr,mg掺杂浓度1×1019cm-3-1×1021cm-3。

31、本发明还公开了一种基于硅衬底的led,其包括上述的led垂直硅衬底外延片。

32、本发明,具有如下有益效果:

33、本发明中硅衬底上表面通过研磨或研磨在上表面上被粗糙化。通过损坏或粗糙化的上比抛光或未损坏的下表面收缩更少或具有更低的热膨胀系数。光学测量,在硅衬底升温和冷却之后,硅衬底上表面处于压缩应力下,因此,本发明通过引入粗糙化上表面引起的压应力减小了由外延层生长引起的张应力。

34、本发明中所述应力支撑层表面积小于衬底的表面积,分布在硅衬底中间,在硅衬底升温和冷却过程中硅衬底边缘因缺少支撑对硅衬底引入压应力,缓冲继续外延生长层的张应力,最终降至室温时外延层无翘曲,避免裂纹产生,得到了高质量的外延层。

35、本发明中应力提供niznse层的热膨胀系数比si大,在后期外延结构生长过程中提供压应力,补偿硅衬底在温度变化过程中收到的拉应力。

36、本发明中应力加强层包括依次制备在应力提供niznse层上的第一应力加强层和第二应力加强层,其中,第一应力加强层与第二应力加强层的成分相同但含量不同,从而有加强对应力提供层中的压应力。

37、本发明的结构可更好地释放基于硅基衬底异质外延时的张应力,解决大规格硅衬底外延异质生长过程中的高密度的裂纹、位错和衬底发生大的翘曲等问题,使得本发明中的外延结构可适用于更大规格的硅衬底。

- 还没有人留言评论。精彩留言会获得点赞!