半导体封装件的制作方法

本发明构思涉及半导体封装件,更具体地,涉及将多个半导体芯片作为一个封装件包括的半导体封装件及其制造方法。

背景技术:

1、半导体封装件是以适合于在电子产品中使用的形式实现的集成电路芯片。在典型的半导体封装件中,半导体芯片可以被安装在印刷电路板(pcb)上,并且可以通过接合线(bonding wire)或凸块电连接到pcb。随着电子工业的发展,已经研究了用于提高可靠性、提供更高的集成度并且提供半导体封装件的进一步小型化的各种技术。

技术实现思路

1、本发明构思的各方面提供了具有改进的电特性的半导体封装件。

2、本发明构思的各方面提供了具有高集成度的半导体封装件。

3、要由本发明构思解决的问题不限于以上提及的问题,并且本领域的普通技术人员将从以下描述清楚地理解未提及的其他问题。

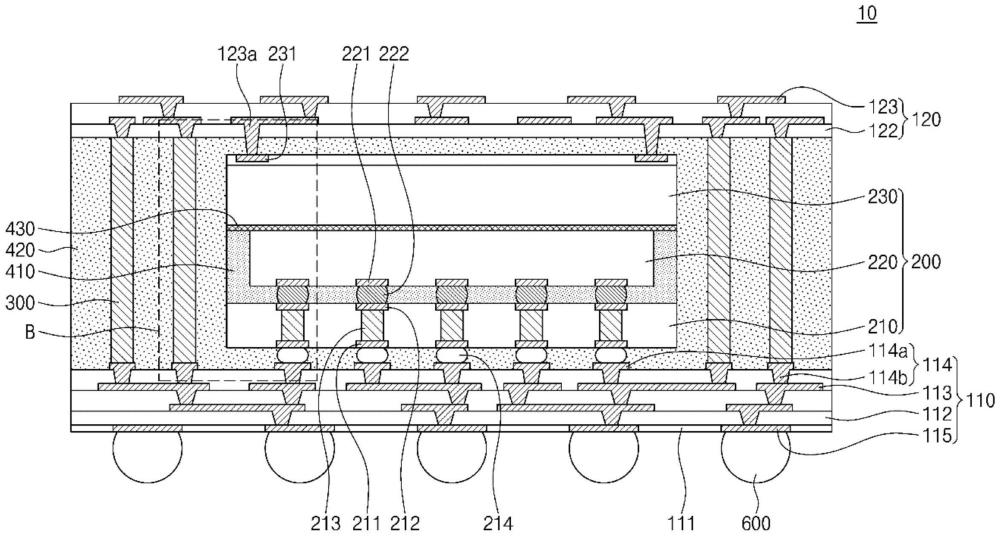

4、一种根据本发明构思的一些实施例的半导体封装件可以包括:第一再分布基板;第二再分布基板,所述第二再分布基板位于所述第一再分布基板上;芯片堆叠件,所述芯片堆叠件位于所述第一再分布基板与所述第二再分布基板之间;第一模制层,所述第一模制层位于所述芯片堆叠件上;以及贯通电极,所述贯通电极延伸到所述第一模制层中并且将所述第一再分布基板电连接到所述第二再分布基板。所述芯片堆叠件可以包括:第一半导体芯片,所述第一半导体芯片位于所述第一再分布基板上,所述第一半导体芯片包括在其中延伸的贯通通路;芯片结构,所述芯片结构包括第二半导体芯片和第二模制层,所述第二半导体芯片位于所述第一半导体芯片上并且电连接到所述贯通通路;以及第三半导体芯片,所述第三半导体芯片位于所述芯片结构与所述第二再分布基板之间,并且所述第一半导体芯片的侧表面可以与所述芯片结构的侧表面共面。

5、一种根据本发明构思的一些实施例的半导体封装件可以包括:第一再分布基板;第一半导体芯片,所述第一半导体芯片位于所述第一再分布基板上,所述第一半导体芯片包括在其中延伸的贯通通路;芯片结构,所述芯片结构位于所述第一半导体芯片上,所述芯片结构包括第二半导体芯片;第三半导体芯片,所述第三半导体芯片位于所述芯片结构上;第二再分布基板,所述第二再分布基板位于所述第三半导体芯片上;连接结构,所述连接结构将所述第一再分布基板电连接到所述第二再分布基板;以及第一模制层,所述第一模制层位于所述第一半导体芯片、所述芯片结构和所述第三半导体芯片上。所述第二再分布基板可以包括绝缘层和位于所述绝缘层中的布线图案,并且所述第三半导体芯片可以包括位于其上的芯片焊盘。所述布线图案中的至少一个布线图案可以延伸到所述第一模制层和所述绝缘层中并且电连接到所述第三半导体芯片的所述芯片焊盘。

6、一种根据本发明构思的一些实施例的半导体封装件可以包括:第一再分布基板;第二再分布基板,所述第二再分布基板位于所述第一再分布基板上;芯片堆叠件,所述芯片堆叠件位于所述第一再分布基板与所述第二再分布基板之间;第一模制层,所述第一模制层位于所述芯片堆叠件上;以及贯通电极,所述贯通电极延伸到所述第一模制层中并且将所述第一再分布基板电连接到所述第二再分布基板。所述芯片堆叠件可以包括:第一半导体芯片,所述第一半导体芯片位于所述第一再分布基板上,所述第一半导体芯片具有在其中延伸的贯通通路;第二半导体芯片,所述第二半导体芯片位于所述第一半导体芯片上,所述第二半导体芯片电连接到所述贯通通路;第二模制层,所述第二模制层位于所述第二半导体芯片与所述第一半导体芯片之间;以及第三半导体芯片,所述第三半导体芯片位于所述第二半导体芯片和所述第二模制层上,所述第三半导体芯片位于所述第二再分布基板与所述第二半导体芯片之间。

技术特征:

1.一种半导体封装件,所述半导体封装件包括:

2.根据权利要求1所述的半导体封装件,其中,所述第二模制层位于所述第一半导体芯片与所述第二半导体芯片之间,并且

3.根据权利要求2所述的半导体封装件,其中,所述芯片结构的所述第二模制层位于所述第二半导体芯片的侧表面上。

4.根据权利要求1所述的半导体封装件,其中,所述第二再分布基板包括绝缘层和位于所述绝缘层中的布线图案,

5.根据权利要求1所述的半导体封装件,其中,所述第二半导体芯片包括第一有源表面和与所述第一有源表面相反的第一后表面,

6.根据权利要求5所述的半导体封装件,其中,所述第一后表面和所述第二后表面通过粘合构件彼此附接。

7.根据权利要求1所述的半导体封装件,所述半导体封装件还包括:

8.根据权利要求1所述的半导体封装件,所述半导体封装件还包括:外部连接端子,所述外部连接端子位于所述第一再分布基板的下表面或所述第二再分布基板的上表面上。

9.一种半导体封装件,所述半导体封装件包括:

10.根据权利要求9所述的半导体封装件,所述半导体封装件还包括:

11.根据权利要求9所述的半导体封装件,其中,所述芯片结构还包括第二模制层,所述第二模制层位于所述第一半导体芯片与所述第二半导体芯片之间,并且

12.根据权利要求9所述的半导体封装件,其中,所述第二半导体芯片包括第一有源表面和与所述第一有源表面相反的第一后表面,

13.根据权利要求12所述的半导体封装件,其中,所述第一后表面和所述第二后表面通过粘合构件彼此附接。

14.根据权利要求9所述的半导体封装件,所述半导体封装件还包括:外部连接端子,所述外部连接端子位于所述第一再分布基板的下表面或所述第二再分布基板的上表面上。

15.根据权利要求9所述的半导体封装件,其中,所述第三半导体芯片的侧表面与所述第一半导体芯片的侧表面共面。

16.一种半导体封装件,所述半导体封装件包括:

17.根据权利要求16所述的半导体封装件,其中,所述第二再分布基板包括绝缘层和位于所述绝缘层中的布线图案,

18.根据权利要求16所述的半导体封装件,其中,所述第二模制层位于所述第二半导体芯片的下表面和侧表面上,

19.根据权利要求16所述的半导体封装件,其中,所述第二半导体芯片包括第一有源表面和与所述第一有源表面相反的第一后表面,

20.根据权利要求16所述的半导体封装件,所述半导体封装件还包括:外部连接端子,所述外部连接端子位于所述第一再分布基板的下表面或所述第二再分布基板的上表面上。

技术总结

提供了一种半导体封装件。所述半导体封装件可以包括:第一再分布基板;第二再分布基板,其位于第一再分布基板上;芯片堆叠件,其位于第一再分布基板与第二再分布基板之间;第一模制层,其位于芯片堆叠件上;以及贯通电极,其延伸到第一模制层中并且将第一再分布基板电连接到第二再分布基板。芯片堆叠件可以包括:第一半导体芯片,其位于第一再分布基板上,第一半导体芯片包括在其中延伸的贯通通路;芯片结构,其包括第二半导体芯片和第二模制层,第二半导体芯片位于第一半导体芯片上并且电连接到贯通通路;以及第三半导体芯片,其位于芯片结构与第二再分布基板之间,并且第一半导体芯片的侧表面可以与芯片结构的侧表面共面。

技术研发人员:朱昶垠,权五局,金善载

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!