半导体结构及其形成方法与流程

本申请涉及半导体,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、在具有沟槽栅极结构的碳化硅mosfet中,沟槽栅极结构底部边缘的电场控制是影响栅极绝缘层可靠性的因素之一。为了控制电场,在一些工艺中,在沟槽栅极结构两侧形成沟槽隔离结构并在沟槽隔离结构底部进行离子注入形成掺杂区。沟槽隔离结构底部的掺杂区比沟槽栅极结构更深。

2、然而,沟槽隔离结构以及掺杂区的形成需要额外的沟槽蚀刻和多次离子注入,其工艺效率低并且电场控制能力也并不能得到保证,器件可靠性低。

3、因此,有必要提供更有效、更可靠的技术方案,提高工艺效率以及电场控制能力。

技术实现思路

1、本申请提供一种半导体结构及其形成方法,可以提高具有沟槽栅极结构的碳化硅mosfet中沟槽栅极结构底部边缘的电场控制能力以及工艺效率。

2、本申请的一个方面提供一种半导体结构的形成方法,包括:提供基底,所述基底包括半导体衬底以及位于所述半导体衬底表面的外延层,所述外延层中包括用于形成沟槽栅极结构的栅极区域;在所述外延层表面形成覆盖所述栅极区域的掩膜层,所述掩膜层的材料为半导体材料;以所述掩膜层为掩膜采用离子注入工艺在所述栅极区域两侧的外延层中形成屏蔽结构,所述栅极区域的长度小于所述屏蔽结构的长度。

3、在本申请的一些实施例中,所述半导体材料包括掺锗的多晶硅、碳化硅、非晶碳化硅或s i gec。

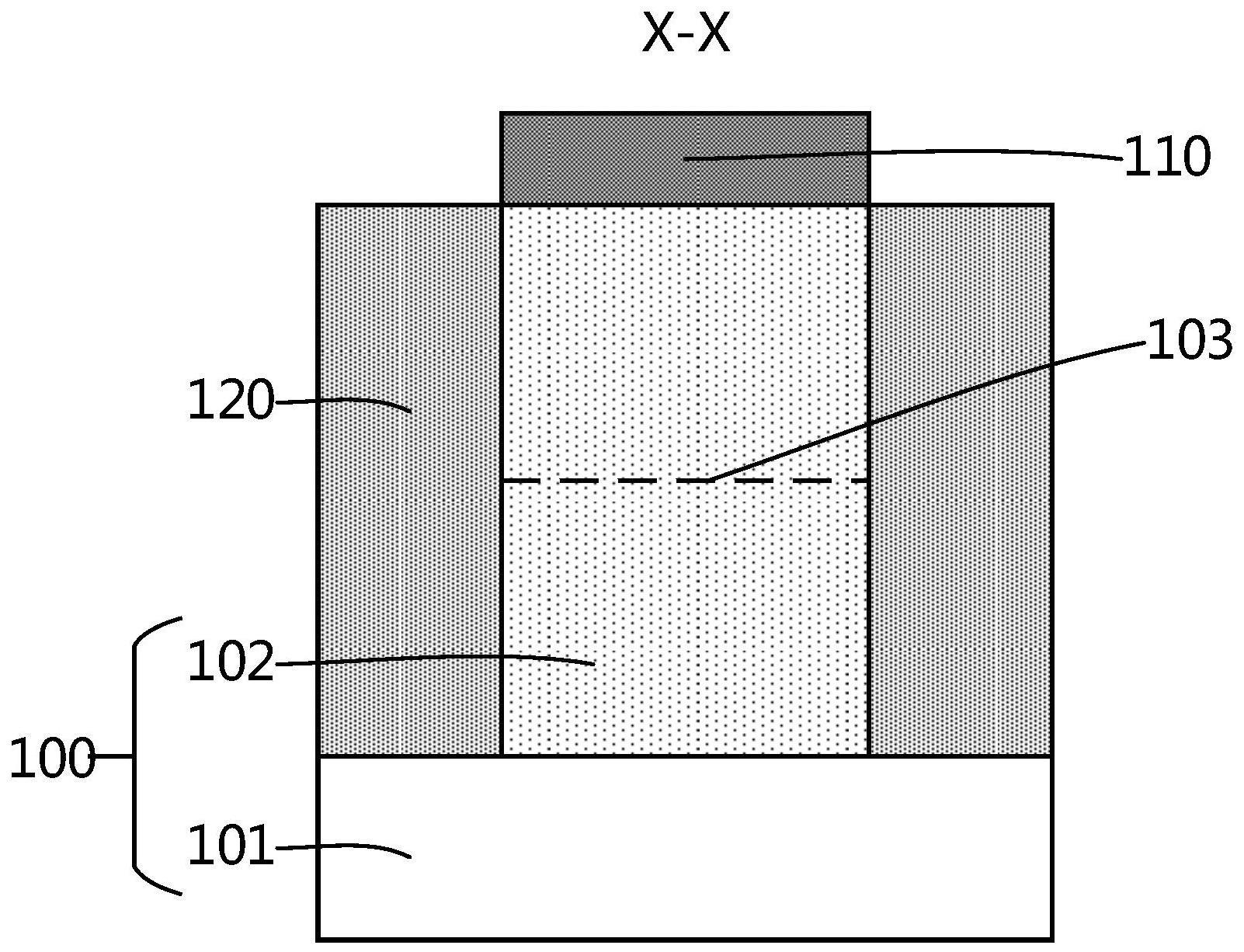

4、在本申请的一些实施例中,形成所述掩膜层的方法包括化学气相沉积工艺或溅射工艺。

5、在本申请的一些实施例中,所述掩膜层的厚度为5微米至10微米。

6、在本申请的一些实施例中,所述外延层的材料为4h-s i c,所述外延层的上表面为硅面,所述硅面与水平面的偏角为0至4度。

7、在本申请的一些实施例中,所述离子注入工艺的注入角度与所述硅面的法线的夹角为-0.5度至5度;所述离子注入工艺的注入离子为铝离子;所述离子注入工艺的注入能量为500kev至50mev;所述离子注入工艺的注入深度为2微米至15微米;所述离子注入工艺的注入浓度为5e15atom/cm3至1e17atom/cm3;所述离子注入工艺的温度为100摄氏度至1200摄氏度。

8、在本申请的一些实施例中,所述半导体结构的形成方法还包括:在所述栅极区域中形成沟槽栅极结构,所述屏蔽结构的深度大于所述沟槽栅极结构的深度。

9、在本申请的一些实施例中,所述屏蔽结构贯穿所述外延层。

10、本申请的另一个方面还提供一种半导体结构,包括:基底,所述基底包括半导体衬底以及位于所述半导体衬底表面的外延层,所述外延层中包括用于形成沟槽栅极结构的栅极区域;掩膜层,位于所述外延层表面覆盖所述栅极区域,所述掩膜层的材料为半导体材料;屏蔽结构,位于所述栅极区域两侧的外延层中,所述栅极区域的长度小于所述屏蔽结构的长度。

11、在本申请的一些实施例中,所述半导体材料包括掺锗的多晶硅、碳化硅、非晶碳化硅或s i gec。

12、在本申请的一些实施例中,所述掩膜层的厚度为5微米至10微米。

13、在本申请的一些实施例中,所述外延层的材料为4h-s i c,所述外延层的上表面为硅面,所述硅面与水平面的偏角为0至4度。

14、在本申请的一些实施例中,所述屏蔽结构中具有注入离子,所述注入离子为铝离子;所述注入离子的浓度为5e15atom/cm3至1e17atom/cm3。

15、在本申请的一些实施例中,所述半导体结构还包括:沟槽栅极结构,位于所述栅极区域的外延层中,所述屏蔽结构的深度大于所述沟槽栅极结构的深度。

16、在本申请的一些实施例中,所述屏蔽结构贯穿所述外延层。

17、本申请提供一种半导体结构及其形成方法,在沟槽栅极结构两侧形成屏蔽结构,可以提高具有沟槽栅极结构的碳化硅mosfet中沟槽栅极结构底部边缘的电场控制能力以及工艺效率,此外利用半导体材料作为离子注入工艺时的掩膜,可以提高离子注入质量和整体工艺效率,提高屏蔽结构的质量,提高器件性能和器件可靠性。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,所述半导体材料包括掺锗的多晶硅、碳化硅、非晶碳化硅或sigec。

3.如权利要求2所述的半导体结构的形成方法,其特征在于,形成所述掩膜层的方法包括化学气相沉积工艺或溅射工艺。

4.如权利要求1所述的半导体结构的形成方法,其特征在于,所述掩膜层的厚度为5微米至10微米。

5.如权利要求1所述的半导体结构的形成方法,其特征在于,所述外延层的材料为4h-sic,所述外延层的上表面为硅面,所述硅面与水平面的偏角为0至4度。

6.如权利要求5所述的半导体结构的形成方法,其特征在于,所述离子注入工艺的注入角度与所述硅面的法线的夹角为-0.5度至5度;所述离子注入工艺的注入离子为铝离子;所述离子注入工艺的注入能量为500kev至50mev;所述离子注入工艺的注入深度为2微米至15微米;所述离子注入工艺的注入浓度为5e15atom/cm3至1e17atom/cm3;所述离子注入工艺的温度为100摄氏度至1200摄氏度。

7.如权利要求1所述的半导体结构的形成方法,其特征在于,还包括:在所述栅极区域中形成沟槽栅极结构,所述屏蔽结构的深度大于所述沟槽栅极结构的深度。

8.如权利要求7所述的半导体结构的形成方法,其特征在于,所述屏蔽结构贯穿所述外延层。

9.一种半导体结构,其特征在于,包括:

10.如权利要求9所述的半导体结构,其特征在于,所述半导体材料包括掺锗的多晶硅、碳化硅、非晶碳化硅或sigec。

11.如权利要求9所述的半导体结构,其特征在于,所述掩膜层的厚度为5微米至10微米。

12.如权利要求9所述的半导体结构,其特征在于,所述外延层的材料为4h-sic,所述外延层的上表面为硅面,所述硅面与水平面的偏角为0至4度。

13.如权利要求9所述的半导体结构,其特征在于,所述屏蔽结构中具有注入离子,所述注入离子为铝离子;所述注入离子的浓度为5e15atom/cm3至1e17atom/cm3。

14.如权利要求9所述的半导体结构,其特征在于,还包括:沟槽栅极结构,位于所述栅极区域的外延层中,所述屏蔽结构的深度大于所述沟槽栅极结构的深度。

15.如权利要求14所述的半导体结构,其特征在于,所述屏蔽结构贯穿所述外延层。

技术总结

本申请提供半导体结构及其形成方法,所述半导体结构包括:基底,所述基底包括半导体衬底以及位于所述半导体衬底表面的外延层,所述外延层中包括用于形成沟槽栅极结构的栅极区域;掩膜层,位于所述外延层表面覆盖所述栅极区域,所述掩膜层的材料为半导体材料;屏蔽结构,位于所述栅极区域两侧的外延层中,所述栅极区域的长度小于所述屏蔽结构的长度。本申请提供一种半导体结构及其形成方法,在沟槽栅极结构两侧形成屏蔽结构,可以提高具有沟槽栅极结构的碳化硅MOSFET中沟槽栅极结构底部边缘的电场控制能力以及工艺效率,此外利用半导体材料作为离子注入工艺时的掩膜,可以提高离子注入质量,提高屏蔽结构的质量,提高器件性能和器件可靠性。

技术研发人员:三重野文健,周永昌

受保护的技术使用者:飞锃半导体(上海)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!