一种双沟槽栅RC-IGBT及其制备方法与流程

本发明涉及半导体,尤其涉及一种双沟槽栅rc-igbt及其制备方法。

背景技术:

1、绝缘栅双极型晶体管(insulated gate bipolar transistor,igbt)同时集金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)易驱动和双极型晶体管(bipolar junction transistor,bjt)大电流两个显著特点于一身,因此在新能源、高铁、智能电网、电动汽车这些绿色产业中成为不可或缺的核心功率器件。igbt通常为单向器件,自身不具备逆向导通能力,在大部分的igbt应用电路中,都需要反并联续流二极管(fast recovery diode,frd)进行保护。

2、早期且现在仍在采用的做法是分别制作igbt和二极管,再将两者封装在一起,做成igbt模块。这样的做法使igbt模块寄生电感较高、集成度较低。为降低成本、提高芯片的功率密度,igbt与二极管同时在集成同一个硅片上的逆导型igbt(reverse conductingigbt, rc-igbt)相继问世以后,rc-igbt已有取代传统集成封装igbt、二极管对的趋势。基于igbt的薄片工艺,将二极管的阴极集成到igbt的阳极中,于是传统igbt的阳极就变成了p区、n区周期性交替排列的结构。而二极管的阳极为传统igbt的p型发射区。当rc-igbt正向导通时,阳极p型集电区向n型漂移区注入少数载流子空穴,电流从igbt阴极流出;而当rc-igbt反向导通时,器件的电流由正向导通的二极管传导,即电流从rc-igbt阳极p型发射区流出,经p型阱区,n型漂移区,n型缓冲层流入阴极,也即第一n型集电区。

3、然而,现有的rc-igbt结构存在正向导通时有电压折回(voltage snapback)现象,反向恢复性能差和漂移区电流分布不均匀等问题;其中,电压折回现象是由于rc-igbt器件工作模式发生切换,电阻率突然减小而产生负阻效应导致的。

技术实现思路

1、本发明提供了一种双沟槽栅rc-igbt及其制备方法,以抑制电压折回现象的产生。

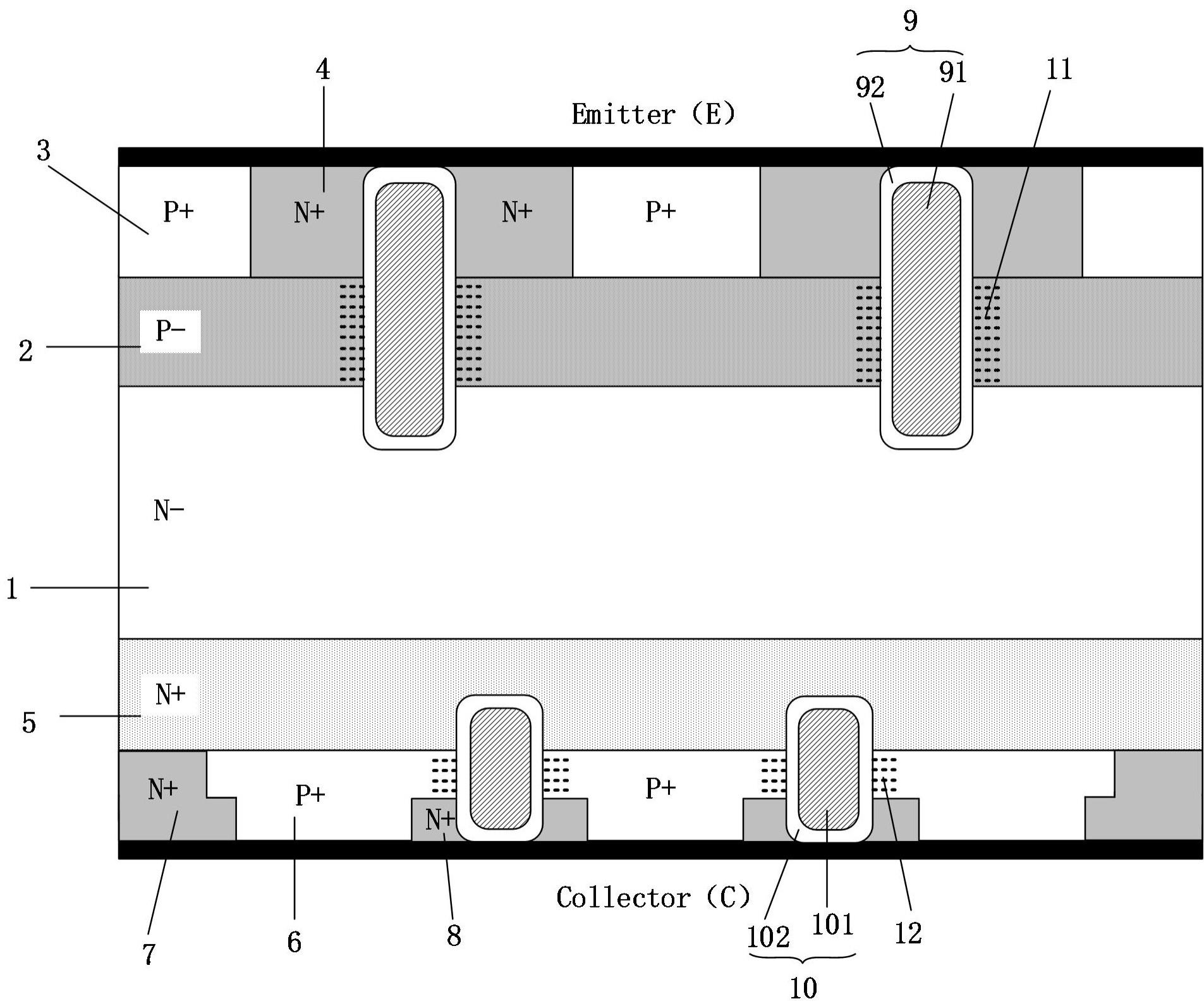

2、根据本发明的一方面,提供了一种双沟槽栅rc-igbt,包括:

3、n型漂移区,具有正面以及与该正面相对的背面;

4、p型阱区,与n型漂移区的正面电接触;

5、p型发射区和n型发射区,在所述p型阱区上依次交替设置,并且均经由p型阱区与n型漂移区的正面电接触;

6、n型缓冲层,与n型漂移区的背面电接触;

7、p型集电区、第一n型集电区和第二n型集电区;p型集电区经由n型缓冲层与n型漂移区的背面电接触;第一n型集电区经由n型缓冲层与n型漂移区的背面电接触;第二n型集电区内嵌于p型集电区远离n型缓冲层的一面,并依次经由p型集电区和n型缓冲层与n型漂移区的背面电接触;

8、第一沟槽栅结构,由n型发射区的表面垂直延伸至n型漂移区内;

9、第二沟槽栅结构,由第二n型集电区的表面垂直延伸至n型缓冲层内。

10、可选地,第一n型集电区的厚度与p型集电区的厚度相同,并且第一n型集电区与p型集电区的接触面呈阶梯状。

11、可选地,位于第二沟槽栅结构与第一n型集电区之间的p型集电区呈t字型。

12、可选地,至少部分第一n型集电区在垂直于缓冲层的方向上与p型发射区对位设置;

13、至少部分p型集电区在垂直于缓冲层的方向上与n型发射区对位设置。

14、可选地,第一沟槽栅结构用于在n型漂移区与n型发射区之间形成的第一n沟道,第二沟槽栅结构用于在n型缓冲层与第二n型集电区之间形成的第二n沟道;第一n沟道与第二n沟道在缓冲层上的垂直投影至少部分重叠。

15、可选地,第一沟槽栅结构包括第一多晶硅栅极和包裹第一多晶硅栅极的第一氧化层;

16、第二沟槽栅结构包括第二多晶硅栅极和包裹第二多晶硅栅极的第二氧化层。

17、根据本发明的另一方面,提供了一种双沟槽栅rc-igbt器件的制备方法,包括:

18、提供n型衬底;

19、于n型衬底的正面进行rc-igbt器件的正面工艺,形成n型漂移区、p型阱区、p型发射区、n型发射区以及第一沟槽栅结构;其中,n型漂移区具有正面以及与该正面相对的背面;p型阱区与n型漂移区的正面电接触;p型发射区和n型发射区依次交替设置,并且均经由p型阱区与n型漂移区的正面电接触;第一沟槽栅结构,由n型发射区的表面垂直延伸至n型漂移区内;

20、于衬底的背面进行rc-igbt器件的背面工艺,形成n型缓冲层、p型集电区、第一n型集电区、第二n型集电区和第二沟槽栅结构;其中,n型缓冲层与n型漂移区的背面电接触;p型集电区经由n型缓冲层与n型漂移区的背面电接触;第一n型集电区经由n型缓冲层与n型漂移区的背面电接触;第二n型集电区内嵌于p型集电区远离n型缓冲层的一面,并依次经由p型集电区和n型缓冲层与n型漂移区的背面电接触;第二沟槽栅结构由第二n型集电区的表面垂直延伸至n型缓冲层内。

21、可选地,于n型衬底的正面进行rc-igbt器件的正面工艺包括:

22、在选定的n型衬底上定义有源区,生长场区氧化层;

23、根据有源区元胞和终端结构设计,定义出p型环;

24、在第一沟槽栅结构的预设位置刻蚀形成第一沟槽,于第一沟槽的侧壁形成第一氧化层并在第一氧化层中形成第一多晶硅栅极;其中第一多晶硅栅极和第一氧化层用于构成第一沟槽栅结构;

25、在p型阱区的预设位置和p型发射区的预设位置注入p型掺杂离子并扩散形成p型阱区和p型发射区;

26、在n型发射区的预设位置内注入n型掺杂离子并扩散形成n型发射区;

27、制备正面ct接触孔,并在ct接触孔内形成金属电极;

28、通过沉积制备钝化层和保护层中至少一个。

29、可选地,于n型衬底的背面进行rc-igbt器件的背面工艺包括:

30、将n型衬底减薄至预设的厚度;

31、在减薄后的n型衬底的背面注入n型掺杂离子至n型缓冲层的预设位置,形成n型缓冲层;

32、在第二沟槽栅结构的预设位置刻蚀形成第二沟槽,于第二沟槽的侧壁形成第二氧化层并在第二氧化层中形成第二多晶硅栅极;其中第二多晶硅栅极和第二氧化层用于构成第二沟槽栅结构;

33、在减薄后的n型衬底的背面注入p型掺杂离子形成p型掺杂层;

34、在p型掺杂层内注入n型掺杂离子并扩散形成第一n型集电区和第二n型集电区;其中,p型掺杂层中未注入n型掺杂离子的区域形成p型集电区。

35、可选地,制备第一n型集电区和第二n型集电区时,通过两道掩模版完成第一n型集电区和第二n型集电区的制备。

36、本发明实施例的技术方案,通过在rc-igbt器件的背面工艺中设置第二沟槽栅结构,并设置第二n型集电区内嵌于p型集电区远离n型缓冲层的一面,如同在一个p型衬底上生长了n沟道mosfet,在第二沟槽栅的栅极加正向偏压使其沟道开启,在p型集电极加正偏压的时候,控制该nmos导通,电子流可以从n型缓冲层经由n沟道流入第二n型集电区,即使p型集电极电压持续增大,该器件工作模式依然是单极导电模式,不转换为双极型导电模式,从而抑制电导调制效应,进而抑制电压折回现象的产生。

37、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!