半导体器件及其制造方法与流程

本申请的实施例涉及半导体器件及其制造方法。

背景技术:

1、随着半导体技术的进步,对更高存储容量、更快处理系统、更高性能和更低成本的需求日益增加。为了满足这些需求,半导体工业持续缩小半导体器件的尺寸,诸如金属氧化物半导体场效应晶体管(mosfet)、鳍式场效应晶体管(finfet)和全环栅(gaa)fet。这种按比例缩小增加了半导体制造工艺的复杂性。

技术实现思路

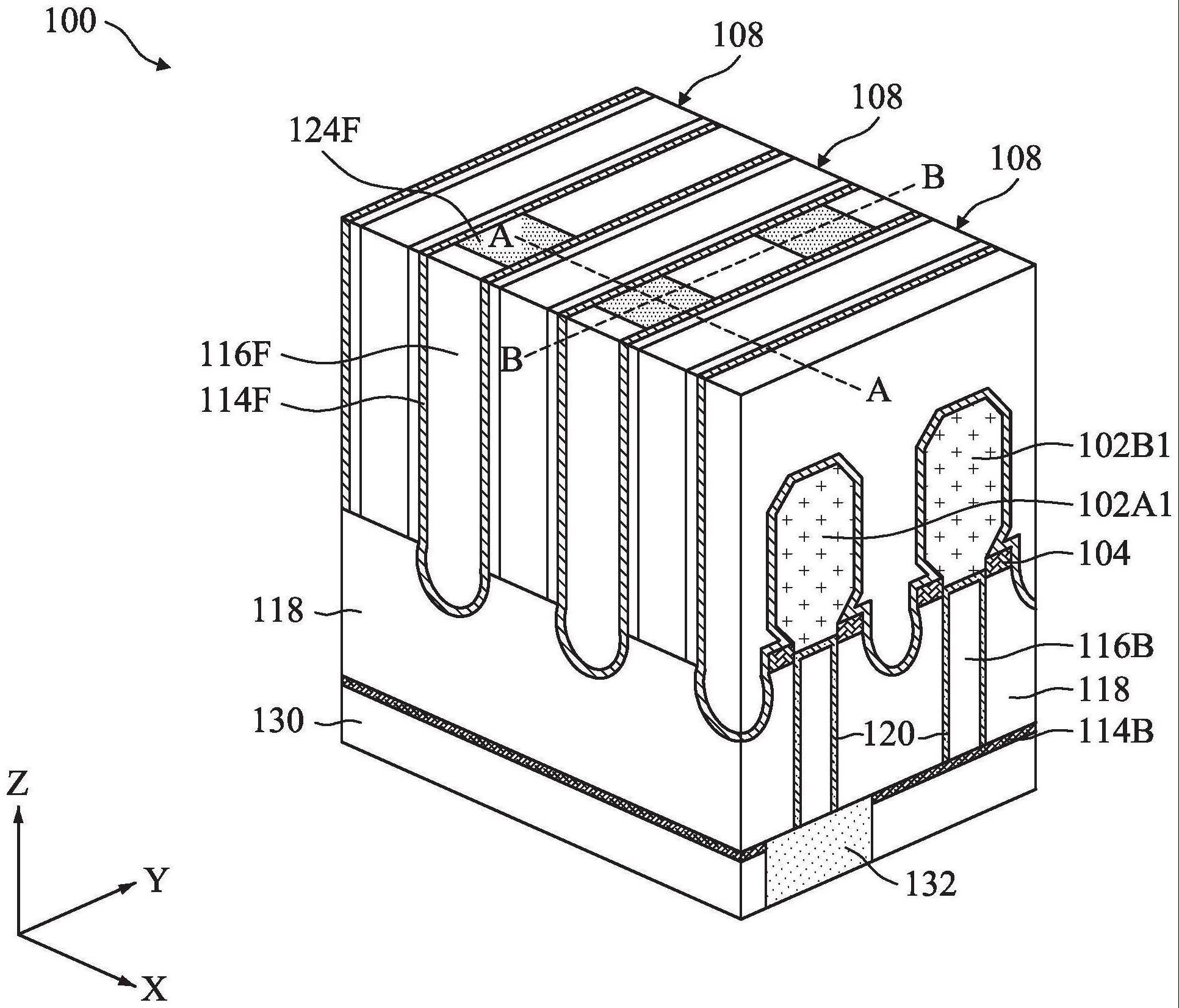

1、本申请的一些实施例提供了一种半导体器件,包括:第一源极/漏极(s/d)区域和第二源极/漏极区域;纳米结构半导体层的堆叠件,与所述第一源极/漏极区域相邻设置;栅极结构,至少部分地围绕每个所述纳米结构半导体层;第一对间隔件,设置在所述第一源极/漏极区域的相对侧壁上;第二对间隔件,设置在所述第二源极/漏极区域的相对侧壁上;第三对间隔件,设置在所述栅极结构的相对侧壁上;第一接触结构,设置在所述第一源极/漏极区域的第一表面上;以及第二接触结构,设置在所述第一源极/漏极区域的第二表面上,其中,所述第一表面和所述第二表面彼此相对,并且其中,所述第一对间隔件设置在所述第二接触结构的相对侧壁上。

2、本申请的另一些实施例提供了一种半导体器件,包括:第一纳米结构沟道区域和第二纳米结构沟道区域;第一栅极结构和第二栅极结构,分别至少部分地围绕所述第一纳米结构沟道区域和所述第二纳米结构沟道区域;外延区域,设置在所述第一纳米结构沟道区域和所述第二纳米结构沟道区域之间;第一间隔件和第二间隔件,设置在所述外延区域的相对侧壁上;以及接触结构,设置在所述外延区域上以及所述第一间隔件和所述第二间隔件之间。

3、本申请的又一些实施例提供了一种制造半导体器件的方法,包括:在衬底上形成鳍结构;在所述鳍结构的第一鳍区域上形成包括第一纳米结构层和第二纳米结构层的超晶格结构;在所述鳍结构的相对侧壁上形成第一间隔件和第二间隔件;在所述鳍结构的第二鳍区域上以及所述第一间隔件和所述第二间隔件之间形成外延区域;用栅极结构替换所述第二纳米结构层;用所述导电层替换所述鳍结构的第一部分;以及用所述介电层替换所述鳍结构的第二部分。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,还包括:设置在所述第二源极/漏极区域上的介电层,其中,所述第二对间隔件设置在所述介电层的相对侧壁上。

3.根据权利要求1所述的半导体器件,其中,所述第一对间隔件和所述第二对间隔件与所述第三对间隔件物理接触,以及

4.根据权利要求1所述的半导体器件,还包括:设置在所述第一源极/漏极区域的相对侧壁上和所述第一对间隔件的侧壁上的介电层。

5.根据权利要求1所述的半导体器件,还包括:设置在所述第一源极/漏极区域和所述第二源极/漏极区域之间的介电层,其中,所述第一对间隔件和所述第二对间隔件设置在所述介电层上。

6.根据权利要求1所述的半导体器件,其中,所述第二接触结构包括接触插塞和设置在所述接触插塞上的阻挡层,以及

7.根据权利要求1所述的半导体器件,还包括:

8.根据权利要求1所述的半导体器件,还包括:设置在所述第一源极/漏极区域和所述第二源极/漏极区域之间的浅沟槽隔离(sti)区域,其中,所述第二接触结构设置在所述浅沟槽隔离区域中。

9.一种半导体器件,包括:

10.一种制造半导体器件的方法,包括:

技术总结

公开了具有背侧接触结构的半导体器件及其制造方法。半导体器件包括:第一和第二S/D区域;纳米结构半导体层的堆叠件,与第一S/D区域相邻设置;栅极结构,围绕每个纳米结构半导体层;第一对间隔件,设置在第一S/D区域的相对侧壁上;第二对间隔件,设置在第二S/D区域的相对侧壁上;第三对间隔件,设置在栅极结构的相对侧壁上;第一接触结构,设置在第一S/D区域的第一表面上;以及第二接触结构,设置在第一S/D区域的第二表面上。第一表面和第二表面彼此相对。第一对间隔件设置在第二接触结构的相对侧壁上。

技术研发人员:林志昌,张荣宏,陈仕承,王志豪,姚茜甯,庄宗翰,江国诚

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!