一种功率器件栅极集成电阻、功率器件及其制备方法与流程

本发明涉及功率器件,特别涉及一种功率器件栅极集成电阻、功率器件及其制备方法。

背景技术:

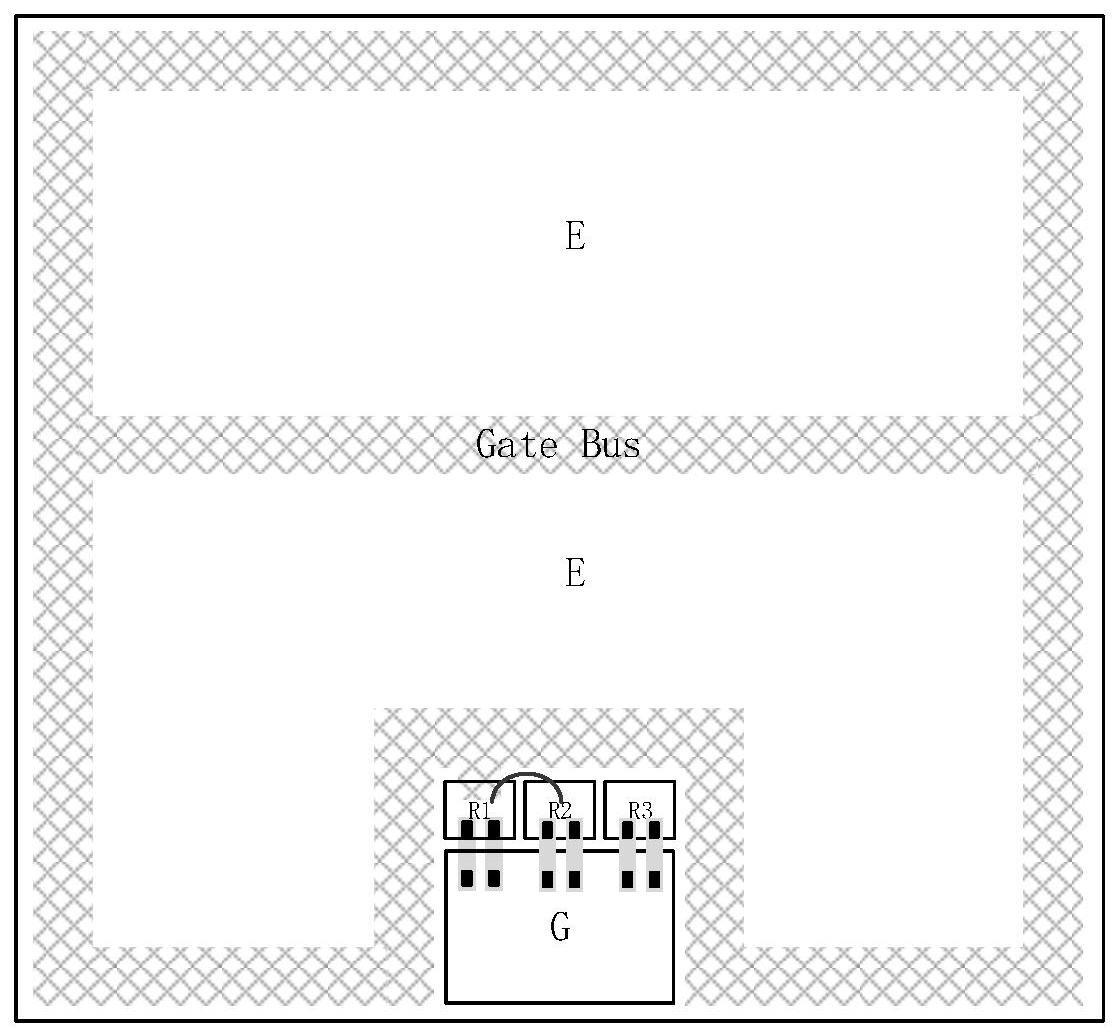

1、在大电流功率模块中,igbt芯片和frd芯片往往需要并联封装在一起,如三组200a芯片并联在一起形成一个600a的芯片单元组,如图。igbt的集电极被焊接到dbc板上同一铜箔区域;集电极需要导通大电流,通过一排排密集的铝丝绑线焊接到dbc板的集电极铜箔走线上;每个igbt的栅极则是通过一根细金属线,引到dbc上的栅极导线上,进而连接到模块的栅级金属端子。

2、由于igbt的栅极金属线一般较细,本身会产生一定的寄生电感,金属丝越细、越长,寄生电感越大,一般为几nh到几十nh。而且并联的不同芯片由于摆放位置的区别,从栅极出发到最终连接到模块的栅级金属端子的距离往往存在一定的差距,即每个并联的igbt的栅极是通过不同的寄生电感连接到模块的栅极端子,在多芯片并联的情况下,近端igbt和远端igbt的寄生电感甚至会达到几倍的差距。原理如图1所示,在igbt模块接收到开启信号后,寄生电感在电流快速的变化下(di/dt),会产生一定的分压vl=l*(di/dt)。那么最终降在igbt栅极上的电压为vg-vl,由于近端igbt和远端igbt的寄生电感存在一定差距,甚至呈倍数级的差距,也就是说vl存在同比的差异。最终降在并联芯片的栅极上的电压vg-vl就会产生明显的不均衡,导致各个芯片间开启不同步。会产生一些诸如下述的现象,有的芯片已经开启完成了,有的还正在开启过程中,流过每个并联芯片的电流不一致。以上就是功率器件领域非常注重的igbt均流问题。

3、如图2所示,在每个igbt芯片前面加上一个栅极电阻,问题便可以得到解决。在igbt开通瞬间,每个并联支路上,电流流过电感和栅极电阻,电感是nh级,电阻是欧姆级。电感上分压与电阻上分压相比,可以忽略掉。这样,就能使得每个并联芯片的igbt栅极电位基本一致。

4、现有技术根据上述原理有以下两种技术路线:一是芯片外就近外接栅极电阻法,在每颗并联芯片的栅极就近位置的dbc板上焊接一颗阻值相同的贴片电阻,这样可以达到一定的效果,但是由于芯片栅极绑线点到外接电阻绑线点还是有一定的距离,就是说电阻和栅极之间依然存在一定的寄生电感,没有完全解决。二是芯片内集成栅极电阻法,将栅极电阻直接集成到芯片内,现主流集成栅极电阻的方法是利用igbt制备过程中的多晶硅淀积层的刻蚀工艺形成栅极电阻,主要是集成到栅极pad附近;该方法能够使集成电阻最大限度的靠近原胞区甚至每个原胞的栅极,能够有效解决均流性问题。

5、现有技术公开了一种多晶硅内置栅极电阻技术;利用igbt制备过程中的多晶硅淀积工艺,在栅极pad附近和栅极汇流条之间,刻蚀出一块或多块多晶硅区域与二者相连,多晶硅区域可刻蚀出具有一定阻值的任意形状。这块具有一定阻值的多晶硅电阻区域就形成了igbt的栅极集成电阻rgint。上述方案存在一定局限性:一是芯片内集成栅极电阻的阻值由工艺版图确定,一经确定,不能调整。如果需要调整阻值,需要经历修改芯片版图,再重新流片,测试等,周期漫长且呈续繁杂,修改一个电阻值基本等同于重新开发一颗芯片。二是芯片内集成栅极电阻很难同时兼容大范围应用频率,外部电阻调节作用有限。如图3所示,在实际的应用中,会根据应用电路的拓扑结构、应用频率等,需要大幅调整栅极电阻。因为栅极的充放电时间t∝rc,由于功率器件的c由内部结构寄生产生,数值基本确定,一般通过在外电路加外接电阻,并加以调节来适应各种频率的开关应用。那么可能就有可能产生如下的场景:例如,某规格igbt模块内部由两组igbt芯片和frd芯片并联,igbt集成栅极电阻为15欧,外部电阻20欧,适用15khz应用;现需将该规格igbt应用在某30khz的应用电路。通过调节外部栅极电阻收效甚微,即便是将20欧外部电阻全部拿掉依然由于开关速度慢难以满足高频电路应用。因为芯片内集成栅极电阻已经确定,已经没办法继续降低。相反,如果只为满足高频应用,内部集成的栅极电阻阻值较低的话,在一些低频频率大电流应用场景中,也可能会出现内部寄生电感引起的均流问题。三是外置栅极电阻的方式,使得在功率模块封装过程中,可以在芯片就近的dbc位置处焊接电阻连接栅极,但是不能有效规避栅极到外置电阻连接产生的寄生电感。

技术实现思路

1、本发明实施例的目的是提供一种功率器件栅极集成电阻、功率器件及其制备方法,通过在封装端采用阻值可调的栅极集成电阻的功率器件,在栅极和栅极汇流条之间形成了一个可调可变的内置集成电阻网络,具有电阻调节便利、无需重新进行芯片设计开发、适用频率范围宽、均流效果好等优点。

2、为解决上述技术问题,本发明实施例的第一方面提供了一种功率器件栅极集成电阻,用于栅极电压控制型功率器件,所述栅极集成电阻包括:设置于栅极pad和栅极汇流条之间的若干个电阻单元;

3、所述电阻单元的一端与所述栅极pad连接,其另一端通过电阻引出极与所述栅极汇流条连接或悬空;

4、至少一个所述电阻引出极与所述栅极汇流条连接;

5、若干个所述电阻引出极之间电气隔离,可通过外置导线连接。

6、进一步地,所述电阻引出极与至少一个所述电阻单元对应连接;

7、至少一个所述电阻引出极与所述栅极汇流条连接,其余所述电阻引出极悬空设置,可通过外置导线互相连接。

8、进一步地,若干个所述电阻引出极与所述电阻单元对应连接;

9、另一个所述电阻引出极仅与所述栅极汇流条连接,仅与所述栅极汇流条连接的所述电阻引出极可通过外置导线与其它所述电阻引出极连接。

10、进一步地,所述电阻单元为所述电阻引出极和所述栅极的金属层下面通过多晶硅层刻蚀得到的多晶硅电阻;

11、所述多晶硅电阻和所述电阻引出极金属层之间设有隔离用的氧化层;

12、所述多晶硅电阻的两端通过通孔分别与所述栅极和所述电阻引出极连接。

13、进一步地,所述功率器件栅极电阻的阻值为直接与所述栅极汇流条直接连接和/或经所述外置导线与所述栅极汇流条间接连接的所述电阻单元并联连接的电阻值:

14、1/rgint=(1/r1)+……+(1/rn);

15、其中,rgint为所述栅极电阻的阻值,r1-rn为与所述栅极直接或间接连接的n个所述电阻单元的阻值。

16、进一步地,所述电阻单元及对应的所述电阻引出极设置于所述栅极的至少一侧。

17、进一步地,所述外置导线为铝线、铜线、银线、金线或合金导线中的一种。

18、相应地,本发明实施例的第二方面提供了一种功率器件,包括上述任一所述的功率器件栅极集成电阻。

19、相应地,本发明实施例的第三方面提供了一种功率器件制备方法,用于制造上述功率器件,包括如下步骤:

20、在硅表面的栅极区域形成一层氧化层以隔离衬底,并作为栅氧化层;

21、淀积一层原位掺杂多晶硅材料,平铺在衬底表面;

22、通过刻蚀工艺刻蚀表面多晶硅材料,在栅极多晶硅和汇流条多晶硅间形成电气隔离;

23、在多晶硅层上淀积一层氧化层,作为绝缘钝化层;

24、在栅极区的多晶硅上和延伸到电阻极区的多晶硅上开孔,用于与金属层连接;

25、以溅射或蒸镀的形式在栅极区表面淀积一层金属,通过通孔连接到栅极区的多晶硅和电阻电极区的多晶硅;

26、刻蚀金属,形成栅极pad和电阻引出极的电气隔离,栅极pad和电阻引出极间通过电阻rn相连,至少一个电阻引出极与栅极汇流条相连,延伸到有源区的各个原胞。

27、相应地,本发明实施例的第四方面提供了一种功率器件制备方法,用于制造上述功率器件,包括如下步骤:

28、在硅表面的栅极区域刻蚀出沟槽分布;

29、通过氧化工艺在沟槽和硅表面形成一层致密氧化层作为栅氧;

30、淀积一层原位掺杂多晶硅材料,并填充沟槽形成原胞内的栅极;

31、通过刻蚀工艺或者研磨工艺去除表面多晶硅材料,形成互相独立的沟槽栅;

32、在栅极表面淀积一层氧化层,作为绝缘钝化层;

33、在栅极区的多晶硅沟槽上和延伸到电阻引出区的多晶硅沟槽上开孔,用于与金属层连接;

34、以溅射或蒸镀的形式在栅极区表面淀积一层金属,通过通孔连接到栅极区的多晶硅和电阻引出区的多晶硅;

35、刻蚀金属,形成栅极pad和电阻引出区的电气隔离,栅极pad和电阻引出区通过若干个电阻单元分别相连,电阻引出区与栅极汇流条相连,延伸到有源区的各个原胞。

36、本发明实施例的上述技术方案具有如下有益的技术效果:

37、通过在封装端采用阻值可调的栅极集成电阻的功率器件,在栅极和栅极汇流条之间形成了一个可调可变的内置集成电阻网络,具有电阻调节便利、无需重新进行芯片设计开发、适用频率范围宽、均流效果好等优点。

- 还没有人留言评论。精彩留言会获得点赞!