半导体器件及其制造方法与流程

本申请涉及半导体,具体涉及一种半导体器件及其制造方法。

背景技术:

1、随着科技的发展,碳化硅(sic)和氮化镓(gan)等半导体材料以其相比于硅材料具有较大的禁带宽度,较高的热导率,较高的电子饱和漂移速度以及10倍于硅材料的临界击穿电场,而被广泛应用在高温、高频、大功率、抗辐射等技术领域。

2、碳化硅(sic)-金氧半场效晶体管(metal-oxide-semiconductor field-effecttransistor, mosfet)作为开关器件,为防止开关过程中电流突变,造成过高的电压尖峰损坏sic-mosfet器件,需要一个反向并联的续流二极管。目前,通常采用sic-mosfet器件自身的寄生体二极管作为续流二极管。

3、但是,若直接采用sic-mosfet器件自身的寄生体二极管,由于碳化硅禁带宽度较宽,其自身的寄生体二极管的开启电压非常高,会造成系统额外的功率损耗。此外,其自身的寄生体二极管开启后,由于sic材料的双极退化效应,

4、导致sic-mosfet器件产生较大的导通压降,对sic-mosfet器件的可靠性造成严重影响。

技术实现思路

1、本申请提供了一种半导体器件及其制造方法,可以提高半导体器件的可靠性。

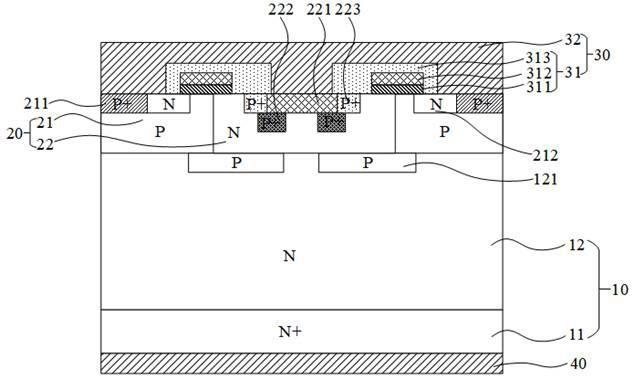

2、第一方面,本申请提供了一种半导体器件,包括:

3、半导体衬底,所述半导体上设置有n型漂移区,所述n型漂移区漂移区内设置有两个间隔设置的p型埋层;

4、功能层,所述功能层设置于所述n型漂移区上,所述功能层包括n型电流拓展区和两个设置于所述n型电流拓展区两侧的p型基区,所述p型基区内设置有相互连接的p+欧姆接触区和n型源区,所述n型电流拓展区内设置有多晶硅沟槽,所述多晶硅沟槽的底部设置有两个间隔设置的第一p+埋层、所述多晶硅沟槽的两侧设置有第二p+埋层;

5、器件层,所述器件层包括栅极结构和第一金属层,所述栅极结构设置于所述功能层上,所述第一金属层覆盖于所述栅极结构和所述功能层上,所述第一金属层分别与所述p+欧姆接触区、n型源区及所述多晶硅沟槽连接。

6、在本申请提供的半导体器件中,位于同一侧所述第一p+埋层与所述第二p+埋层相接触,以使所述第一p+埋层和所述第二p+埋层呈阶梯状设置。

7、在本申请提供的半导体器件中,所述第一p+埋层靠近所述p型基区的侧边在所述器件层上的正投影位于第二p+埋层在所述器件层上的正投影内。

8、在本申请提供的半导体器件中,所述p型埋层位于所述漂移区靠近所述功能层的一侧,所述p型埋层一侧边在所述功能层上的正投影位于所述p型基区上,或与所述p型基区和所述n型电流拓展区的交界平齐。

9、在本申请提供的半导体器件中,所述p型埋层另一侧边在所述器件层上的正投影位于所述第一p+埋层在所述器件层上的正投影和所述第二p+埋层在所述器件层上的正投影之间。

10、在本申请提供的半导体器件中,还包括第二金属层,所述第二金属层位于所述半导体衬底背向n型漂移区的一侧。

11、在本申请提供的半导体器件中,所述半导体衬底的材料为碳化硅。

12、在本申请提供的半导体器件中,两个所述第一p+埋层之间的间距为0.5um~4um。

13、在本申请提供的半导体器件中,两个所述p型埋层之间的间距为0.5um~4um。

14、第二方面,本申请提供了一种半导体器件的制造方法,上述的半导体器件由所述半导体器件的制造方法制成,所述半导体器件的制造方法包括:

15、提供一半导体衬底,并在在所述半导体衬底上形成n型漂移区,所述n型漂移区漂移区内设置有两个间隔设置的p型埋层;

16、在所述n型漂移区上形成功能层,所述功能层包括n型电流拓展区和两个设置于所述n型电流拓展区两侧的p型基区,所述p型基区内设置有相互连接的p+欧姆接触区和n型源区,所述n型电流拓展区内设置有多晶硅沟槽,所述多晶硅沟槽的底部设置有两个间隔设置的第一p+埋层、所述多晶硅沟槽的两侧设置有第二p+埋层;

17、在所述功能层上形成器件层,所述器件层包括栅极结构和第一金属层,所述栅极结构设置于所述功能层上,所述第一金属层覆盖于所述栅极结构和所述功能层上,所述第一金属层分别与所述p+欧姆接触区、n型源区及所述多晶硅沟槽连接。

18、综上,本申请提供的半导体器件包括半导体衬底、功能层和器件层,其中,所述半导体上设置有n型漂移区,所述n型漂移区漂移区内设置有两个间隔设置的p型埋层;所述功能层设置于所述n型漂移区上,所述功能层包括n型电流拓展区和两个设置于所述n型电流拓展区两侧的p型基区,所述p型基区内设置有相互连接的p+欧姆接触区和n型源区,所述n型电流拓展区内设置有多晶硅沟槽,所述多晶硅沟槽的底部设置有两个间隔设置的第一p+埋层、所述多晶硅沟槽的两侧设置有第二p+埋层;所述器件层包括栅极结构和第一金属层,所述栅极结构设置于所述功能层上,所述第一金属层覆盖于所述栅极结构和所述功能层上,所述第一金属层分别与所述p+欧姆接触区、n型源区及所述多晶硅沟槽连接。本方案可以通过在半导体器件的jfet区设置多晶硅沟槽,使多晶硅沟槽与半导体衬底形成异质结,从而在半导体器件反向导通时,有效降低导通压降,避免半导体器件的双极退化,进而提高半导体器件的可靠性。

技术特征:

1.一种半导体器件,其特征在于,包括

2.如权利要求1所述的半导体器件,其特征在于,位于同一侧的所述第一p+埋层与所述第二p+埋层相接触,以使位于同一侧的所述第一p+埋层和所述第二p+埋层呈阶梯状设置。

3.如权利要求2所述的半导体器件,其特征在于,所述第一p+埋层靠近所述p型基区的侧边在所述器件层上的正投影位于第二p+埋层在所述器件层上的正投影内。

4.如权利要求3所述的半导体器件,其特征在于,所述p型埋层位于所述漂移区靠近所述功能层的一侧,所述p型埋层一侧边在所述功能层上的正投影位于所述p型基区上,或与所述p型基区和所述n型电流拓展区的交界平齐。

5.如权利要求4所述的半导体器件,其特征在于,所述p型埋层另一侧边在所述器件层上的正投影位于所述第一p+埋层在所述器件层上的正投影和所述第二p+埋层在所述器件层上的正投影之间。

6.如权利要求1所述的半导体器件,其特征在于,还包括第二金属层,所述第二金属层位于所述半导体衬底背向n型漂移区的一侧。

7.如权利要求1-6任一项所述的半导体器件,其特征在于,所述半导体衬底的材料为碳化硅。

8.如权利要求1-6任一项所述的半导体器件,其特征在于,两个所述第一p+埋层之间的间距为0.5um~4um。

9.如权利要求1-6任一项所述的半导体器件,其特征在于,两个所述p型埋层之间的间距为0.5um~4um。

10.一种半导体器件的制造方法,其特征在于,权利要求1至9任一项所述半导体器件由所述半导体器件的制造方法制成,所述半导体器件的制造方法包括:

技术总结

本申请公开了一种半导体器件及其制造方法,该半导体器件包括半导体衬底、功能层和器件层,半导体上设置有N型漂移区,N型漂移区漂移区内设置有两个间隔设置的P型埋层;功能层设置于N型漂移区上,功能层包括N型电流拓展区和两个设置于N型电流拓展区两侧的P型基区,P型基区内设置有相互连接的P+欧姆接触区和N型源区,N型电流拓展区内设置有多晶硅沟槽,多晶硅沟槽的底部设置有两个间隔设置的第一P+埋层、多晶硅沟槽的两侧设置有第二P+埋层;器件层包括栅极结构和第一金属层,栅极结构设置于功能层上,第一金属层覆盖于栅极结构和功能层上,第一金属层分别与P+欧姆接触区、N型源区及多晶硅沟槽连接。本方案可以提高半导体器件的可靠性。

技术研发人员:李伟聪,陈钱,陈银

受保护的技术使用者:深圳市威兆半导体股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!