一种基于堆叠方式的封装结构及封装方法与流程

本申请涉及芯片封装,具体而言,涉及一种基于堆叠方式的封装结构及封装方法。

背景技术:

1、在集成电路中,实现各个功能的芯片需要通过封装实现电气连接和保护。qfn封装(quadflatno-leadpackage,方形扁平无引脚封装)因内部引脚与焊盘之间的导电路径短,自感系数以及封装体内部线电阻低,能够提供卓越的电性能而得到了广泛的应用。

2、现有技术中的qfn封装,主要过程为:将晶圆减薄至指定厚度,并切割为单颗;将单颗芯片贴装至框架上,通过焊线导通芯片与框架间信号;塑封整条产品,然后在框架正面印字;最后,将整条产品切割为单颗。但是,现有的qfn封装方法,无法同时实现fc(flip chip,倒装)封装和wb(wire bond,引线键合)。

技术实现思路

1、本申请的目的在于,针对上述现有技术中的不足,提供一种基于堆叠方式的封装结构及封装方法,其能够同时实现fc封装和wb封装。

2、为实现上述目的,本申请实施例采用的技术方案如下:

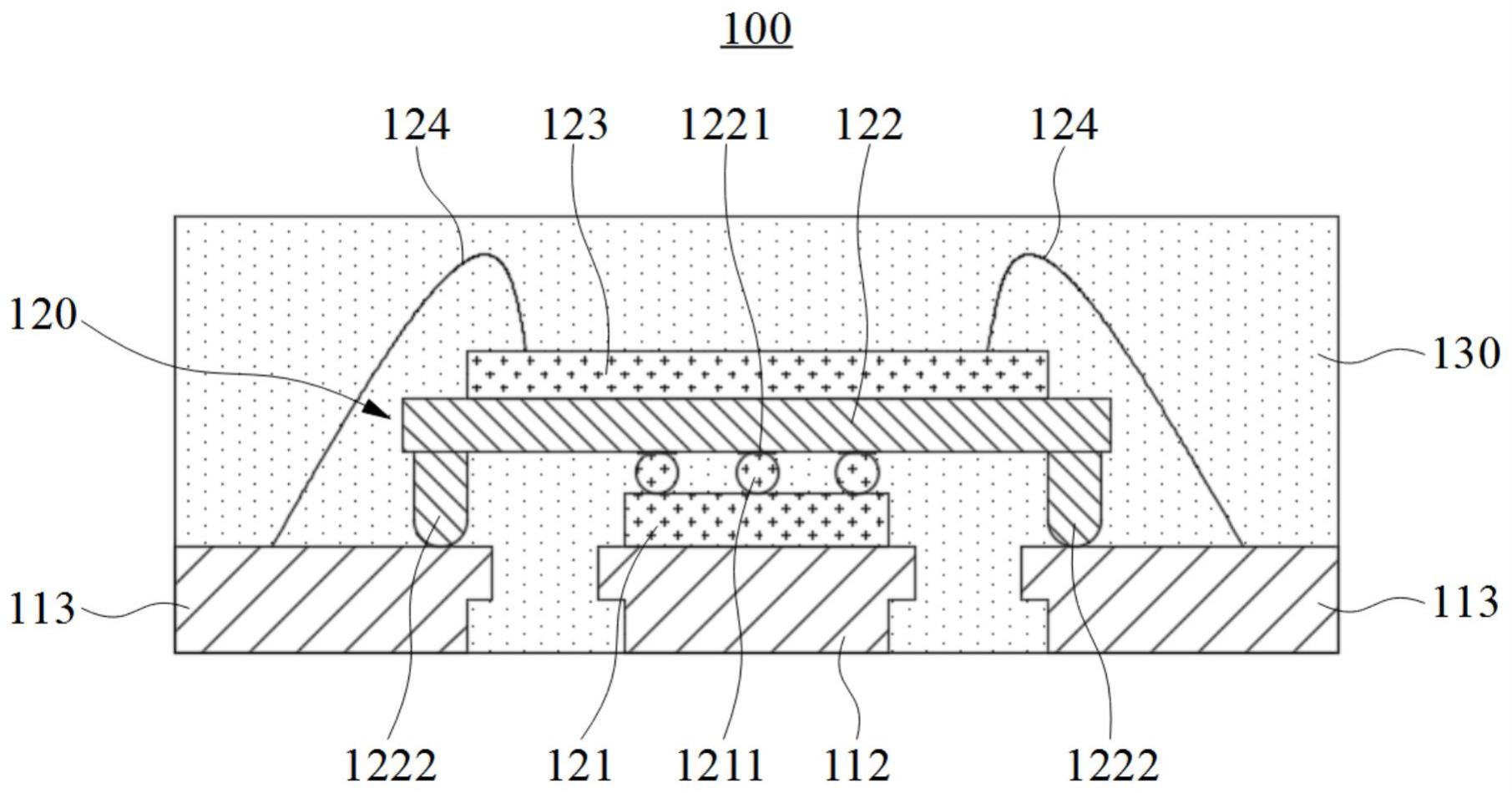

3、本申请实施例的一方面,提供一种基于堆叠方式的封装结构,包括:框架、集成芯片组件,以及包裹框架和集成芯片组件的塑封层;框架包括支撑框、设置在支撑框上的基岛和引脚,集成芯片组件包括依次层叠设置在基岛上的第一芯片、基板和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接。

4、可选地,基板上设有第二焊接凸块,基板通过第二焊接凸块与引脚电连接。

5、可选地,第一芯片为倒装芯片,第二芯片为引线键合芯片,第一芯片的表面设有第一焊接凸块,基板上设有与第一焊接凸块对应的开窗,第一焊接凸块固定在开窗内;或者,第一芯片为引线键合芯片,第二芯片为倒装芯片,第二芯片的表面设有第三焊接凸块,基板上设有与第三焊接凸块对应的开窗,第三焊接凸块固定在开窗内。

6、本申请实施例的另一方面,提供一种基于堆叠方式的封装方法,包括:提供框架,其中,框架包括支撑框、固定在支撑框上的基岛和引脚;在基岛上形成集成芯片组件,并使集成芯片组件的第一芯片和第二芯片分别与引脚电连接,其中,集成芯片组件包括基板和设置在基板相对的两侧的第一芯片和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接;将框架和集成芯片组件塑封,以形成包裹框架和集成芯片组件的塑封层。

7、可选地,在基岛上形成集成芯片组件,并使集成芯片组件的第一芯片和第二芯片分别与引脚电连接,其中,集成芯片组件包括基板和设置在基板相对的两侧的第一芯片和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接包括:提供表面具有第一焊接凸块的第一芯片,并将第一芯片正装在基岛上;提供表面具有第二焊接凸块和开窗的基板,并将基板倒装在框架上,以使第二焊接凸块与引脚连接,开窗与第一焊接凸块连接;提供第二芯片,并将第二芯片固定在基板上;采用引线将第二芯片与引脚连接。

8、可选地,在基岛上形成集成芯片组件,并使集成芯片组件的第一芯片和第二芯片分别与引脚电连接,其中,集成芯片组件包括基板和设置在基板相对的两侧的第一芯片和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接包括:提供表面具有第一焊接凸块的第一芯片和表面具有第二焊接凸块和开窗的基板,并将第一芯片倒装在基板上,以使第一焊接凸块与开窗连接;将基板倒装在框架上,以使第二焊接凸块与引脚连接;提供第二芯片,并将第二芯片固定在基板上;采用引线将第二芯片与引脚连接。

9、可选地,在基岛上形成集成芯片组件,并使集成芯片组件的第一芯片和第二芯片分别与引脚电连接,其中,集成芯片组件包括基板和设置在基板相对的两侧的第一芯片和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接包括:提供表面具有第一焊接凸块的第一芯片、表面具有第二焊接凸块和开窗的基板和第二芯片,并将第一芯片倒装在基板上,以使第一焊接凸块与开窗连接,将第二芯片固定在基板的另一表面;将基板倒装在框架上,以使第二焊接凸块与引脚连接;采用引线将第二芯片与引脚连接。

10、可选地,在基岛上形成集成芯片组件,并使集成芯片组件的第一芯片和第二芯片分别与引脚电连接,其中,集成芯片组件包括基板和设置在基板相对的两侧的第一芯片和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接包括:提供第一芯片,并将第一芯片固定在基板上,采用引线将第一芯片与引脚电连接;提供表面具有第二焊接凸块和开窗的基板,并将基板倒装在框架上,以使第二焊接凸块与引脚连接;提供表面具有第三焊接凸块的第二芯片,并将第二芯片倒装在基板上,以使第三焊接凸块与开窗连接。

11、可选地,在基岛上形成集成芯片组件,并使集成芯片组件的第一芯片和第二芯片分别与引脚电连接,其中,集成芯片组件包括基板和设置在基板相对的两侧的第一芯片和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接包括:提供第一芯片,并将第一芯片固定在基板上,采用引线将第一芯片与引脚电连接;提供表面具有第三焊接凸块的第二芯片和表面具有第二焊接凸块和开窗的基板,并将第二芯片倒装在基板上,以使第三焊接凸块与开窗连接;将基板安装在框架上,以使第二焊接凸块与引脚连接。

12、可选地,将框架和集成芯片组件塑封之后,还包括:切割框架和塑封层以得到封装成品。

13、本申请的有益效果包括:

14、本申请提供了一种基于堆叠方式的封装结构,包括:框架、集成芯片组件,以及包裹框架和集成芯片组件的塑封层;框架包括支撑框、设置在支撑框上的基岛和引脚,集成芯片组件包括依次层叠设置在基岛上的第一芯片、基板和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接。该基于堆叠方式的封装结构,通过中间层的基板,实现了芯片的双层封装以及qfn类产品的hybrid封装(fc封装+wb封装),扩展了框架类板材装片空间,并且第二芯片的装片空间不再受基岛大小的限制。同时,还能够利用基板将框架类产品难以传导的倒装芯片上错综复杂的信号传导至框架指定的引脚上,减小了第一芯片和第二芯片的连接距离,可以使用基板走线连接第一芯片和第二芯片,设计更复杂的第一芯片和第二芯片的互联线路。

技术特征:

1.一种基于堆叠方式的封装结构,其特征在于,包括:框架、集成芯片组件,以及包裹所述框架和所述集成芯片组件的塑封层;所述框架包括支撑框、设置在所述支撑框上的基岛和引脚,所述集成芯片组件包括依次层叠设置在所述基岛上的第一芯片、基板和第二芯片,所述第一芯片和所述第二芯片中的一者倒装在所述基板上并通过所述基板与所述引脚电连接、另一者通过引线与所述引脚电连接。

2.如权利要求1所述的基于堆叠方式的封装结构,其特征在于,所述第一芯片为倒装芯片,所述第二芯片为引线键合芯片,所述第一芯片的表面设有第一焊接凸块,所述基板上设有与所述第一焊接凸块对应的开窗,所述第一焊接凸块固定在所述开窗内;

3.如权利要求1所述的基于堆叠方式的封装结构,其特征在于,所述基板上设有第二焊接凸块,所述基板通过所述第二焊接凸块与所述引脚电连接。

4.一种基于堆叠方式的封装方法,其特征在于,包括:

5.如权利要求4所述的基于堆叠方式的封装方法,其特征在于,所述在所述基岛上形成集成芯片组件,并使所述集成芯片组件的第一芯片和第二芯片分别与所述引脚电连接,其中,所述集成芯片组件包括基板和设置在所述基板相对的两侧的所述第一芯片和所述第二芯片,所述第一芯片和所述第二芯片中的一者倒装在所述基板上并通过所述基板与所述引脚电连接、另一者通过引线与所述引脚电连接包括:

6.如权利要求4所述的基于堆叠方式的封装方法,其特征在于,所述在所述基岛上形成集成芯片组件,并使所述集成芯片组件的第一芯片和第二芯片分别与所述引脚电连接,其中,所述集成芯片组件包括基板和设置在所述基板相对的两侧的所述第一芯片和所述第二芯片,所述第一芯片和所述第二芯片中的一者倒装在所述基板上并通过所述基板与所述引脚电连接、另一者通过引线与所述引脚电连接包括:

7.如权利要求4所述的基于堆叠方式的封装方法,其特征在于,所述在所述基岛上形成集成芯片组件,并使所述集成芯片组件的第一芯片和第二芯片分别与所述引脚电连接,其中,所述集成芯片组件包括基板和设置在所述基板相对的两侧的所述第一芯片和所述第二芯片,所述第一芯片和所述第二芯片中的一者倒装在所述基板上并通过所述基板与所述引脚电连接、另一者通过引线与所述引脚电连接包括:

8.如权利要求4所述的基于堆叠方式的封装方法,其特征在于,所述在所述基岛上形成集成芯片组件,并使所述集成芯片组件的第一芯片和第二芯片分别与所述引脚电连接,其中,所述集成芯片组件包括基板和设置在所述基板相对的两侧的所述第一芯片和所述第二芯片,所述第一芯片和所述第二芯片中的一者倒装在所述基板上并通过所述基板与所述引脚电连接、另一者通过引线与所述引脚电连接包括:

9.如权利要求4所述的基于堆叠方式的封装方法,其特征在于,所述在所述基岛上形成集成芯片组件,并使所述集成芯片组件的第一芯片和第二芯片分别与所述引脚电连接,其中,所述集成芯片组件包括基板和设置在所述基板相对的两侧的所述第一芯片和所述第二芯片,所述第一芯片和所述第二芯片中的一者倒装在所述基板上并通过所述基板与所述引脚电连接、另一者通过引线与所述引脚电连接包括:

10.如权利要求4所述的基于堆叠方式的封装方法,其特征在于,所述将所述框架和所述集成芯片组件塑封之后,还包括:

技术总结

本申请提供一种基于堆叠方式的封装结构及封装方法,涉及芯片封装技术领域。该基于堆叠方式的封装结构包括:框架、集成芯片组件,以及包裹框架和集成芯片组件的塑封层;集成芯片组件包括依次层叠设置在基岛上的第一芯片、基板和第二芯片,第一芯片和第二芯片中的一者倒装在基板上并通过基板与引脚电连接、另一者通过引线与引脚电连接。该基于堆叠方式的封装结构实现了芯片的双层封装以及QFN类产品的FC封装和WB封装,且第二芯片的装片空间不再受基岛大小的限制。同时,还能够利用基板将倒装芯片上错综复杂的信号传导至框架指定的引脚上,还可以使用基板走线连接第一芯片和第二芯片,设计更复杂的第一芯片和第二芯片的互联线路。

技术研发人员:符镇涛,张超,张政,张粮佶,骆国臻

受保护的技术使用者:甬矽电子(宁波)股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!