一种碳化硅MOSFET器件及其制作方法与流程

本技术涉及半导体器件,特别是涉及一种碳化硅mosfet器件及其制作方法。

背景技术:

1、碳化硅因其禁带宽度大、高热导率、高击穿场强、高电子饱和速率以及强抗辐射性,使得碳化硅功率半导体器件能够应用于高温、高压、高频以及强辐射的工作环境下。

2、垂直形mosfet主要包括平面双注入型mosfet和沟槽型mosfet。其中,沟槽型mosfet器件不存在jfet区电阻且具有更高的元胞密度,因而被认为具有更广泛的应用前景。

3、但是,在沟槽型mosfet中,栅氧化层直接暴露于漂移区中,碳化硅外延层的sic介电常数是栅氧化层(sio2)介电常数的2.5倍。在阻断状态下,栅极沟槽底部的栅氧化层在没有达到外延层临界击穿电压时已经被提前击穿,由此造成器件可靠性下降。

4、发明专利公开号cn113764514a公开了一种sic mosfet器件及其制备方法,sicmosfet器件包括衬底、外延层、基层、源极金属层、栅极、栅介质层、沟道段、沟道长度减缩段、浮空段、连接层、源极和漏极。通过设置沟槽上部开口宽度大于其下部槽底的宽度,且沟槽的两侧斜侧壁与所述第一表面的槽侧夹角介于50°~70°,因此可以降低沟槽内栅介质层的缺陷密度,还可以提高沟槽的载流子迁移率,降低导通电阻。并且缩短了沟道长度,以降低栅氧的缺陷密度,还可以抵御ds极反向击穿电压的电场,有效减少了栅介质层承受的电场强度,起到保护栅介质层的作用,进一步避免栅介质层被提前击穿,并使得器件的击穿电压提高。其次,由于沟槽的两侧主要为基层,与栅极导电类型相同的基层可以进一步抵御ds极反向击穿电压的电场,保护栅介质层,提高器件的可靠性。

5、发明专利公开号cn114242768a公开了一种栅底电荷平衡改善的碳化硅mosfet器件及其制造方法,器件包括:具有电荷平衡柱的外延片结构、嵌埋式栅极结构、位于顶层的源极结构及位于底层的漏极结构,外延片结构的碳化硅外延层上形成有挖槽后的沟道顺从层。利用位于栅极结构两侧的接触沟槽,源极结构与外延片结构形成非平面的欧姆接触。利用位于栅极沟槽与接触沟槽下方的电荷平衡柱且基本由预置叠层阱所构成,以避免电荷平衡柱穿透到外延片结构的碳化硅衬底。通过具有规范栅底电荷平衡结的底部深度与外形受到比较好的截面柱形的效果,以解决在沟道顺从层的设置基础上导致电荷平衡结不能调整注入浓度与无法形成结侧柱形与结底深度随沟槽深度变化的电性能不稳定缺陷。

技术实现思路

1、基于此,有必要解决栅氧化层容易被击穿导致mosfet可靠性不高的技术问题,提供一种碳化硅mosfet器件。

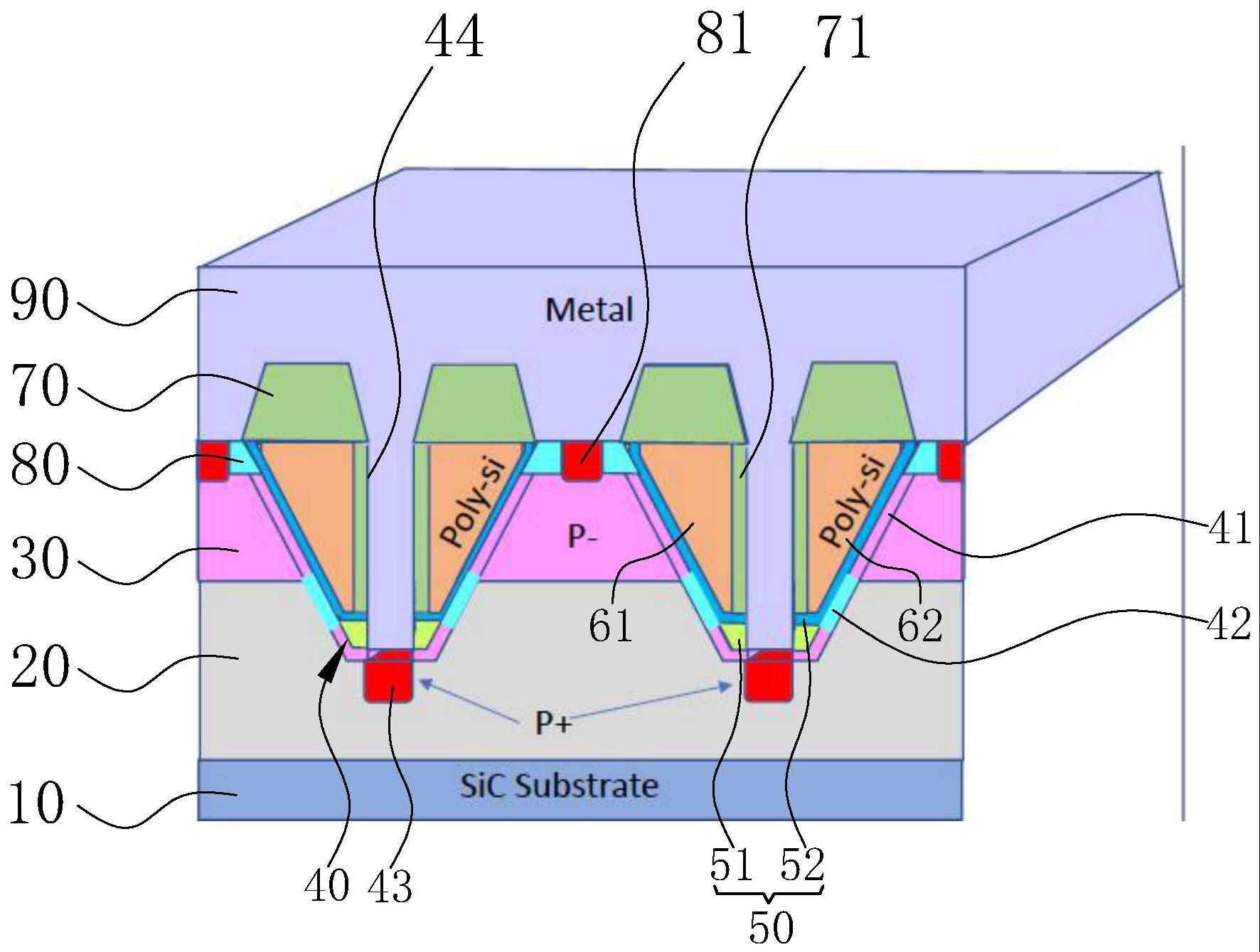

2、一种碳化硅mosfet器件,包括:

3、衬底;

4、碳化硅外延结构,设置于所述衬底上,所述碳化硅外延结构包括外延层与形成在所述外延层表面层的沟道体层,所述沟道体层的表面层还形成有在预定柵极之间的体隔离结,所述碳化硅外延结构内形成有栅极沟槽;

5、对应所述栅极沟槽内以源极接触孔将一个栅极分隔为相对的第一栅极填充体与第二栅极填充体,所述第一栅极填充体与所述第二栅极填充体分别设置于所述栅极沟槽内的相对两侧壁,所述源极接触孔位于所述第一栅极填充体与所述第二栅极填充体之间,所述外延层中通过所述源极接触孔的底部形成有栅隔离结,所述栅隔离结能形成屏蔽电场,以阻止电荷从栅极沟槽底部渗漏;

6、源极金属层,设置于所述碳化硅外延结构上,所述源极金属层还延伸填充于所述源极接触孔内并与所述栅隔离结接触,以降低所述栅隔离结的工作电位并增加所述源极金属层与所述碳化硅外延结构的机械结合。

7、通过采用上述技术方案,栅隔离结在外延层中为相对于mosfet的反向偏置,mosfet正常使用状态时,在外延层中栅隔离结的周边形成反向电压的耗尽层,其场势效应对栅氧化层起到屏蔽电场的作用,使得栅氧化层内的最大电场转移至耗尽层中,减小栅氧化层内的工作电场,从而降低栅氧化层被电场击穿的可能性。在此基础上,源极金属层与栅隔离结进一步形成接触,从而使得栅极沟槽底部的栅隔离结及栅氧化层与源极金属层的电压差降低,实现了栅极沟槽底部的零电位。此外,在漏极和源极反向加电压时,栅隔离结的周边与外延层之间的耗尽层为正向电压,栅极沟槽底部与侧边的栅氧化层不容易被高压电场击穿,从而提升了mosfet器件的可靠性;并且,在器件中对体隔离结与栅隔离结对源极金属层的金属半导体接触界面能形成良好有高度差的添附结合。

8、在其中一个实施例中,所述栅极沟槽的内壁上形成有栅极介质结构,所述栅极介质结构位于所述栅极沟槽底壁的第一部位厚度大于位于所述栅极沟槽侧壁的第二部位厚度。

9、通过采用上述技术方案,所述栅极介质结构位于栅极沟槽底壁的第一部位厚度大于所述栅极介质结构位于栅极沟槽侧壁(栅氧化层)的第二部位厚度,能够使得栅氧化层延伸到栅极沟槽底壁的部位承受更大的电压,难以被击穿,从而提高mosfet器件的可靠性。

10、在其中一个实施例中,所述栅极介质结构包括栅极介质层及形成在所述栅极介质层上的栅氧化层,所述栅极介质层设置于所述栅极沟槽的底壁上,所述栅氧化层形成于所述栅极介质层上,所述栅氧化层还形成于所述栅极沟槽的侧壁上。

11、在其中一个实施例中,所述碳化硅外延结构在所述栅极沟槽的底壁与侧壁还形成有沟槽顺从层,所述沟槽顺从层的离子掺杂类型与所述外延层相反,与所述沟道体层同极性相连。

12、在其中一个实施例中,所述沟槽顺从层在所述栅极沟槽靠近所述栅极沟槽底壁的侧边位置上还转置形成有反极型导接段,所述反极型导接段的离子掺杂类型与所述沟槽顺从层相反,用于修正所述沟道顺从层的沟道长度。

13、在其中一个实施例中,所述反极型导接段延伸通过所述外延层与所述沟道体层之间的界面。

14、在其中一个实施例中,所述沟道体层的表面层为体连接层,所述体隔离结贯穿所述体连接层并连接至所述沟道体层,所述源极金属层还接触所述体连接层与所述体隔离结。

15、在其中一个实施例中,所述碳化硅mosfet器件还包括层间膜,形成于所述第一栅极填充体与所述第二栅极填充体的上表面与内侧,以避免所述源极金属层直接接触至所述第一栅极填充体与所述第二栅极填充体。

16、本技术还提供一种碳化硅mosfet器件的制作方法,包括步骤:

17、s100,提供衬底,并设置碳化硅外延结构于所述衬底上,所述碳化硅外延结构包括外延层与形成在所述外延层表面层的沟道体层,所述沟道体层的表面层还形成有在预定柵极之间的体隔离结;

18、s200,图案化蚀刻所述碳化硅外延结构,以形成栅极沟槽;

19、s300,淀积形成栅极于所述栅极沟槽内;

20、s400,图案化蚀刻所述栅极,由在所述栅极沟槽中还形成有源极接触孔,所述源极接触孔能将所述栅极分隔为相对的第一栅极填充体及第二栅极填充体;

21、s500,通过所述源极接触孔,对所述碳化硅外延结构在所述源极接触孔的底部进行离子注入,以在所述外延层中形成栅隔离结;

22、s600,积淀生长源极金属层于所述碳化硅外延结构上,所述源极金属层与所述体隔离结接触,所述源极金属层还延伸填充于所述源极接触孔内并与所述栅隔离结接触,以降低所述栅隔离结的工作电位并增加所述源极金属层与所述碳化硅外延结构的机械结合。

23、在其中一个实施例中,在形成所述源极接触孔的步骤s400之后与在形成所述栅隔离结的步骤s500之前,该制作方法还包括:

24、s19,覆盖形成层间膜于所述第一栅极填充体及所述第二栅极填充体的上表面,所述层间膜还填充于所述源极接触孔内;

25、s20,图案化蚀刻所述层间膜,以使得所述源极接触孔内预留出所述源极金属层的填充位置,其中所述层间膜仍纵向地设置于所述源极接触孔内,以避免所述源极金属层直接接触所述第一栅极填充体与所述第二栅极填充体。

26、综上所述,本技术的碳化硅mosfet器件具有以下至少一种的有益技术效果:

27、1.在正常使用碳化硅mosfet器件时,栅隔离结与外延层的界面处于反向偏置状态,栅隔离结的周边形成耗尽层,从而对栅氧化层起到屏蔽电场的作用,使得栅氧化层内的最大电场转移至耗尽层中,减小栅氧化层内的工作电场,从而降低栅氧化层被电场击穿的可能性;

28、2.源极金属层的孔延伸部位与栅隔离结进一步形成电性接触,从而使得栅极沟槽底部的栅隔离结及栅氧化层与源极金属层的电压差降低,实现了栅极沟槽底部的零电位;栅极沟槽底部的栅氧化层不容易被高压电场击穿,从而提升了mosfet器件的可靠性;

29、3.栅极沟槽底部以栅极介质结构构成的绝缘厚层体结合栅隔离结能够降低栅极-漏极之间漏电流,减少器件应用开关损耗;

30、4. 栅极沟槽底部以栅极介质结构构成的绝缘厚层体结合栅隔离结能够降低米勒电容,从而使得mosfet器件能够提高开启速度,实现更高的开关频率;

31、5.栅极沟槽底部的栅隔离结与源极接触孔底部的源极金属层的延伸体直接相连而非悬空地呈“浮岛”式设计能够增加栅隔离结的稳定性,从而保证mosfet器件长期工作可靠性。

- 还没有人留言评论。精彩留言会获得点赞!