一种抑制表面漏电流的肖特基势垒二极管的制作方法

本发明涉及半导体功率器件,特别涉及一种抑制表面漏电流的肖特基势垒二极管。

背景技术:

1、目前功率半导体器件的主要研究和发展方向是小型化、大容量、高频化、高效节能、高可靠性和低成本。

2、肖特基势垒二极管(sbd)不是利用p型半导体与n型半导体接触形成pn结原理制作的,而是利用金属与半导体接触形成的金属-半导体结原理制作的,是一种热载流子二极管。但是由于sbd的反向势垒较薄,且在其表面极易发生电子迁移,造成表面漏电流偏大,反向击穿不稳定,所以提高肖特基势垒二极管表面可靠性是市场应用需求之一。

技术实现思路

1、本申请通过提供一种抑制表面漏电流的肖特基势垒二极管,解决了现有技术中常规肖特基势垒二极管反向击穿不稳定的问题,实现了更好的抑制表面漏电流的能力,能有效解决反向击穿不稳定的问题,提高产品可靠性。

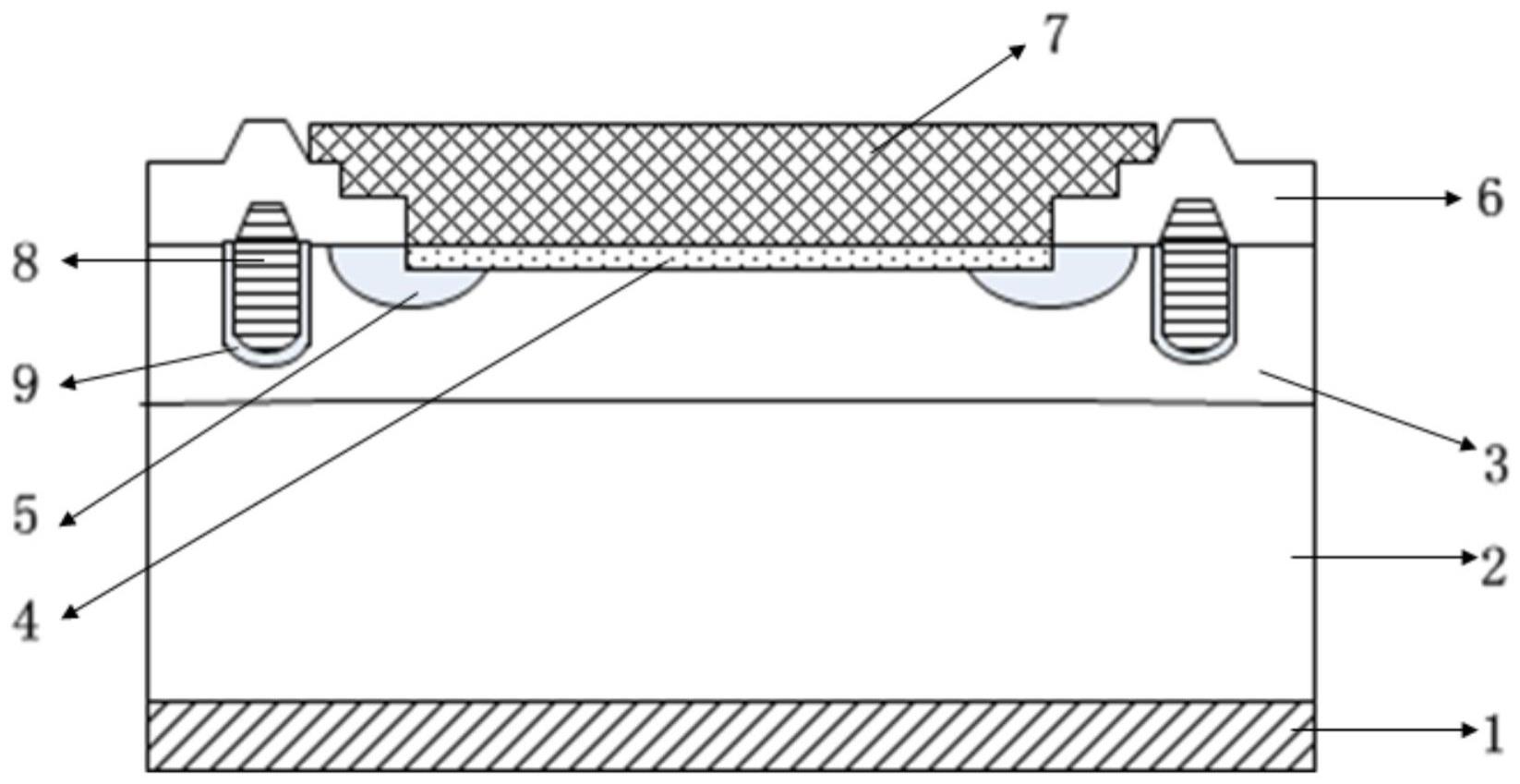

2、本申请实施例提供了一种抑制表面漏电流的肖特基势垒二极管,包括:

3、n-型硅衬底;

4、n-型外延层,设置于所述n-型硅衬底上方;

5、p+保护环,所述p+保护环设置于所述n-型外延层主表面;

6、势垒金属层,所述势垒金属层设置于所述n-型外延层主表面,且所述势垒金属层设置于所述p+保护环的环内;

7、沟槽型电容,所述沟槽型电容设置于所述n-型外延层主表面,且设置于所述p+保护环的外侧,所述沟槽型电容与所述p+保护环无接触;

8、二氧化硅层,所述二氧化硅层设置于所述势垒金属层外侧,且所述二氧化硅层设置于所述沟槽型电容上方;

9、正面金属层,所述正面金属层设置于所述势垒金属层上方;

10、背面金属层,所述背面金属层设置于所述n-型硅衬底下方。

11、上述实施例的有益效果在于:该肖特基二极管主要通过p+保护环的设置增加对电场集中点的抗性,提高芯片抗击穿能力,同时由于p+保护环表面浓度高,可一定程度上抑制表面电子的迁移性;同时在p+保护环外侧增加沟槽型电容 ,从而在肖特基二极管芯片生产过程中因钝化层质量差、沾污或表面处理不净导致出现表面可动电子增多,在电场作用下在外延层上表面发生迁移形成微弱的表面漏电时,可断绝漏电通道,即使电子聚集也无法形成电流,实现了更好的抑制表面漏电流的能力,能有效解决反向击穿不稳定的问题,提高产品可靠性。

12、在上述实施例基础上,本申请可进一步改进,具体如下:

13、在本申请其中一个实施例中,所述n-型外延层主表面开设有沟槽,所述沟槽设置于所述p+保护环的外侧,所述沟槽型电容包括设置于所述沟槽槽壁的绝缘层和填充于所述绝缘层之中的多晶硅填充物,所述多晶硅填充物延伸至所述绝缘层上方。通过绝缘层和多晶硅填充物断绝漏电通道,同时多晶硅填充物顶部高于绝缘层,可降低多晶硅刻蚀时对绝缘层造成损伤。

14、在本申请其中一个实施例中,所述多晶硅填充物上端部的截面呈上短下长的梯形。生产过程中二氧化硅层顶部和多晶硅填充物顶部形状一致,肖特基二极管的正面金属层边缘在p+保护环外侧,所以金属层边缘会延伸至二氧化硅层的凸出部分,梯形结构能够有效保证正面金属层在侧面的良好覆盖,极大的增加正面金属加工余量;另外,若二氧化硅层顶部呈现为弧形或方行凸起,金属易在台阶处出现断裂,导致有效金属场版宽度减小,而二氧化硅层顶部呈现为梯形可有效避免上述情况。

15、在本申请其中一个实施例中,所述沟槽深度为3μm~6μm。沟槽深度可根据外延厚度进行调整,需大于等于3μm。

16、在本申请其中一个实施例中,所述沟槽内径大于等于1μm。沟槽内径根据版图设计余量进行设计,最低1μm。

17、在本申请其中一个实施例中,所述沟槽的内径从上至下逐渐减小或保持一致。

18、在本申请其中一个实施例中,所述绝缘层厚度大于等于0.3μm。

19、在本申请其中一个实施例中,所述多晶硅填充物需进行ph扩散处理。从而降低多晶硅的电阻率。

20、本申请实施例还提供了一种上述沟槽型电容的结构制备方法,包括以下步骤:

21、s1:在所述n-型外延层的表面制备氧化层;

22、s2:通过光刻,打开沟槽环区窗口;

23、s3:干法刻蚀制得所述沟槽;

24、s4:制备所述绝缘层;

25、s5:多晶硅填充;

26、s6:刻蚀所述多晶硅填充物,保证所述氧化层表面所述多晶硅刻蚀后无剩余;

27、s7:光刻,在所述多晶硅填充物上保留胶条,胶条宽度小于所述多晶硅填充物环宽,其余位置打开;

28、s8:刻蚀所述多晶硅填充物和绝缘层,使所述多晶硅填充物顶部呈现上短下长的梯形结构,超出所述n-型外延层表面的所述绝缘层可适当保留或全部去除。

29、在本申请其中一个实施例中,所述步骤s5中,所述多晶硅填充至所述绝缘层之间无空洞且填充最低点高于所述氧化层的高度。

30、本申请实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

31、1.该肖特基二极管主要通过p+保护环的设置增加对电场集中点的抗性,提高芯片抗击穿能力,同时由于p+保护环表面浓度高,可一定程度上抑制表面电子的迁移性;同时在p+保护环外侧增加沟槽型电容 ,实现了更好的抑制表面漏电流的能力,能有效解决反向击穿不稳定的问题,提高产品可靠性;

32、2.该肖特基二极管通过绝缘层和多晶硅填充物构成的沟槽型电容断绝漏电通道,同时多晶硅填充物顶部高于绝缘层,可降低多晶硅刻蚀时对绝缘层造成损伤;

33、3.该肖特基二极管中二氧化硅层顶部呈梯形结构,由于肖特基二极管的正面金属层边缘在p+保护环外侧,所以金属层边缘会延伸至二氧化硅层的凸出部分,梯形结构能够有效保证正面金属层在侧面的良好覆盖,极大的增加正面金属加工余量;另外,若二氧化硅层顶部呈现为弧形或方行凸起,金属易在台阶处出现断裂,导致有效金属场版宽度减小,而二氧化硅层顶部呈现为梯形可有效避免上述情况。

技术特征:

1.一种抑制表面漏电流的肖特基势垒二极管,其特征在于,包括:

2.根据权利要求1所述的肖特基势垒二极管,其特征在于:所述n-型外延层主表面开设有沟槽,所述沟槽设置于所述p+保护环的外侧,所述沟槽型电容包括设置于所述沟槽槽壁的绝缘层和填充于所述绝缘层之中的多晶硅填充物,所述多晶硅填充物延伸至所述绝缘层上方。

3.根据权利要求2所述的肖特基势垒二极管,其特征在于:所述多晶硅填充物上端部的截面呈上短下长的梯形。

4.根据权利要求2所述的肖特基势垒二极管,其特征在于:所述沟槽深度为3μm~6μm。

5.根据权利要求4所述的肖特基势垒二极管,其特征在于:所述沟槽内径大于等于1μm。

6.根据权利要求5所述的肖特基势垒二极管,其特征在于:所述沟槽的内径从上至下逐渐减小或保持一致。

7.根据权利要求6所述的肖特基势垒二极管,其特征在于:所述绝缘层厚度大于等于0.3μm。

8.根据权利要求2所述的肖特基势垒二极管,其特征在于:所述多晶硅填充物需进行ph扩散处理。

9.一种如权利要求2-8任一所述的沟槽型电容的结构制备方法,包括以下步骤:

10.根据权利要求9所述的结构制备方法,其特征在于:所述步骤s5中,所述多晶硅填充至所述绝缘层之间无空洞且填充最低点高于所述氧化层的高度。

技术总结

本发明公开了半导体功率器件技术领域内的一种抑制表面漏电流的肖特基势垒二极管,包括:N‑型硅衬底;N‑型外延层,设置于N‑型硅衬底上方;P+保护环,设置于N‑型外延层主表面;势垒金属层,设置于N‑型外延层主表面,且势垒金属层设置于P+保护环的环内;沟槽型电容,设置于N‑型外延层主表面,且设置于P+保护环的外侧,沟槽型电容与P+保护环无接触;二氧化硅层,设置于势垒金属层外侧,且二氧化硅层设置于沟槽型电容上方;正面金属层,设置于势垒金属层上方;背面金属层,设置于N‑型硅衬底下方。该肖特基势垒二极管实现了更好的抑制表面漏电流的能力,能有效解决反向击穿不稳定的问题,提高产品可靠性。

技术研发人员:徐婷,董文俊,李浩,齐露露

受保护的技术使用者:扬州国宇电子有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!