一种高压隔离类集成电路封装结构的制作方法

本发明涉及集成电路封装及芯片,尤其涉及一种高压隔离类集成电路封装结构。

背景技术:

1、在对集成电路进行高压隔离测试时,常常存在着输入端和输出端打火放电的问题。造成这一问题的主要原因在于:在对集成电路仅进行高压测试时,在集成电路的输入端和输出端间会产生高压,高压产生的电流可进一步沿着封装体表面流经另一端;由于目前常见的集成电路封装体通常为整体面结构,受封装体宽度限制,爬电(creepage distance)距离有限,从而导致集成电路的输入端和输出端短路。

2、集成电路封装体越宽可增加爬电距离,但是封装体变大后,封装成本会急剧增加,而且安装通用性会变差。而增加集成电路引线框架的低压端基岛和高压端基岛的距离虽然可以提升高低压端的固体绝缘耐压,但是无法改变延塑封体表面的爬电距离。因此,随着高压隔离类集成电路应用领域的不断扩大和需求的不断增加,隔离耐压的提高已经成为了一个重要的研究方向。

技术实现思路

1、本发明旨在提供一种高压隔离类集成电路封装结构,以克服现有技术中存在的不足。

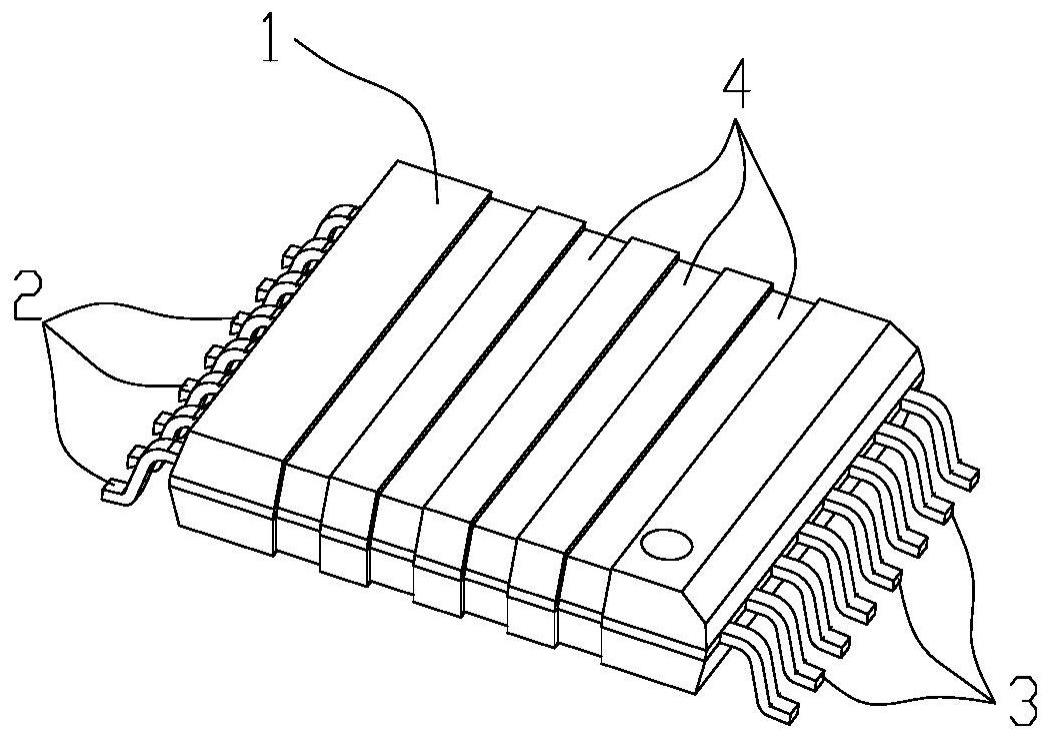

2、为解决上述技术问题,本发明的技术方案是:一种高压隔离类集成电路封装结构,包括封装体、输入端引脚、输出端引脚,所述输入端引脚与输出端引脚设于封装体的两侧,所述封装体表面设有多个下凹的凹槽或者凸出封装体表面的凸条,多个所述凹槽或者凸条沿封装体长度方向阵列排布,并绕封装体表面环形设置,且所述凹槽、凸条设置在垂直于输入端引脚和输出端引脚的方向上。

3、进一步的,上述的高压隔离类集成电路封装结构,所述封装体内部设有与输入端引脚连接的输入端基岛、与输出端引脚连接的输出端基岛,所述输入端基岛与输出端基岛之间设有间隙,所述间隙根据耐压需求和封装体塑封料的介电强度设定,其关系式为:h=aumax/eb,

4、其中:h为基岛间隙;umax为隔离耐压峰值;a为安全系数;eb为封装体塑封料介电强度,介电强度按交流电峰值测量。

5、进一步的,上述的高压隔离类集成电路封装结构,所述封装体的塑封料为介电强度和cti值高的高耐压塑封料。

6、进一步的,上述的高压隔离类集成电路封装结构,所述输入端基岛和输出端基岛上设有芯片,所述芯片通过焊线与输入端基岛、输出端基岛连接,所述芯片的表面设有隔离部,所述隔离部至少设置在芯片正面、芯片背面、芯片四周侧中的一个位置。

7、进一步的,上述的高压隔离类集成电路封装结构,所述隔离部为绝缘材料制成。

8、进一步的,上述的高压隔离类集成电路封装结构,所述隔离部的厚度2μm-20μm。

9、进一步的,上述的高压隔离类集成电路封装结构,所述隔离部为隔离圈和/或者隔离平面,所述隔离圈为闭环的环形结构,所述隔离平面为局部隔离的块平面结构;且所有的所述隔离圈、隔离平面的厚度相同。

10、进一步的,上述的高压隔离类集成电路封装结构,所述芯片的四周侧设有密封环,设于芯片四周侧的所述隔离部沿密封环外侧设置。

11、与现有技术相比,本发明的有益效果是:在同比相同封装体宽度下可增加集成电路的隔离耐压,有效降低对集成电路进行高压隔离测试的失败率,提高产品通过率。

技术特征:

1.一种高压隔离类集成电路封装结构,其特征在于:包括封装体(1)、输入端引脚(2)、输出端引脚(3),所述输入端引脚(2)与输出端引脚(3)设于封装体(1)的两侧,所述封装体(1)表面设有多个下凹的凹槽(4)或者凸出封装体(1)表面的凸条(5),多个所述凹槽(4)或者凸条(5)沿封装体(1)长度方向阵列排布,并绕封装体(1)表面环形设置,且所述凹槽(4)、凸条(5)设置在垂直于输入端引脚(2)和输出端引脚(5)的方向上。

2.根据权利要求1所述的高压隔离类集成电路封装结构,其特征在于:所述封装体(1)内部设有与输入端引脚(2)连接的输入端基岛(8)、与输出端引脚(3)连接的输出端基岛(9),所述输入端基岛(8)与输出端基岛(9)之间设有间隙(11),所述间隙(11)根据耐压需求和封装体(1)塑封料的介电强度设定,其关系式为:

3.根据权利要求1所述的高压隔离类集成电路封装结构,其特征在于:所述封装体(1)的塑封料为介电强度和cti值高的高耐压塑封料。

4.根据权利要求2所述的高压隔离类集成电路封装结构,其特征在于:所述输入端基岛(8)和输出端基岛(9)上设有芯片(10),所述芯片(10)通过焊线(12)与输入端基岛(8)、输出端基岛(9)连接,所述芯片(10)的表面设有隔离部(14),所述隔离部(41)至少设置在芯片(10)正面、芯片(10)背面、芯片(10)四周侧中的一个位置。

5.根据权利要求4所述的高压隔离类集成电路封装结构,其特征在于:所述隔离部(14)为绝缘材料制成。

6.根据权利要求4所述的高压隔离类集成电路封装结构,其特征在于:所述隔离部(14)的厚度为2μm-20μm。

7.根据权利要求4所述的高压隔离类集成电路封装结构,其特征在于:所述隔离部(14)为隔离圈和/或者隔离平面,所述隔离圈为闭环的环形结构,所述隔离平面为局部隔离的块平面结构;且所有的所述隔离圈、隔离平面的厚度相同。

8.根据权利要求7所述的高压隔离类集成电路封装结构,其特征在于:所述芯片(10)的四周侧设有密封环(13),设于芯片(10)四周侧的所述隔离部(14)沿密封环(13)外侧设置。

技术总结

本发明提供一种高压隔离类集成电路封装结构,包括封装体、输入端引脚、输出端引脚,所述输入端引脚与输出端引脚设于封装体的两侧,所述封装体表面设有多个下凹的凹槽或者凸出封装体表面的凸条,多个所述凹槽或者凸条沿封装体长度方向阵列排布,并绕封装体表面环形设置,且所述凹槽、凸条设置在垂直于输入端引脚和输出端引脚的方向上;所述封装体内部的芯片的表面设有隔离耐压的隔离部。本发明在同比相同封装体宽度下可提高集成电路的隔离耐压性能,有效降低对集成电路进行高压隔离测试的失败率,提高产品通过率。

技术研发人员:崔卫兵,郑永富,邓旭东,张进兵,孙亚丽

受保护的技术使用者:天水华天科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!