一种沟道处理方法及存储介质与流程

本发明属于微电子,尤其涉及一种沟道处理方法及存储介质。

背景技术:

1、 逐渐缩小的工艺节点,使得静态随机存储器sram(static radom accessmemory)存储单元的失配(mismatch)特性成为关注的焦点;由于失配问题会影响存储器件读取过程的稳定性,还会影响写入过程的冗余度(margin),也即危害到了相关器件的良率;基于此,sram,尤其是40nm节点及以下的制程,亟需克服上述技术问题。

2、如图1至图4所示,给出了相关技术中,实测的数据;而图7则给出了相关技术中的沟道结构;其中,第四沟槽结构040很可能因为较差的一致性及上述失配问题导致相关器件存在难以接受的漏电现象和较低的良率。

技术实现思路

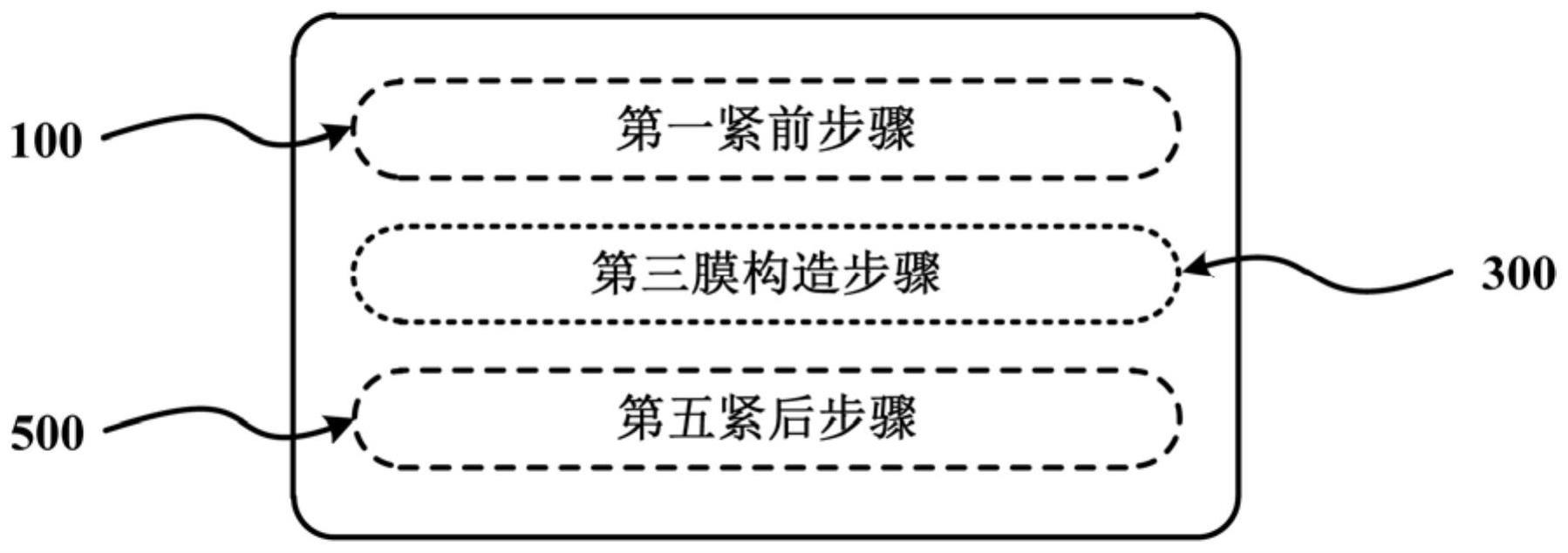

1、本发明实施例公开了一种沟道处理方法,包括第三膜构造步骤;该第三膜构造步骤位于第一紧前步骤之后;其第一紧前步骤提前构造有沟槽隔离结构,该沟槽隔离结构包括第一基底层、第二介质层、第三介质层;其第二介质层构造于第一基底层靠近沟槽隔离结构槽口一侧;其第三介质层构造于第二介质层外远离第一基底层一侧;其沟槽隔离结构的槽结构贯穿其第三介质层及第二介质层并在其第一基底层形成预设深度的第一沟槽。

2、其中,第三膜构造步骤在其沟槽隔离结构表面内缩后形成第二槽口台阶结构,该第二槽口台阶结构和/或沟槽隔离结构表层构造有第五膜结构,用以改善工件的表面特性和相关物理特征。

3、 具体地,其沟槽隔离结构的空间结构可按照浅沟槽隔离sti(shallow trenchisolation)结构对高宽比har(high aspect ratio)阈值的要求进行构造。

4、其中,第二介质层可以是第二氧化物层;该第二氧化物层可由第一基底层氧化后获得。具体地,其第一基底层可采用硅材料制备;其第二介质层的材料可以是硅氧化物。

5、其中,第三膜构造步骤可采用去耦合等离子氮化dpn过程构造出第五膜结构。

6、具体地,其第三介质层可采用氮化物构造;其第五膜结构可通过调整预设的厚度,用于缓冲沟槽隔离结构高宽比制程harp产生的应力。

7、对于一些应用,其沟槽隔离结构的临界尺寸ocd或特征尺寸可以是不小于40nm的,其第五膜结构氧化层的厚度预设值或目标值可选择17å。

8、此外,还可通过第五紧后步骤完成功能单元或电路部分的构造;其中,第三膜构造步骤介于第一紧前步骤和第五紧后步骤之间;该第五紧后步骤用于构造沟槽隔离结构预设的功能电路和/或单元,其功能电路和/或单元的临界尺寸或特征尺寸不小于沟槽隔离结构对应的临界尺寸或特征尺寸。

9、相应地,本发明实施例还公开了一种存储介质,包括第五膜结构;该第五膜结构构造于预设的沟槽隔离结构和/或该沟槽隔离结构表面内缩后形成的第二槽口台阶结构之上;其中,该沟槽隔离结构包括第一基底层、第二介质层、第三介质层;其第二介质层构造于第一基底层靠近沟槽隔离结构槽口一侧;其第三介质层构造于第二介质层外远离第一基底层一侧;其沟槽隔离结构的槽结构贯穿第三介质层及第二介质层并在其第一基底层上形成预设深度的第一沟槽。

10、具体地,其沟槽隔离结构的空间结构可按照浅沟槽隔离sti结构对高宽比har阈值的要求进行制备,用以满足相应的物理隔离或线路设置需要。

11、其中,第二介质层可以是第二氧化物层;其第二氧化物层可由第一基底层氧化后获得。具体地,其第一基底层可采用硅材料制备;其第二介质层的材料可以是硅氧化物。

12、其中,第五膜结构可采用去耦合等离子氮化dpn过程构造;其第三介质层可采用氮化物构造;其第五膜结构可通过调整预设的厚度,用于缓冲沟槽隔离结构高宽比制程harp产生的应力。

13、具体地,其沟槽隔离结构的临界尺寸ocd或特征尺寸可以选择不小于40nm的设置,其第五膜结构氧化层的厚度预设值或目标值可以选择17å的设置。

14、进一步地,该存储介质还可制备有静态存储器sdram单元;该静态存储器sdram单元构造于沟槽隔离结构之上,该静态存储器sdram单元的临界尺寸或特征尺寸可选择不小于沟槽隔离结构对应的临界尺寸或特征尺寸。

15、 综上,本发明于紧前的沟槽成型步骤形成基础拓扑即沟槽隔离结构,于内缩pb(pull back)的沟槽上进一步构造处置层的介质结构,即第五膜结构;进而可结合沟槽隔离结构的物理特征,例如浅沟槽隔离结构sti(shallow trench isolation),生成功能单元,又如存储介质。

16、 其中,其第五膜结构可采用去耦合等离子氮化工艺dpn(decoupled plasmanitridation)来构造,该结构可有效缓冲高宽比制程harp(high ratio process)在沟道产生的应力,亦可确保特定载流子的迁移率;其方法可有效改善静态随机存储器sram(staticrandom access memory)的失配(mismatch)特性,提升器件的一致性(uniformity)、减少漏电并提升产品良率;在实施中,其方法和产品的制备无须添置新的步骤,可在原制程上灵活升级。

17、需要说明的是,在本文中采用的“第一”、“第二”等类似的语汇,仅仅是为了描述技术方案中的各组成要素,并不构成对技术方案的限定,也不能理解为对相应要素重要性的指示或暗示;带有“第一”、“第二”等类似语汇的要素,表示在对应技术方案中,该要素至少包含一个。

技术特征:

1.一种沟道处理方法,其特征在于,包括第三膜构造步骤(300);所述第三膜构造步骤(300)位于第一紧前步骤(100)之后;所述第一紧前步骤(100)构造有沟槽隔离结构(111),所述沟槽隔离结构(111)包括第一基底层(010)、第二介质层(020)、第三介质层(030);所述第二介质层(020)构造于所述第一基底层(010)靠近所述沟槽隔离结构(111)槽口一侧;所述第三介质层(030)构造于所述第二介质层(020)外远离所述第一基底层(010)一侧;所述沟槽隔离结构(111)的槽结构贯穿所述第三介质层(030)及所述第二介质层(020)并在所述第一基底层(010)形成预设深度的第一沟槽(101);其中,所述第三膜构造步骤(300)在所述沟槽隔离结构(111)表面内缩后形成第二槽口台阶结构(222),所述第二槽口台阶结构(222)和/或所述沟槽隔离结构(111)表层构造有第五膜结构(050)。

2.如权利要求1所述的沟道处理方法,其中:所述沟槽隔离结构(111)的空间结构符合浅沟槽隔离sti结构对高宽比har阈值的要求。

3.如权利要求1或2所述的沟道处理方法,其中:所述第二介质层(020)为第二氧化物层;所述第二氧化物层由所述第一基底层(010)氧化后获得。

4.如权利要求3所述的沟道处理方法,其中:所述第一基底层(010)采用硅材料制备;所述第二介质层(020)的材料包括硅氧化物。

5.如权利要求1、2或4中任一项所述的沟道处理方法,其中:所述第三膜构造步骤(300)采用去耦合等离子氮化dpn过程构造出所述第五膜结构(050)。

6.如权利要求5所述的沟道处理方法,其中:所述第三介质层(030)采用氮化物构造;所述第五膜结构(050)调整预设的厚度,并用于缓冲所述沟槽隔离结构(111)高宽比制程harp产生的应力。

7.如权利要求1、2、4、6任一项所述的沟道处理方法,其中:所述沟槽隔离结构(111)的临界尺寸ocd或特征尺寸不小于40nm,所述第五膜结构(050)氧化层的厚度预设值或目标值包括17å。

8.如权利要求7所述的沟道处理方法,还包括第五紧后步骤(500);所述第三膜构造步骤(300)介于所述第一紧前步骤(100)和所述第五紧后步骤(500)之间;所述第五紧后步骤(500)用于构造所述沟槽隔离结构(111)预设的功能电路和/或单元,所述功能电路和/或所述单元的所述临界尺寸或所述特征尺寸不小于所述沟槽隔离结构(111)对应的所述临界尺寸或所述特征尺寸。

9.一种存储介质,包括第五膜结构(050);所述第五膜结构(050)构造于预设的沟槽隔离结构(111)和/或所述沟槽隔离结构(111)表面内缩后形成第二槽口台阶结构(222)之上;其中,所述沟槽隔离结构(111)包括第一基底层(010)、第二介质层(020)、第三介质层(030);所述第二介质层(020)构造于所述第一基底层(010)靠近所述沟槽隔离结构(111)槽口一侧;所述第三介质层(030)构造于所述第二介质层(020)外远离所述第一基底层(010)一侧;所述沟槽隔离结构(111)的槽结构贯穿所述第三介质层(030)及所述第二介质层(020)并在所述第一基底层(010)形成预设深度的第一沟槽(101)。

10.如权利要求9所述的存储介质,其中:所述沟槽隔离结构(111)的空间结构符合浅沟槽隔离sti结构对高宽比har阈值的要求。

11.如权利要求9或10所述的存储介质,其中:所述第二介质层(020)为第二氧化物层;所述第二氧化物层由所述第一基底层(010)氧化后获得。

12.如权利要求11所述的存储介质,其中:所述第一基底层(010)采用硅材料制备;所述第二介质层(020)的材料包括硅氧化物。

13.如权利要求9、10或12中任一项所述的存储介质,其中:所述第五膜结构(050)采用去耦合等离子氮化dpn过程构造。

14.如权利要求13所述的存储介质,其中:所述第三介质层(030)采用氮化物构造;所述第五膜结构(050)调整预设的厚度,并用于缓冲所述沟槽隔离结构(111)高宽比制程harp产生的应力。

15.如权利要求9、10、12、14任一项所述的存储介质,其中:所述沟槽隔离结构(111)的临界尺寸ocd或特征尺寸不小于40nm,所述第五膜结构(050)氧化层的厚度预设值或目标值包括17å。

16.如权利要求15所述的存储介质,还包静态存储器sdram单元;所述静态存储器sdram单元构造于所述沟槽隔离结构(111)之上,所述静态存储器sdram单元的所述临界尺寸或所述特征尺寸不小于所述沟槽隔离结构(111)对应的所述临界尺寸或所述特征尺寸。

技术总结

本发明属于微电子技术领域,尤其涉及一种沟道处理方法及存储介质;于紧前的沟槽成型步骤形成基础拓扑即沟槽隔离结构(111),于内缩PB(Pull Back)的沟槽上进一步构造处置层的介质结构,即第五膜结构(050);进而可结合沟槽隔离结构(111)的物理特征,例如浅沟槽隔离结构STI(Shallow Trench Isolation),生成功能单元,又如存储介质;其中,第五膜结构(050)可采用去耦合等离子氮化工艺DPN(Decoupled Plasma Nitridation)来构造,可有效缓冲高宽比制程HARP(High Ratio Process)在沟道产生的应力,亦可确保特定载流子的迁移率;其方法可有效改善静态随机存储器SRAM(Static Random Access Memory)的失配(Mismatch)特性,提升器件的一致性(Uniformity)、减少漏电并提升产品良率;其方法及产品的制备无须添置步骤,可在原制程上灵活升级。

技术研发人员:杨欣,郭振强,黄鹏,孙少俊

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!