一种三维集成电路的制作方法

本申请涉及半导体器件,具体地,涉及一种三维集成电路。

背景技术:

1、电子产品目前正在朝小型化、高密度化、高可靠性、低功耗方向发展,使得芯片也的发展方向也是小型化、高密度化、高可靠性、低功耗。为了缩小芯片尺寸,业界发明了多层芯片堆叠封装技术。

2、开始时,堆叠封装是把多个芯片裸片堆叠放置在一起,把芯片之间的信号通过键合(bonding)技术连结,组成内部的完整系统,再把外部信号通过封装引脚外连,最后封装成为一个完整芯片。

3、后来,业界发明了硅通孔(tsv)技术,堆叠的芯片裸片之间的信号是通过tsv连接,形成了更加紧凑的多芯片堆叠封装芯片。这种3d封装芯片是在封装阶段通过多层芯片裸片堆叠封装形成的,从芯片制造角度看,这种3d封装芯片只能看作是伪3d芯片。

4、3d封装芯片存在如下缺陷:

5、1、减薄技术面临的主要挑战是超薄化工艺所要求的<50um的减薄能力,没有支撑的减薄硅片在组装后会发生严重的翘曲,与基板之间的互连(微凸点)上会产生较大的残余应力,从而导致器件结构的可靠性问题。

6、2、因为cu易于氧化并在高温下容易形成各种氧化物(cuo和cu2o),需要高真空度和高洁净度的cu-cu混合键合工艺。

7、3、不同芯片裸晶在封装过程中的对准精度较低,封装过程之中,裸晶可能会有位移,导致钻孔或脚位没对准,布线和互连间距受覆盖精度的影响被限制在几个微米。intel最先进的qmc工艺的pitch为3um,因此键合的i/o数目受到pitch的限制,无法再提高集成度。

8、4、3d封装由大量不同的材料组成,这些材料具有不同的材料特性,如热膨胀系数(cte)、热导率、电导率及弹性模量等,这会在芯片上产生巨大的热-机械力,并导致芯片与封装相互作用(cpi),从而发生低k值电介质材料开裂、金属结构脱落等现象。另外,封装自身可能也会发生严重翘曲,从而增加了额外的应力,尤其是对于面积较大的封装。

9、因此,传统的3d封装芯片不能适应芯片的发展方向,急需真正的3d芯片,是本领域技术人员急需要解决的技术问题。

10、在背景技术中公开的上述信息仅用于加强对本申请的背景的理解,因此其可能包含没有形成为本领域普通技术人员所知晓的现有技术的信息。

技术实现思路

1、本申请实施例提供了一种三维集成电路,以解决传统的3d封装芯片不能适应芯片的发展方向的技术问题。

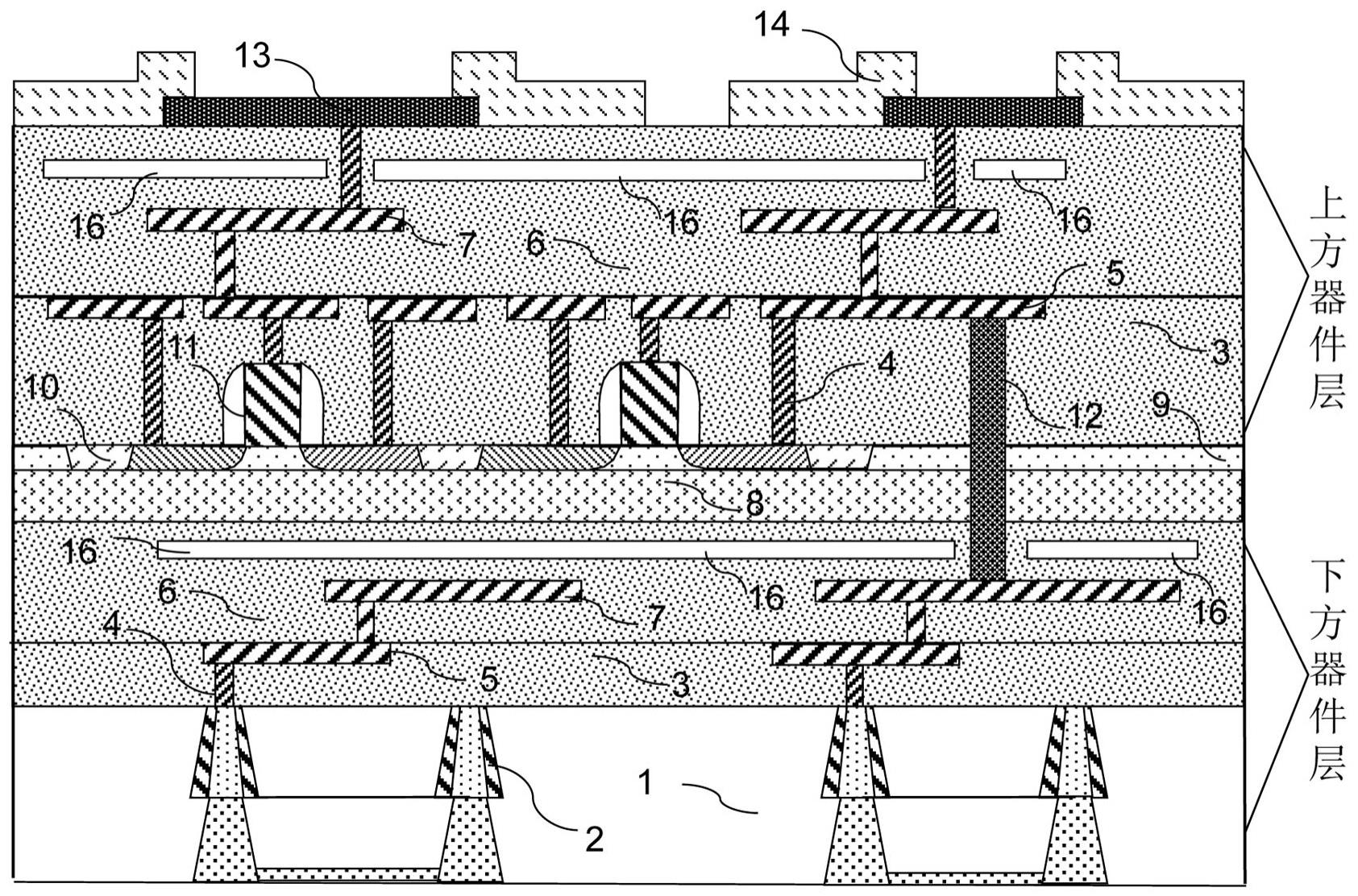

2、本申请实施例提供了一种三维集成电路,包括:

3、下方器件层;所述下方器件层包括下方器件层本体和退火阻挡层,所述退火阻挡层位于所述下方器件层本体内的上部,且所述退火阻挡层避开竖向通孔以不与竖向通孔连接;

4、形成在下方器件层上方的上方器件层;

5、其中,所述下方器件层的退火阻挡层用于阻挡上方器件层制备过程中退火工艺的光对所述下方器件层退火阻挡层之下的结构进行加热。

6、本申请实施例由于采用以上技术方案,具有以下技术效果:

7、本申请实施例的三维集成电路,包括自下而上设置的下方器件层和上方器件层。其中,下方器件层包括下方器件层本体和退火阻挡层,退火阻挡层位于所述下方器件层本体内的上部。在制备本申请实施例的三维集成电路时,先制备下方器件层,再制备上方器件层。由于下方器件层本体中退火阻挡层存在,在上方器件层制备过程中退火工艺的光产生的大量热量,会被下方器件层的退火阻挡层阻挡,将热量限制在下方器件层的退火阻挡层位置,使得热量不会对已经制备好的下方器件层退火阻挡层之下的结构进行加热,避免了下方器件层烧毁,使得能够制备出本申请实施例的三维集成电路。本申请实施例的三维集成电路,通过下方器件层本体内的上部设置退火阻挡层,使得在下方器件层上方再形成上方器件层的同时,对下方器件层本体的结构进行保护,从而实现了在垂向方向形成多层器件层,为实现真正的3d芯片提供了结构基础。

技术特征:

1.一种三维集成电路,其特征在于,包括:

2.根据权利要求1所述的三维集成电路,其特征在于,还包括:

3.根据权利要求2所述的三维集成电路,其特征在于,所述下方器件层本体包括自下而上设置的下方半导体层、下方功能器件层、下方绝缘层;其中,所述下方绝缘层中具有与下方功能器件层的功能器件连接的电连接结构;

4.根据权利要求3所述的三维集成电路,其特征在于,所述下方器件层的退火阻挡层遮盖所述下方功能器件层的功能器件的金属硅化物区域、低熔点金属区域;其中,所述低熔点金属区域熔点低于上方器件层制备过程中退火工艺的退火温度;

5.根据权利要求3所述的三维集成电路,其特征在于,所述下方器件层的退火阻挡层遮盖所述下方功能器件层的功能器件。

6.根据权利要求4或5所述的三维集成电路,其特征在于,所述下方器件层为底部器件层;所述底部器件层包括自下而上设置的底部衬底、底部功能器件层、底部绝缘层;其中,所述底部绝缘层中具有与底部功能器件层的功能器件连接的电连接结构;

7.根据权利要求6所述的三维集成电路,其特征在于,三维集成电路还包括:

8.根据权利要求1所述的三维集成电路,其特征在于,所述退火阻挡层为高比热容材料的退火阻挡层;所述退火阻挡层比热容的取值范围为大于等于0.1kj/kg.摄氏度小于等于3.5kj/kg.摄氏度;

9.根据权利要求7所述的三维集成电路,其特征在于,所述第一半导体层具有贯穿所述第一半导体层的器件隔离,器件隔离包围在第一功能器件层的功能器件的外侧;

10.根据权利要求9所述的三维集成电路,其特征在于,第h半导体层为第h薄硅层;所述第h薄硅层厚度的取值范围为大于等于2纳米小于等于220纳米,h遍取从1到n;

11.根据权利要求10所述的三维集成电路,其特征在于,在形成第一功能器件层的功能器件过程中的离子注入后的退火工艺和消除应力的退火工艺中,采用低热预算闪光毫秒退火工艺,低热预算闪光毫秒退火工艺退火温度的取值范围为大于等于750°c小于等于1200°c;

12.根据权利要求9所述的三维集成电路,其特征在于,所述底部器件层还包括:

13.根据权利要求12所述的三维集成电路,其特征在于,所述底部绝缘层包括自下而上设置的氧化物绝缘层和低介电常数绝缘层;

14.根据权利要求13所述的三维集成电路,其特征在于,形成在第一功能器件层的功能器件的源极和漏极中需要设置竖向钨通孔的位置的欧姆接触。

15.根据权利要求14所述的三维集成电路,其特征在于,所述第一绝缘层包括自下而上设置的氧化硅绝缘层和低介电常数绝缘层;

16.根据权利要求15所述的三维集成电路,其特征在于,所述底部器件层的退火阻挡层位于所述底部绝缘层的低介电常数绝缘层内,且位于所述底部绝缘层中低介电常数绝缘层的金属互连线的高度之上。

17.根据权利要求16所述的三维集成电路,其特征在于,所述上方第一器件层的退火阻挡层位于所述第一绝缘层的低介电常数绝缘层内,且位于所述第一绝缘层中低介电常数绝缘层的金属互连线的高度之上;

18.根据权利要求17所述的三维集成电路,其特征在于,所述三维集成电路为分布式一体化存算芯片,对应的:

19.根据权利要求18所述的三维集成电路,其特征在于,逻辑电路层的多个计算单元分布式均匀排列;第一存储电路层、第二存储电路层、……、第n存储电路层各自的存储单元分布式均匀排列。

技术总结

本申请实施例提供了一种三维集成电路,包括:下方器件层;所述下方器件层包括下方器件层本体和退火阻挡层,所述退火阻挡层位于所述下方器件层本体内的上部,且所述退火阻挡层避开竖向通孔以不与竖向通孔连接;形成在下方器件层上方的上方器件层;其中,所述下方器件层的退火阻挡层用于阻挡上方器件层制备过程中退火工艺的光对所述下方器件层退火阻挡层之下的结构进行加热。本申请实施例解决了传统的3D封装芯片不能适应芯片的发展方向的技术问题。

技术研发人员:岳丹诚,张耀辉

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!