具有高沟道密度强短路能力的SiC功率半导体器件的制作方法

本发明涉及一种功率半导体器件,尤其是一种具有高沟道密度强短路能力的sic功率半导体器件。

背景技术:

1、碳化硅(sic)作为第三代宽禁带材料,具有禁带宽度大、临界击穿电场高、热导率高、载流子饱和速度高等优点,在功率器件领域倍受青睐。

2、碳化硅金属氧化物场效应晶体管(mosfet)在功率器件中表现优异,由于碳化硅材料具备的高临界击穿电场的特性,sic mosfet器件能够实现10倍与si mosfet器件的耐压,接近1/300的漂移区电阻,具备明显的应用优势。此外,碳化硅金属氧化物场效应晶体管(mosfet)不仅具有sic材料阻断电压高、工作结温高、抗辐照能力强等特点,同时具有易于驱动、控制简单、工作频率高、开关损耗小等优点,是应用于电机驱动、高端储能、电力电子变压器等领域的理想开关器件之一,具有广阔的发展前景。

3、在sic mosfet器件在制造过程中,由于栅氧化层底部会形成较多的界面态,致使沟道迁移率较低,沟道电阻大。因此,提升器件性能的关键因素之一为降低沟道电阻,常见的优化方式分别为通过工艺优化提高沟道迁移率,以及通过结构设计实现更高密度的沟道,后者更加具备兼容性和普适性。与此同时,通过结构设计实现高密度沟道时,将引入可靠性能力及短路能力下降的问题,如何实现高导通性能、高可靠性以及强短路能力的sicmosfet器件是如今从业人员需要思考的问题。

4、为实现sic mosfet器件的高沟道密度,以提升器件导通性能,现有技术中,往往采用如下两种方式:1)、采用缩小元胞尺寸的方式,此时,每个单位面积中的沟道变多,器件的沟道密度提升,进而提高sic mosfet器件的导通性能;2)、通过采用方形、六角等密集排布方式,此种排布方式可增加沟道密度。

5、上述缩小元胞和密集排布都可增加沟道的密度,但沟道的饱和电流上升,导致短路工况下流经器件的电流迅速上升,引起器件的短路能力下降。此外,往更小的元胞尺寸设计时,工艺的难度更大,同时对工艺的控制能力和设备的加工能力提出更高要求。在采用密集排布时,jfet区不呈现为均匀的条形结构,此时,反向耐压会使得电场更加集中,电场的集中会导致栅极可靠性下降的问题。

技术实现思路

1、本发明的目的是克服现有技术中存在的不足,提供一种具有高沟道密度强短路能力的sic功率半导体器件,其具有高沟道密度以及强短路能力,降低电场集中效应,提高功率半导体器件栅极的可靠性。

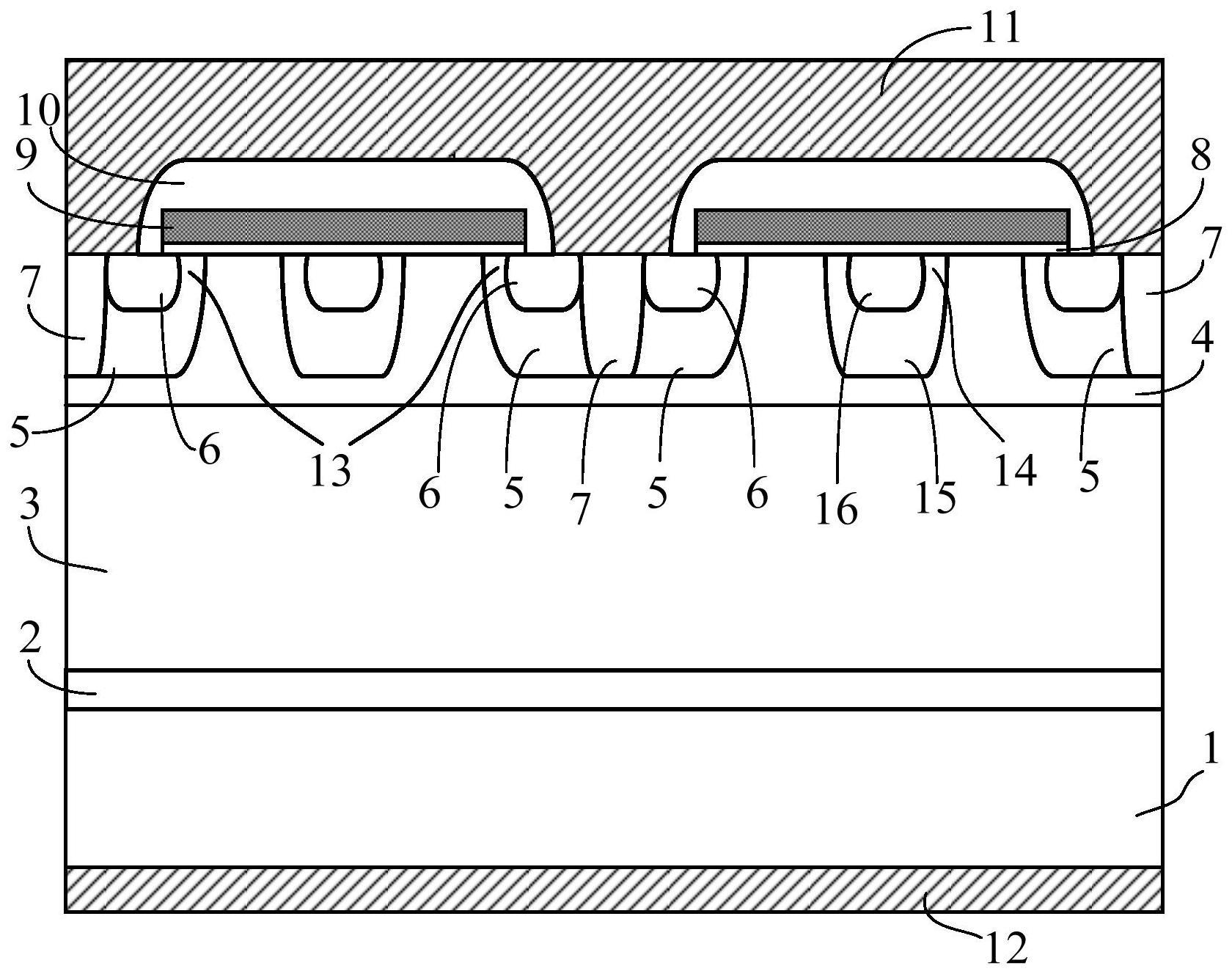

2、按照本发明提供的技术方案,所述具有高沟道密度强短路能力的sic功率半导体器件,包括具有第一导电类型的sic基板以及制备于所述sic基板中心区的有源区;所述有源区内包括若干并列分布的平面型元胞;

3、对任一平面型元胞,包括位于所述有源区内的第一类导电沟道;

4、在有源区内,还包括用于增加沟道密度的第二类导电沟道,其中,

5、第一类导电沟道、第二类导电沟道均与sic基板上方的正面第一电极金属欧姆接触,以利用第一类导电沟道以及第二类导电沟道同时形成功率半导体器件导通的电流通道;

6、第二类导电沟道的饱和电流小于第一类导电沟道的饱和电流,以利用第二类导电沟道降低所在功率半导体器件在短路工况下的饱和电流。

7、第二类导电沟道的沟道长度与第一类导电沟道的沟道长度相一致;

8、对第一类导电沟道,包括位于sic基板内的第一类导电沟道第二导电类型阱区,对第二类导电沟道,包括位于sic基板内的第二类导电沟道第二导电类型阱区,其中,

9、在功率半导体器件的截面上,第二类导电沟道第二导电类型阱区的横向宽度小于第一类导电沟道第二导电类型阱区的横向宽度。

10、对平面型元胞,还包括平面栅单元,其中,

11、在所述功率半导体器件的截面上,平面栅单元包括设置于sic基板上的栅极绝缘层以及设置于所述栅极绝缘层上的栅极导电多晶硅,栅极导电多晶硅的端部均与对应的第一类导电沟道交叠;

12、对第一类导电沟道,还包括位于第一类导电沟道第二导电类型阱区内的第一类导电沟道第二导电类型重掺杂区以及分布于所述第一类导电沟道第二导电类型重掺杂区内两侧的第一类导电沟道第一导电类型源区,第一类导电沟道第一导电类型源区与第一类导电沟道第二导电类型重掺杂区接触;

13、对与栅极导电多晶硅端部对应的第一类导电沟道,所述第一类导电沟道内的第一类导电沟道第二导电类型阱区以及第一类导电沟道第一导电类型源区与栅极绝缘层接触。

14、对第二类导电沟道,包括设置于第二类导电沟道第二导电类型阱区内的第二类导电沟道第一导电类型源区,其中,

15、第二类导电沟道第二导电类型阱区通过sic基板内的第一导电类型轻掺杂区与第一类导电沟道第二导电类型阱区间隔。

16、正面第一电极金属通过第二类导电沟道接触孔与第二类导电沟道第一导电类型源区欧姆接触,其中,

17、填充在第二类导电沟道接触孔内的正面第一电极金属还与第二类导电沟道第二导电类型重掺杂区欧姆接触,所述第二类导电沟道第二导电类型重掺杂区与第二类导电沟道接触孔对应的第二类导电沟道第一导电类型源区接触;

18、第二类导电沟道第二导电类型阱区与第一类导电沟道第二导电类型阱区具有相同的结深。

19、在有源区内,平面型元胞的排布形状包括方形、六角形或品字形,其中,

20、第一类导电沟道第二导电类型阱区以及第二类导电沟道第二导电类型阱区在有源区内形成的二维分布状态,所形成的二维分布状态包括与条形适配的分布状态。

21、在有源区内,所有第二类导电沟道内的第二类导电沟道第一导电类型源区相互连接成一体,或者,

22、所有的第二类导电沟道第一导电类型源区通过正面第一电极金属连接成等电位状态。

23、在功率半导体器件的纵向方向上,第二类导电沟道第一导电类型源区上部的掺杂浓度大于第二类导电沟道第一导电类型源区其余区域的掺杂浓度,和/或,

24、在功率半导体器件的横向方向上,第二类导电沟道第一导电类型源区内包括若干空缺区,和/或,所述第二类导电沟道第一导电类型源区的掺杂浓度呈非均匀变化状态。

25、在功率半导体器件的纵向方向上,第一类导电沟道第一导电类型源区上部的掺杂浓度大于第一类导电沟道第一导电类型源区其余区域的掺杂浓度,和/或,

26、在功率半导体器件的横向方向上,对第一类导电沟道第一导电类型源区内包括若干空缺区,和/或,所述第一类导电沟道第一导电类型源区的掺杂浓度呈非均匀变化状态。

27、在有源区内,还包括第二导电类型注入区,其中,

28、第二导电类型注入区位于第一类导电沟道的外,且位于第二类导电沟道第一导电类型源区内;

29、第二导电类型注入区与第二类导电沟道第一导电类型源区接触,且与正面第一电极金属欧姆接触。

30、所述“第一导电类型”和“第二导电类型”两者中,对于n型sic功率半导体器件,第一导电类型指n型,第二导电类型为p型;对于p型sic功率半导体器件,第一导电类型与第二导电类型所指的类型与n型功率半导体器件正好相反。

31、本发明的优点:利用设置于有源区内的第二类导电沟道,可提升有源区内的沟道密度,在有源区内同时设置第一类导电沟道以及第二类导电沟道后,在保持功率半导体器件导通效率的情况下,有效降低沟道电阻,并可降低电场集中效率,提高栅极的可靠性;

32、第二类导电沟道的饱和电流小于第一类导电沟道的饱和电流,在短路工况下,利用第二类导电沟道可降低整个功率半导体器件的饱和电流,提高功率半导体器件的短路能力。

- 还没有人留言评论。精彩留言会获得点赞!