一种碳化硅超级结MOSFET结构及其制备方法

本发明属于半导体器件,具体涉及一种碳化硅超级结mosfet结构及其制备方法。

背景技术:

1、与硅(si)相比,宽带隙半导体材料碳化硅(sic)具有优越的电学性能,从而在电力电子领域受到了越来越多的关注。基于4h-sic的单极功率器件已被广泛用于高功率密度、高温和高临界电场等环境中,其中典型代表便是金属氧化物半导体场效应晶体管(mosfet)。然而,比导通电阻和击穿电压间的折衷关系限制了硅基以及碳化硅基功率器件的进一步发展。超级结(superjunction,简称:sj)结构可称为突破极限的里程碑式创新。sj结构将p型掺杂引入漂移区,促成了传统器件中单一的阻性耐压层向结型耐压层的转变,借助二维电场调制效应实现了击穿电压和导通电阻间更好的折衷关系,进而打破材料一维极限。硅基超结器件已经在技术和商业上有所实现。

2、而在实践方面,相较si材料而言,sic材料杂质扩散系数小和硬度高等稳定的化学和物理特性,为sic基超级结器件的制备增添了诸多困难。因此在现有工艺条件下,通过合理的结构设计及优化,在sic中实现理想的超级结性能是一个有价值的研究方向。

技术实现思路

1、本发明的目的在于克服上述现有技术不足之处而提供一种碳化硅超级结mosfet结构及其制备方法。

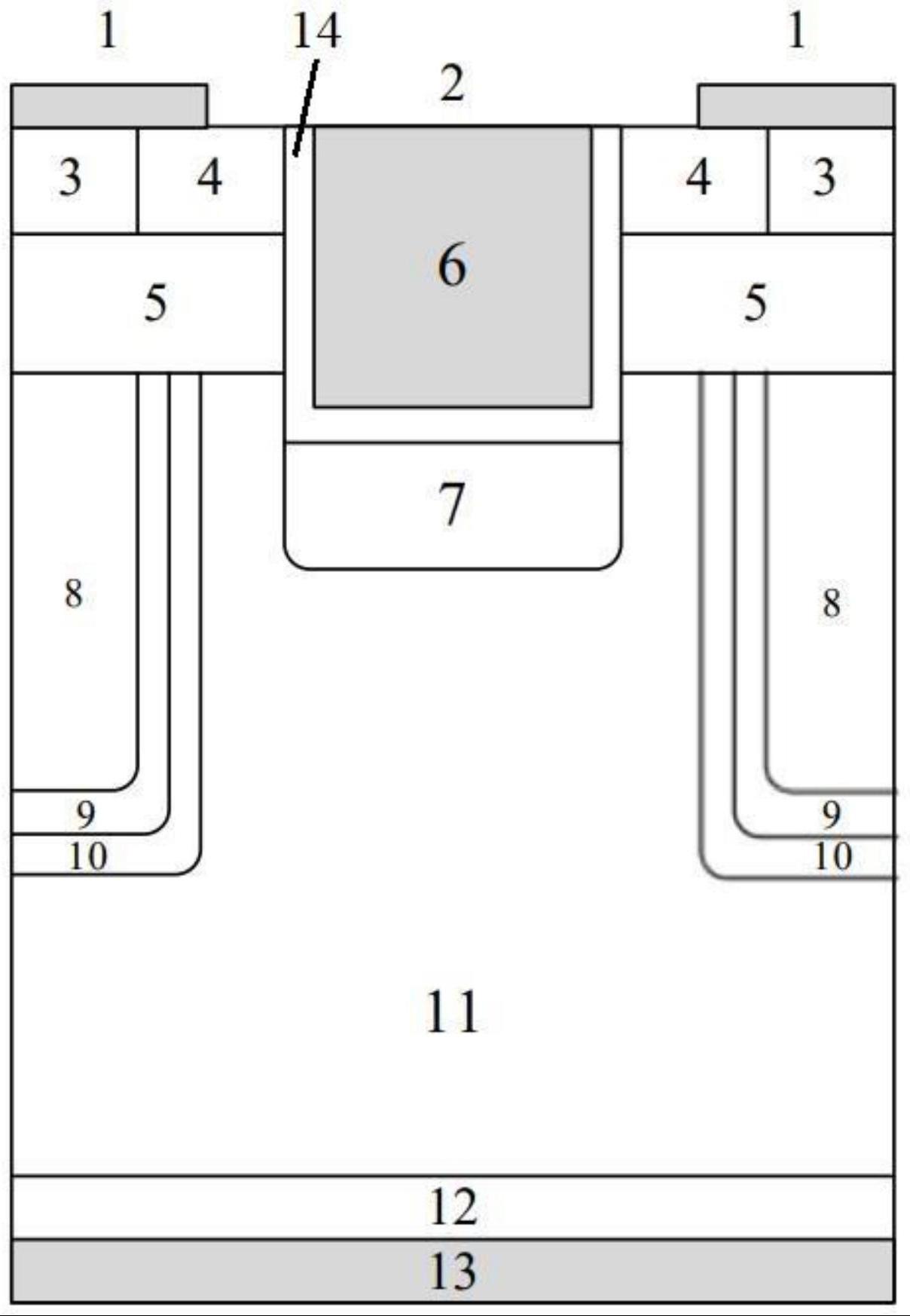

2、为实现上述目的,本发明提供了一种碳化硅超级结mosfet结构,包括:

3、漏极;

4、第一导电类型衬底,位于所述漏极的上表面;

5、第一导电类型外延层,位于所述第一导电类型衬底的上表面;

6、第二导电类型阱区,位于所述第一导电类型外延层内;

7、第一导电类型源区和第二导电类型源区,并排设置于所述第二导电类型阱区的上表面;

8、第二导电类型柱区,位于所述第一导电类型外延层内且上表面和所述第二导电类型阱区的底面相重合;

9、第二导电类型重掺杂区,位于所述第二导电类型柱区的底面和侧壁且上表面和所述第二导电类型阱区的底面相重合;

10、第一导电类型重掺杂区,位于所述第二导电类型重掺杂区的底面和侧壁且上表面和所述第二导电类型阱区的底面相重合;

11、栅极结构,所述栅极结构与所述第一导电类型外延层接触设置;

12、源极,位于所述第一导电类型源区部分上表面和所述第二导电类型源区上表面。

13、进一步的,所述栅极结构为沟槽栅,包括:

14、沟槽栅,位于所述第一导电类型外延层、第二导电类型阱区和第一导电类型源区中;

15、栅氧化介质层,位于所述栅沟槽内侧表面;

16、多晶硅栅极,位于所述栅氧化介质层内。

17、进一步的,还包括:位于所述第一导电类型外延层内的第二导电类型埋岛区,所述第二导电类型埋岛区的上表面和所述栅氧化介质层的底面相重合。

18、进一步的,所述栅极结构为平面栅,包括形成于所述第一导电类型外延层顶部表面上的栅氧化介质层,以及位于所述栅氧化介质层上表面的多晶硅栅极。

19、进一步的,还包括jfet区,所述jfet区的掺杂浓度高于所述第一导电类型外延层。

20、进一步的,所述第二导电类型阱区位于所述第二导电类型源区和所述第一导电类型源区的底面和所述第一导电类型源区的侧壁,且所述第二导电类型阱区的侧壁和所述jfet区相接触。

21、进一步的,所述第二导电类型柱区和所述第一导电类型外延层通过第一导电类型重掺杂区和第二导电类型重掺杂区隔离。

22、进一步的,所述第一导电类型外延层、第一导电类型重掺杂区、第二导电类型重掺杂区以及第二导电类型柱区横向排列,形成超级结结构。

23、进一步的,所述第一导电类型重掺杂区或所述第二导电类型重掺杂区和所述第二导电类型柱区的宽度比为1:3-1:6。

24、进一步的,所述第二导电类型重掺杂区或所述第一导电类型重掺杂区的深度大于所述第二导电类型柱区的深度,且深度差小于1.5μm。

25、进一步的,所述第一导电类型重掺杂区的深度大于所述第二导电类型重掺杂区的深度,且深度差小于0.8μm。

26、进一步的,所述第一导电类型重掺杂区或所述第二导电类型重掺杂区的掺杂浓度高于所述第二导电类型柱区或所述第一导电类型外延层的掺杂浓度。

27、进一步的,所述第一导电类型重掺杂区或所述第二导电类型重掺杂区的掺杂浓度和所述第二导电类型柱区的掺杂浓度比为1.5:1-4:1。

28、进一步的,所述第二导电类型阱区的掺杂浓度为5e17-8e17cm-3,所述第一导电类型源区和第二导电类型源区的掺杂浓度为1e19-5e19cm-3,所述第二导电类型埋岛区的掺杂浓度为5e15-8e15cm-3,所述第一导电类型衬底的掺杂浓度为1e19-5e19cm-3。

29、进一步的,所述第二导电类型阱区的深度为0.6-0.7μm,所述第一导电类型源区和第二导电类型源区的深度为0.3-0.5μm,所述第二导电类型埋岛区的深度为0.3-0.5μm。

30、进一步的,所述第一导电类型为n型,所述第二导电类型为p型。

31、本发明还提供了一种碳化硅超级结mosfet结构的制备方法,包括:

32、提供第一导电类型衬底;

33、在所述第一导电类型衬底上通过外延生长形成第一导电类型外延层;

34、在所述第一导电类型外延层中,通过离子注入技术,形成第一导电类型重掺杂区;

35、在所述第一导电类型重掺杂区中,通过离子注入技术,形成第二导电类型重掺杂区;

36、在所述第二导电类型重掺杂区中,通过离子注入技术,形成第二导电类型柱区;

37、采用离子注入技术,在所述第一导电类型外延层中形成第二导电类型阱区;

38、采用离子注入技术,在所述第一导电类型外延层中形成并排的第一导电类型源区和第二导电类型源区;

39、在所述第一导电类型外延层中间位置形成栅极结构;

40、在第一导电类型衬底背面形成漏极;

41、在第一导电类型源区部分上表面和第二导电类型源区上表面形成源极。

42、进一步的,所述栅极结构为沟槽栅,所述沟槽栅的形成步骤为对所述第一导电类型外延层的顶部进行刻蚀形成沟槽,并在所述沟槽中氧化形成栅氧化介质层,在所述沟槽中填充多晶硅形成多晶硅栅极。

43、进一步的,还包括:采用离子注入技术,在第一导电类型外延层中间位置形成埋岛区。

44、进一步的,所述栅极结构为平面栅,所述平面栅的形成步骤为于所述第一导电类型外延层的顶部通过氧化形成栅氧化介质层,并在所述栅氧化介质层顶部淀积多晶硅形成多晶硅栅极。

45、进一步的,在所述第一导电类型外延层中间位置通过离子注入形成jfet区,所述jfet区的上表面和所述栅氧化介质层的底面相接触。

46、本发明具有如下的有益效果:

47、(1)本发明可使得器件能够在保证击穿电压和传统超级结结构器件相比不变的情况下降低器件导通电阻,使得器件在反向耐压和正向导通间达到一个平衡的效果,进而在保障击穿电压的同时提高器件的正向导通性能;

48、(2)本发明可使得器件相较于传统超级结结构器件具有更加优异的性能,在正向导通时导通电阻更低,而反向时能更好的横向耗尽,增强了耐压能力,并降低了表面峰值电场,同时该结构还具有一个更好的耐电荷失衡能力,提高了碳化硅超级结结构器件的整体性能;

49、(3)本发明中第一导电类型重掺杂区、第二导电类型重掺杂区以及第二导电类型柱区的设置,为目前碳化硅难以形成超级结结构提供了一种获得超级结结构的全新方案,解决了目前在碳化硅中通常采用高能量离子注入工艺,或者采用多次外延结合多次离子注入工艺的问题,降低了制备工艺的难度,同时降低了制备高性能碳化硅超级结器件的成本;

50、(4)本发明可增强器件反偏时体内的峰值电场,提升器间雪崩耐量;

51、(5)通过本发明解决了现有技术中超级结结构中电荷不平衡引起超级结性能下降、超级结结构中柱区掺杂浓度不能过高以及碳化硅中实现完整超级结结构难度大,理论超级结性能无法在碳化硅中实现等问题。

- 还没有人留言评论。精彩留言会获得点赞!