竖直半导体器件及其制造方法与流程

本公开的各方面总体涉及竖直半导体器件。本公开的各方面还涉及这种竖直半导体器件的制造方法。

背景技术:

1、半导体器件通常包括集成在某种技术的半导体主体(诸如硅、碳化硅、砷化镓等)上的电子元件。在竖直半导体器件中,与横向半导体器件相反,电流从半导体主体的顶表面竖直流动至该半导体主体的底表面。通过此种方式,与横向半导体器件相比,可以实现相对较高的驱动能力。

2、图1所示的二极管100是已知的竖直半导体器件的示例。二极管100包括基板101和在所述基板上生长的外延层。外延层包括第一导电类型的第一半导体区102和作为扩散阱(diffusion well)构建至外延层中的第二导电类型的第二半导体区103。第一半导体区102和第二半导体区103一起形成pn结。例如,第一导电类型可以是n型,并且第二导电类型可以是p型。在这种情况下,第一半导体区102用作二极管100的阴极,并且第二半导体区103用作二极管100的阳极。在另一示例中,第一半导体区102和第二半导体区103的导电类型的极性反转,因此也分别反转了该第一半导体区102和第二半导体区103作为阳极和阴极的作用。接触部105a、105b布置为实现电接入二极管100的阳极和阴极。

3、二极管100还包括布置在外延层的横向边缘处的第二导电类型的沟道截断区104。实际上,当在晶片上制造多个半导体器件时,沟道截断区104布置在最终将形成相应半导体器件的晶片相应部分之间的锯切路径中。沟道截断区104通常布置为防止在晶片测试期间在晶片的相邻管芯上形成寄生沟道,并且在二极管100的场终端(field termination)中形成界限清楚的场。

4、竖直半导体器件通常包括绕半导体主体的周边的场终端,以防止或限制在反向偏置操作中发生过早的横向击穿。如图1所示,已知的场终端方法是增加第二半导体区103与沟道截断区104之间的第一距离d1,使得该第一距离d1大于第二半导体区103与基板101之间的第二距离d2。通过此种方式,在反向偏置条件下,第一半导体区102和第二半导体区103之间的结将先延伸至基板101,然后延伸至外延层的边缘,使得首先发生竖直击穿。

5、用于防止过早横向击穿的已知方法的缺点是,场终端可能占据半导体主体的相对较大区域,这对半导体器件的有源区域不具有有效贡献。这适用于图1的二极管100,而且适用于其它类型的竖直半导体器件,诸如双极结晶体管(bjt)。

6、此外,在图1所示的示例中,二极管100的制造方法需要应用掩模层、执行光刻和蚀刻步骤以及注入和驱动离子以形成第二半导体区103作为外延层中的扩散部。这可能导致半导体器件所需的热预算、处理扩展、能量消耗以及更普遍制造成本的增加。

7、us2015/0123240a1公开了一种半导体器件,该半导体器件具有包括第一导电类型的半导体材料的基板。包括第二导电类型的半导体材料的第一层形成在基板中,其中第一层和第一导电类型的半导体材料之间的边界作为p-n结。通过各向异性蚀刻来形成穿过第一层的竖直沟槽,并且该竖直沟槽至少延伸至边界。

8、cn103840013a公开了一种双向tvs和该双向tvs的制造方法。双向tvs包括第一导电类型基板、第二导电类型基区、第一导电类型导电层、多个槽部、氧化层、第一电极和第二电极。

9、ep0232510a2公开了一种具有平面结的半导体器件,其中该平面结具有自动钝化终端,该半导体器件包括:第一导电类型的硅基板;第二导电类型的外延层,该外延层形成在基板上从而形成pn结;第一导电类型的第一区,该第一区在其内部限定器件的有源部分。第一区从外延层的表面横向延伸至基板。

技术实现思路

1、本公开的各方面涉及一种半导体器件及其制造方法,其中,上述一个或多个缺点不会发生或几乎不会发生。

2、下文阐述了本文公开的某些实施例的方面的概述。应当理解的是,提出这些方面仅以向读者提供这些特定实施例的简要概述,并且这些方面不旨在限制本公开的范围。实际上,本公开可以涵盖可能未阐述的各种方面和/或方面的组合。

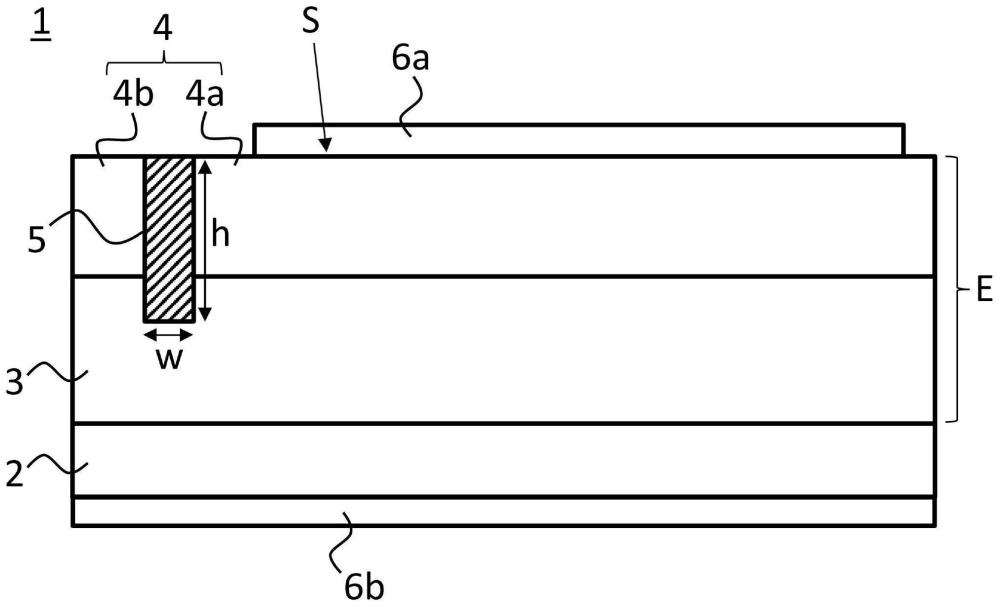

3、根据本公开的一方面,提供了一种竖直半导体器件。半导体器件包括半导体主体,该半导体主体包括基板和布置在所述基板上的外延层。外延层包括第一导电类型的第一半导体区和与第一导电类型不同的第二导电类型的第二半导体区。第二半导体区相对于第一半导体区与基板相对地布置。此外,在从外延层到基板的第一方向上观察时,第一半导体区和第二半导体区各自延伸跨过半导体主体的整个区域。

4、根据本公开的方面的半导体器件还包括布置在半导体主体中的沟槽。沟槽延伸穿过第二半导体区并且至少部分进入第一半导体区,从而将第二半导体区划分成相互电隔离的内部部分和外部部分。此外,半导体包括第一导电接触部,该第一导电接触部布置在第二半导体区上并且构造成使得能够电接入内部部分。

5、通过采用上述使第二半导体区的内部部分和外部部分电绝缘的沟槽,可以显著减小场终端所需的面积。此外,通过使用沟槽,第二半导体区不再需要构建至外延层中,并且可以布置为延伸跨过半导体主体的整个区域。换言之,第二半导体区域可以布置为完全覆盖第一半导体区。结果,如下文进一步解释的,可以通过更具成本效益和时间效益的方式来实现半导体器件的制造处理。

6、外延层可以为第一导电类型,并且第二半导体区可以形成为外延层中的毯式注入区。或者,外延层可以包括布置在基板顶部的第一导电类型的第一外延层,所述第一外延层形成第一半导体区,以及布置在第一外延层顶部的第二导电类型的第二外延层,所述第二外延层形成第二半导体区。

7、半导体器件还可以包括布置在沟槽内部的电绝缘材料。在示例中,电绝缘材料可以包括氧化硅、氮化硅和未掺杂多晶硅中的至少一种。沟槽可以完全填充有所述电绝缘材料。

8、沟槽可以完全延伸穿过第一半导体区和第二半导体区。

9、沟槽在第一方向上的深度可以大于沟槽在垂直于所述第一方向的第二方向上的宽度。例如,深度可以是宽度的至少两倍。在另一示例中,深度可以是宽度的至少十倍。

10、沟槽可以形成为围绕内部部分的闭合环路形状。

11、沟槽可以布置为更靠近半导体主体的周边而不是半导体主体的中心。通过此种方式,可以使半导体主体的有源区域最大化。

12、半导体器件还可以包括第二导电接触部,该第二导电接触部构造成使得能够电接入第一半导体区。例如,第二导电接触部可以布置在基板上并且与第一半导体区相对。在这种情况下,基板可以为第一导电类型,并且第二导电接触部可以通过所述基板与第一半导体区电连接。

13、第一半导体区和第二半导体区可以一起形成pn结,并且半导体器件可以是二极管。

14、在一些实施例中,第一导电接触部可以与第二半导体区形成肖特基(schottky)接触。为此,半导体器件可以包括肖特基二极管。

15、外延层还可以包括第一导电类型的第三半导体区。第三半导体区可以通过第二半导体区与第一半导体区间隔。在这种情况下,半导体器件可以是双极结型晶体管bjt。例如,第二半导体区可以形成bjt的基极,第一和第三半导体区中的一个可以形成bjt的集电极,并且第一和第三半导体区中的另一个可以形成bjt的发射极。

16、在另一实施例中,半导体可以包括第三导电接触部,该第三导电接触部构造成使得能够电接入第三半导体区。例如,第三导电接触部可以在半导体主体的与第一导电接触部相同的表面处布置在第三半导体区上。

17、根据本公开的另一方面,提供了一种根据上述的竖直半导体器件的制造方法。该方法包括以下步骤:a)设置半导体主体,该半导体主体包括基板和布置在该基板上的外延层,其中,外延层包括第一导电类型的第一半导体区,该第一半导体区在从外延层到基板的第一方向上延伸跨越半导体主体的整个区域;b)将与所述第一导电类型不同的第二导电类型的第二半导体区相对于第一半导体区与基板相对地布置在外延层中,其中,在第一方向上,第二半导体区延伸跨越半导体主体的整个区域;c)在半导体主体中形成沟槽,该沟槽延伸穿过第二半导体区并且至少部分进入第一半导体区,从而将第二半导体区分为相互电隔离的内部部分和外部部分;以及d)在第二半导体区上形成第一导电接触部,第一导电接触部布置为使得能够电接入内部部分。

18、通过采用沟槽,第二半导体区不需要结构化,并且可以形成为完全延伸跨过半导体主体的整个区域。例如,第二半导体区布置为完全覆盖第一半导体区。这不需要布置掩模层以及执行光刻和蚀刻步骤以用于布置第二半导体区,这可以减少制造方法期间的热预算、处理扩展和能量消耗。内部部分可以用作半导体器件的有源区,并且可以通过第一导电接触来电接入。

19、步骤a)可以包括设置基板并且在所述基板的顶部生长第一半导体区作为第一导电类型的第一外延层。

20、步骤b)可以包括在第一半导体区的顶部生长第二半导体区作为第二导电类型的第二外延层。

21、可替代地,步骤b)可以包括在外延层中毯式注入第二半导体区。例如,在毯式注入步骤后可以在熔炉中进行驱入步骤以驱入扩散。在驱入步骤的同时,可以产生氧化物以用于可选后续光刻和结构化步骤,诸如通过结构化的方式来形成另外的半导体区。通过此种方式,不需要在单独的熔炉步骤中单独生长这种氧化物,从而节省了热预算。

22、步骤c)可以包括执行各向异性蚀刻步骤以形成沟槽。通过此种方式,可以布置深且窄的沟槽,以在提供将内部部分与外部部分电隔离的功能的同时,使半导体主体的可用有源区域的影响最小化。

23、该方法还可以包括在沟槽内部布置电绝缘材料。例如,电绝缘材料可以包括氧化硅、氮化硅和未掺杂多晶硅中的至少一种。沟槽可以完全填充有所述电绝缘材料。

24、沟槽可以形成为完全延伸穿过第一半导体区和第二半导体区。

25、沟槽可以形成为所述沟槽在第一方向上的深度大于所述沟槽在垂直于所述第一方向的第二方向上的宽度,例如至少为两倍,或者在另一示例中至少为十倍。

26、沟槽可以形成为围绕内部部分的闭合环路形状。

27、沟槽可以布置成更靠近半导体主体的周边而不是半导体主体的中心。

28、该方法还包括布置第二导电接触部,该第二导电接触部构造成使得能够电接入第一半导体区。例如,第二导电接触部可以布置在基板上并且与第一半导体区相对。在这种情况下,基板可以为第一导电类型,并且第二导电接触部可以通过所述基板与第一半导体区电连接。

29、第一半导体区和第二半导体区可以一起形成pn结,并且半导体器件可以是二极管。

30、在一些实施例中,第一导电接触部可以与第二半导体区形成肖特基接触。为此,半导体器件可以包括肖特基二极管。

31、该方法还可以包括步骤d)在外延层中形成第一导电类型的第三半导体区,其中,第三半导体区可以通过第二半导体区与第一半导体区间隔。在这种情况下,半导体器件可以是双极结型晶体管bjt。例如,第二半导体区可以形成bjt的基极,第一和第三半导体区中的一个可以形成bjt的集电极,并且第一和第三半导体区中的另一个可以形成bjt的发射极。

32、步骤d)可以包括在半导体器件上布置掩模层并且执行离子注入步骤以形成第三半导体区。掩模层可以包括氧化物材料,优选氧化硅。此外,如果使用毯式注入步骤来形成第二半导体区,则可以在所述毯式注入步骤后的驱入步骤期间形成掩模层。

33、该方法还可以包括布置第三导电接触部,该第三导电接触部构造成使得能够电接入第三半导体区。例如,第三导电接触部可以在半导体主体的与第一导电接触部相同的表面处布置在第三半导体区上。

- 还没有人留言评论。精彩留言会获得点赞!