包括堆叠结构之间的连接部的半导体器件及其制造方法与流程

本公开的多种实施例总体上涉及一种半导体器件,更具体地,涉及包括堆叠结构之间的连接部的半导体器件及其制造方法。

背景技术:

1、近来,作为制造半导体器件的方法,已提出在第一基板和第二基板上形成不同的集成电路,并且接合其上形成有集成电路的第一基板和第二基板以将集成电路彼此连接的方法。作为示例,第一基板和第二基板的集成电路可以通过将第一基板和第二基板的导电焊盘彼此接合而彼此电连接。在这种情况下,第一基板和第二基板的导电焊盘的结构稳定性可以确定半导体器件的电可靠性。

技术实现思路

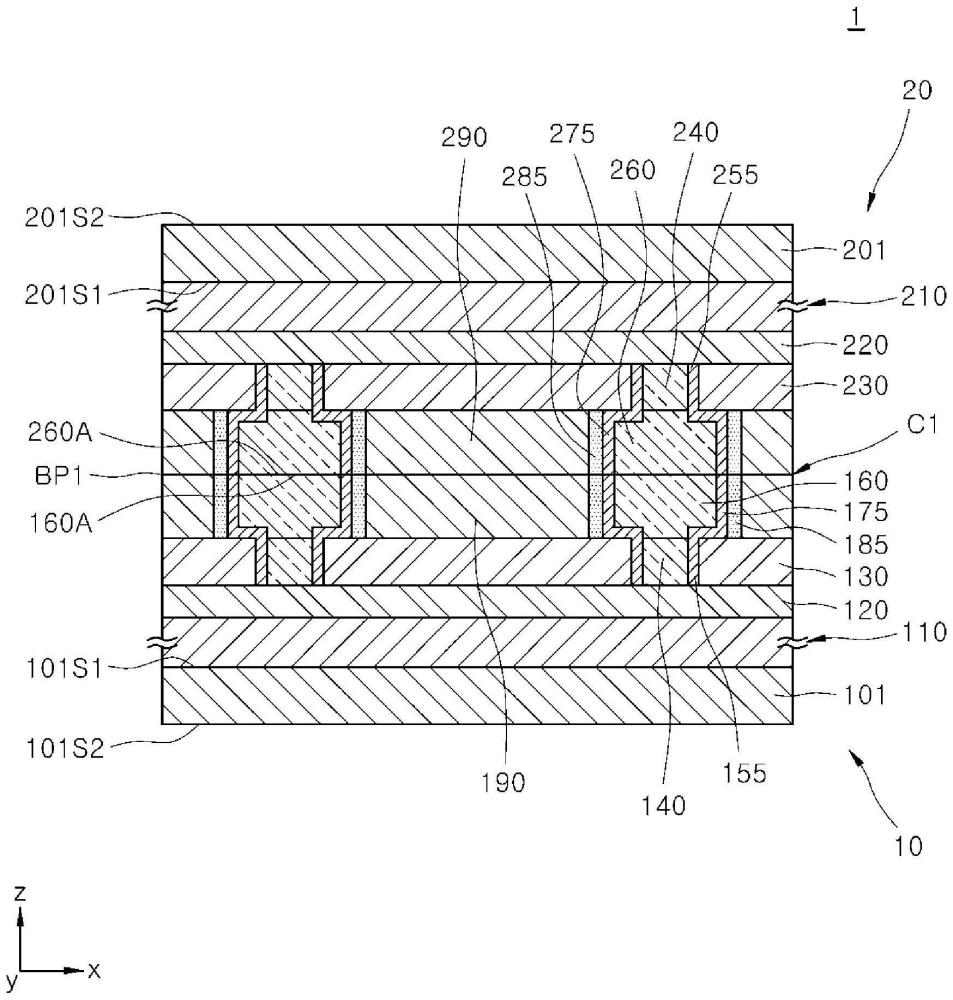

1、根据本公开的一个实施例的一种半导体器件可以包括第一堆叠结构,该第一堆叠结构包括第一基体、设置在第一基体的表面上方的第一连接焊盘以及与第一连接焊盘相邻设置的第一焊盘缓冲层。第一焊盘缓冲层可以包括具有多孔结构的第一绝缘材料。此外,该半导体器件可以包括第二堆叠结构,该第二堆叠结构包括第二基体、设置在第二基体的表面上方的第二连接焊盘以及与第二连接焊盘相邻设置的第二焊盘缓冲层。第二焊盘缓冲层可以包括具有多孔结构的第二绝缘材料。该半导体器件可以包括连接第一连接焊盘和第二连接焊盘的第一堆叠结构和第二堆叠结构的连接部。

2、根据本公开的另一实施例的一种半导体器件可以包括第一基板结构,该第一基板结构包括基板、设置在基板上方的存储单元驱动器电路、设置在基板上方以电连接到存储单元驱动器电路的第一连接焊盘以及在第一连接焊盘的横向方向上设置的第一焊盘缓冲层。第一焊盘缓冲层可以包括具有多孔结构的第一绝缘材料。此外,该半导体器件可以包括第二基板结构,该第二基板结构包括基板、设置在基板上方的存储单元结构、设置在基板上方以电连接到存储单元结构的第二连接焊盘以及在第二连接焊盘的横向方向上设置的第二焊盘缓冲层。第二焊盘缓冲层可以包括具有多孔结构的第二绝缘材料。此外,该半导体器件可以包括第一基板结构和第二基板结构的连接部,该连接部连接第一连接焊盘和第二连接焊盘。

3、公开了一种制造半导体器件的方法。在该方法中,可以形成第一基板结构,该第一基板结构包括基板、设置在第一基板的表面上方的第一连接焊盘以及与第一连接焊盘相邻设置的第一焊盘缓冲层。第一焊盘缓冲层可以包括金属有机框架。可以形成第二基板结构,该第二基板结构包括基板、设置在第二基板的表面上方的第二连接焊盘以及与第二连接焊盘相邻设置的第二焊盘缓冲层。第二焊盘缓冲层可以包括金属有机框架。可以将第一基板结构和第二基板结构彼此接合以形成第一连接焊盘和第二连接焊盘的连接部。

4、根据本公开的另一实施例的一种半导体器件可以包括第一基板结构,该第一基板结构包括第一连接焊盘和设置成至少围绕第一连接焊盘的侧壁的第一焊盘缓冲层。此外,该半导体器件可以包括第二基板结构,该第二基板结构包括第二连接焊盘和设置成至少围绕第二连接焊盘的侧壁的第二焊盘缓冲层。第一基板结构和第二基板结构使用第一连接焊盘和第二连接焊盘彼此物理接合和电接合。第一焊盘缓冲层和第二焊盘缓冲层包括具有多孔结构的绝缘材料。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中,具有所述多孔结构的所述第一绝缘材料和所述第二绝缘材料包括金属有机框架。

3.根据权利要求2所述的半导体器件,其中,所述金属有机框架具有包括空腔的二维结构,以及

4.根据权利要求1所述的半导体器件,还包括:

5.根据权利要求4所述的半导体器件,其中,所述第一焊盘阻挡层和所述第二焊盘阻挡层中的每一个的二维材料包括mxene。

6.根据权利要求5所述的半导体器件,

7.根据权利要求5所述的半导体器件,其中,所述第一焊盘阻挡层和所述第二焊盘阻挡层中的每一个包括至少一层mxene。

8.根据权利要求1所述的半导体器件,其中,在所述连接部中,所述第一连接焊盘的表面积与所述第二连接焊盘的表面积基本相同。

9.根据权利要求1所述的半导体器件,其中,在所述连接部中,所述第一连接焊盘的表面积与所述第二连接焊盘的表面积不同。

10.根据权利要求1所述的半导体器件,

11.根据权利要求1所述的半导体器件,其中,所述连接部还包括所述第一焊盘缓冲层和所述第二焊盘缓冲层的接合。

12.根据权利要求1所述的半导体器件,

13.根据权利要求1所述的半导体器件,其中,所述第一堆叠结构还包括:

14.根据权利要求1所述的半导体器件,其中,所述第二堆叠结构还包括:

15.根据权利要求1所述的半导体器件,其中,所述第二堆叠结构还包括:

16.一种半导体器件,包括:

17.根据权利要求16所述的半导体器件,其中,具有所述多孔结构的所述第一绝缘材料和所述第二绝缘材料包括金属有机框架。

18.根据权利要求17所述的半导体器件,

19.根据权利要求16所述的半导体器件,还包括第一焊盘阻挡层和第二焊盘阻挡层中的至少一个,所述第一焊盘阻挡层设置在所述第一连接焊盘和所述第一焊盘缓冲层之间,以及所述第二焊盘阻挡层设置在所述第二连接焊盘和所述第二焊盘缓冲层之间,所述第一焊盘阻挡层包括二维材料层,以及所述第二焊盘阻挡层包括二维材料。

20.根据权利要求19所述的半导体器件,其中,所述第一焊盘阻挡层和所述第二焊盘阻挡层中的每一个的所述二维材料包括mxene。

21.根据权利要求20所述的半导体器件,其中,所述第一焊盘阻挡层和所述第二焊盘阻挡层中的每一个包括至少一层mxene。

22.根据权利要求16所述的半导体器件,

23.根据权利要求16所述的半导体器件,其中,所述第一基板结构还包括:

24.根据权利要求16所述的半导体器件,其中,所述第二基板结构还包括:

25.一种制造半导体器件的方法,所述方法包括:

26.根据权利要求25所述的方法,其中,形成所述第一基板结构包括:

27.根据权利要求26所述的方法,还包括在所述第一基板上方形成存储单元驱动器电路或存储单元结构。

28.根据权利要求25所述的方法,其中,形成所述第二基板结构包括:

29.根据权利要求25所述的方法,其中,形成所述第二基板结构包括:

30.根据权利要求25所述的方法,

31.一种半导体器件,包括:

32.根据权利要求31所述的半导体器件,其中,具有多孔结构的所述绝缘材料包括金属有机框架。

33.根据权利要求32所述的半导体器件,

34.根据权利要求33所述的半导体器件,其中,所述二维材料包括mxene。

技术总结

本公开涉及半导体器件以及制造方法。根据实施例的半导体器件包括第一堆叠结构,第一堆叠结构包括第一基体、设置在第一基体的表面上方的第一连接焊盘以及与第一连接焊盘相邻设置的第一焊盘缓冲层,第一焊盘缓冲层包括具有多孔结构的绝缘材料。此外,该半导体器件包括第二堆叠结构,第二堆叠结构包括第二基体、设置在第二基体的表面上方的第二连接焊盘以及与第二连接焊盘相邻设置的第二焊盘缓冲层,第二焊盘缓冲层包括具有多孔结构的绝缘材料。该半导体器件包括连接第一连接焊盘和第二连接焊盘的第一堆叠结构和第二堆叠结构的连接部。

技术研发人员:林米乐,具元泰

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!