一种外延结构及其制备方法、半导体器件与流程

本申请涉及半导体,特别涉及一种外延结构及其制备方法、半导体器件。

背景技术:

1、一些si基衬底的gan hemt器件中,由于si基衬底与gan之间存在较大的晶格失配和热失配,在大尺寸的si基衬底上得到高晶体质量的gan基外延材料比较困难,尤其是高温生长结束后降温的过程会引入较大的张应力,使得外延片的翘曲较大导致外延层出现较多的龟裂。为减少外延层的龟裂,相关技术中,采用由aln/algan组成的超晶格结构释放应力以获得较高晶体质量的外延层。然而aln的迁移性能较差,难以生长形成良好的二维aln晶体薄膜,且aln晶格常数与gan的晶格常数接近,不能有效为后续的gan引入压应力,这使得外延层的裂纹会加剧,外延厚度受到限制不宜长厚,从而使器件耐压能力受限,也不宜获得良好的晶体质量。这些问题最终会导致漏电,影响器件性能。

技术实现思路

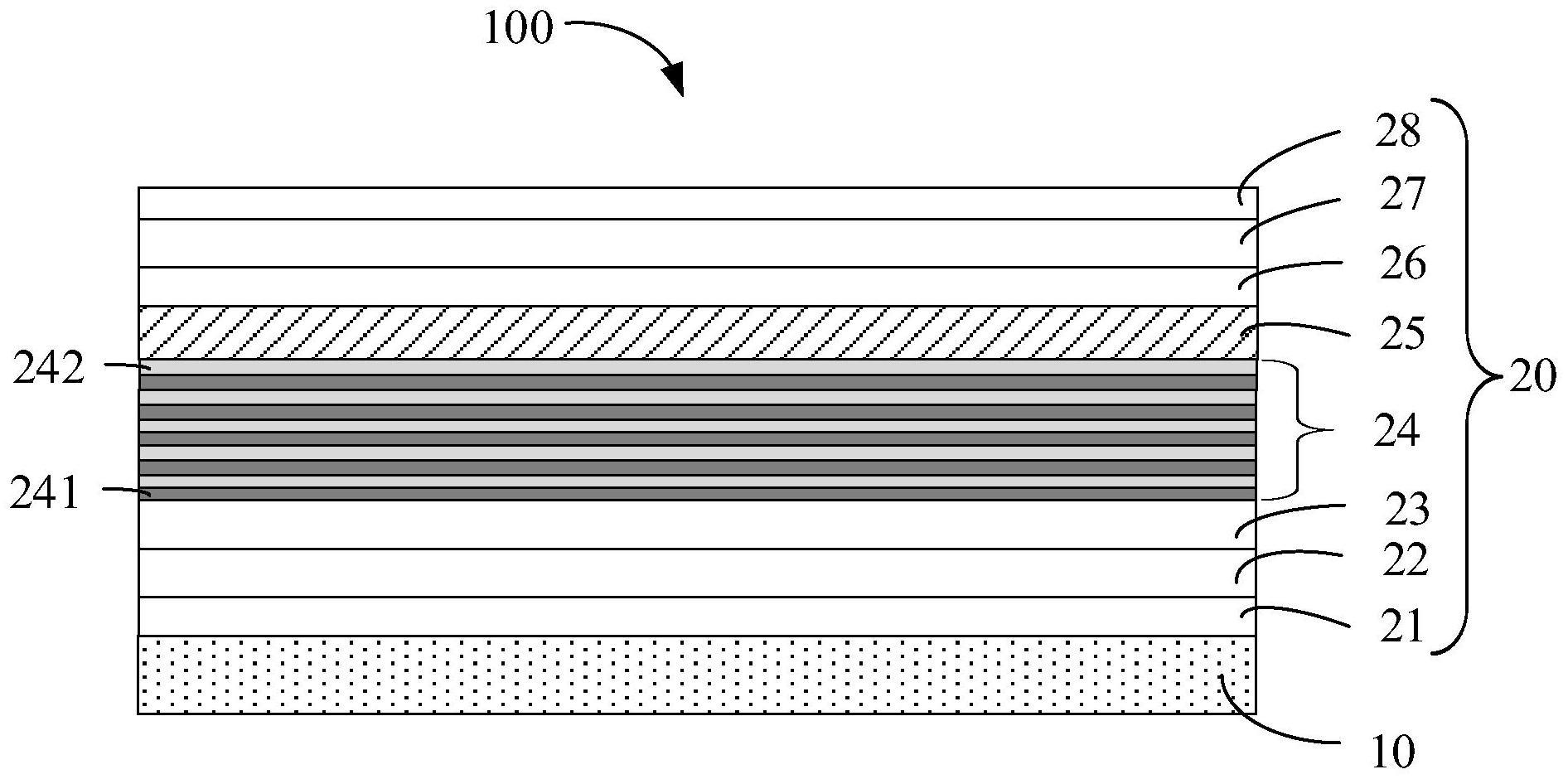

1、根据本申请实施例的第一方面,提供了一种外延结构,其包括:

2、硅衬底;

3、外延层,所述外延层包括设于所述硅衬底一侧的超晶格缓冲层,所述超晶格缓冲层包括交替间隔的多层bn膜层和多层algan膜层。

4、在一些实施例中,所述bn膜层厚度小于所述algan膜层厚度;每一所述bn膜层的厚度范围为5nm-10nm;每一所述algan膜层的厚度范围为20nm-40nm。

5、在一些实施例中,所述多层bn膜层的各层bn膜层厚度相等;

6、所述多层algan膜层的各algan膜层厚度相等。

7、在一些实施例中,所述超晶格缓冲层中位于靠近所述硅衬底一侧的底层为bn膜层,所述超晶格缓冲层中位于背离所述硅衬底一侧的顶层为algan膜层。

8、在一些实施例中,所述外延结构还包括位于所述超晶格缓冲层背离所述硅衬底一侧表面的耐压层,所述耐压层为gan膜层;

9、所述位于背离所述硅衬底一侧的顶层的algan膜层中,至少背离所述硅衬底的表面材料为gan。

10、在一些实施例中,所述外延结构还包括设于所述硅衬底和所述超晶格缓冲层之间的成核层及过渡层,以及依序设于所述耐压层背离所述超晶格缓冲层的插入层、势垒层以及p型增强层;其中,所述成核层设于所述硅衬底之上,所述过渡层设于所述成核层背离所述硅衬底的一侧。

11、在一些实施例中,所述外延层采用金属有机物化学气相淀积技术或分子束外延技术形成。

12、根据本申请实施例的第二方面,提供了一种外延结构的制备方法,其包括:

13、提供硅衬底;

14、在所述硅衬底之上形成外延层;所述形成外延层包括形成超晶格缓冲层,所述超晶格缓冲层位于所述硅衬底的一侧;所述超晶格缓冲层包括交替间隔的多层bn膜层和多层algan膜层。

15、在一些实施例中,所述形成超晶格缓冲层包括依序形成交替间隔的多层bn膜层和多层algan膜层;其中,采用bcl3或b2h4与nh3的混合气体在高温下形成所述bn膜层。

16、在一些实施例中,所述bn膜层厚度小于所述algan膜层厚度;每一所述bn膜层的厚度范围为5nm-10nm;每一所述algan膜层的厚度范围为20nm-40nm。

17、在一些实施例中,所述多层bn膜层的各层bn膜层厚度相等;

18、所述多层algan膜层的各algan膜层厚度相等。

19、在一些实施例中,所述超晶格缓冲层中位于靠近所述硅衬底一侧的底层为bn膜层,所述超晶格缓冲层中位于背离所述硅衬底一侧的顶层为algan膜层。

20、在一些实施例中,在形成设于所述硅衬底一侧的超晶格缓冲层之后,所述外延结构的制备方法还包括:

21、在位于所述超晶格缓冲层背离所述硅衬底一侧表面形成耐压层;所述耐压层为gan膜层。

22、在一些实施例中,形成所述位于背离所述硅衬底一侧的顶层的algan膜层时,减少al的摩尔量,使得位于背离所述硅衬底一侧的顶层的algan膜层中,至少背离所述硅衬底的表面材料为gan。

23、在一些实施例中,在形成所述超晶格缓冲层之前,所述形成外延结构还包括:

24、在所述硅衬底上依序形成成核层及过渡层;其中,所述成核层设于所述硅衬底之上,所述过渡层设于所述成核层背离所述硅衬底的一侧;

25、在形成所述超晶格缓冲层之后,所述形成外延结构还包括:

26、依序形成设于所述耐压层背离所述超晶格缓冲层的插入层、势垒层以及p型增强层。

27、在一些实施例中,所述外延层采用金属有机物化学气相淀积技术或分子束外延技术形成。

28、根据本申请实施例的第三方面,提供了一种半导体器件,所述半导体器件包括如上所述的外延结构。

29、本申请实施例所达到的主要技术效果是:

30、本申请实施例提供的外延结构,通过将超晶格缓冲层设置为交替间隔的多层bn膜层和多层algan膜层,相较于相关技术中采用交替间隔的aln膜层和algan膜层形成的超晶格缓冲层而言,基于bn的迁移能力较好,容易形成平整的二维晶体材料,bn的b原子比al原子和ga原子小,bn的晶格常数比aln的晶格常数小等优点,本申请的bn膜层可为后续生长的其它外延膜层(比如耐压层gan)提供较大压应力来尽可能较大程度抵消硅衬底对外延层带来的张应力,从而使整个外延层趋于平整或者略微凸起的状态,这样更有利于外延层生长的工艺控制,不容易出现外延层龟裂,同时由于bn比aln更高的击穿场强,可以进一步提高该外延结构的器件的耐压。因此,相较于相关技术中采用交替间隔的aln膜层和algan膜层形成的超晶格缓冲层而言,该交替间隔的多层bn膜层和多层algan膜层所形成的超晶格缓冲层,能够提供更好地进行应力调控及增加耐压能力,有利于提高外延层的质量进而提升具有该外延结构的器件的可靠性。

技术特征:

1.一种外延结构,其特征在于,包括:

2.如权利要求1所述的外延结构,其特征在于,所述bn膜层厚度小于所述algan膜层厚度;每一所述bn膜层的厚度范围为5nm-10nm;每一所述algan膜层的厚度范围为20nm-40nm。

3.如权利要求1所述的外延结构,其特征在于,所述多层bn膜层的各层bn膜层厚度相等;

4.如权利要求1所述的外延结构,其特征在于,所述超晶格缓冲层中位于靠近所述硅衬底一侧的底层为bn膜层,所述超晶格缓冲层中位于背离所述硅衬底一侧的顶层为algan膜层。

5.如权利要求4所述的外延结构,其特征在于,所述外延结构还包括位于所述超晶格缓冲层背离所述硅衬底一侧表面的耐压层,所述耐压层为gan膜层;

6.如权利要求5所述的外延结构,其特征在于,所述外延结构还包括设于所述硅衬底和所述超晶格缓冲层之间的成核层及过渡层,以及依序设于所述耐压层背离所述超晶格缓冲层的插入层、势垒层以及p型增强层;其中,所述成核层设于所述硅衬底之上,所述过渡层设于所述成核层背离所述硅衬底的一侧。

7.如权利要求1至6中任一项所述的外延结构,其特征在于,所述外延层采用金属有机物化学气相淀积技术或分子束外延技术形成。

8.一种外延结构的制备方法,其特征在于,包括:

9.如权利要求8所述的外延结构的制备方法,其特征在于,所述形成超晶格缓冲层包括依序形成交替间隔的多层bn膜层和多层algan膜层;其中,采用bcl3或b2h4与nh3的混合气体在高温下形成所述bn膜层。

10.如权利要求8所述的外延结构的制备方法,其特征在于,所述bn膜层厚度小于所述algan膜层厚度;每一所述bn膜层的厚度范围为5nm-10nm;每一所述algan膜层的厚度范围为20nm-40nm。

11.如权利要求8所述的外延结构的制备方法,其特征在于,所述多层bn膜层的各层bn膜层厚度相等;

12.如权利要求8所述的外延结构的制备方法,其特征在于,所述超晶格缓冲层中位于靠近所述硅衬底一侧的底层为bn膜层,所述超晶格缓冲层中位于背离所述硅衬底一侧的顶层为algan膜层。

13.如权利要求11所述的外延结构的制备方法,其特征在于,在形成设于所述硅衬底一侧的超晶格缓冲层之后,所述外延结构的制备方法还包括:

14.如权利要求13所述的外延结构的制备方法,其特征在于,形成所述位于背离所述硅衬底一侧的顶层的algan膜层时,减少al的摩尔量,使得位于背离所述硅衬底一侧的顶层的algan膜层中,至少背离所述硅衬底的表面材料为gan。

15.如权利要求14所述的外延结构的制备方法,其特征在于,在形成所述超晶格缓冲层之前,所述形成外延结构还包括:

16.如权利要求8至15中任一项所述的外延结构的制备方法,其特征在于,所述外延层采用金属有机物化学气相淀积技术或分子束外延技术形成。

17.一种半导体器件,其特征在于,所述半导体器件包括如权利要求1至7中任一项所述的外延结构。

技术总结

本申请提供一种外延结构及其制备方法、半导体器件。外延结构包括硅衬底及外延层。外延层包括设于硅衬底一侧的超晶格缓冲层,超晶格缓冲层包括交替间隔的多层BN膜层和多层ALGaN膜层。上述外延结构,通过将超晶格缓冲层设置为交替间隔的多层BN膜层和多层ALGaN膜层,相较于采用交替间隔的AlN膜层和ALGaN膜层形成的超晶格缓冲层而言,BN膜层可为后续生长的其它外延膜层提供较大压应力来尽可能较大程度抵消硅衬底对外延层带来的张应力,从而使整个外延层趋于平整或者略微凸起的状态,这样更有利于外延层生长的工艺控制,不容易出现外延层龟裂,同时由于BN比AlN更高的击穿场强,可以进一步提高该外延结构的器件的耐压。

技术研发人员:卢云霞,胡自强,黎力,张雪

受保护的技术使用者:英诺赛科(苏州)半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!