一种增加JFET区源极接触的锥型槽VDMOSFET结构的制作方法

本发明涉及大功率器件mosfet结构,具体涉及一种锥形槽六边形元胞的碳化硅vdmosfet结构。

背景技术:

1、mosfet器件在大功率分立器件领域应用广泛,当前功率器件行业内多数应用的mosfet结构为vdmosfet和umosfet两种。由于刻蚀难度大,难以保证u槽两侧平行,容易形成subtrench等原因,很多功率器件厂商不得不放弃对umosfet产品的开发,将研发精力投入到vdmosfet研发优化上。(如图1和2)

2、vdmosfet的研发主要分两个方向:1.器件性能的优化(迁移率、可靠性、损耗及电学特性等);2.器件尺寸的缩减。

3、1、关于器件性能的优化:

4、器件性能的优化主要体现在迁移率的提高优化,体二极管正向压降的降低优化,开关损耗的降低优化,开关时间的降低优化,可靠性的优化等。

5、关于器件性能,传统的vdmosfet器件,其体二极管主要由pn结组成,其开启电压相对较大。

6、传统vdmosfet的crss也较大,这是由于栅极(g极)与漏极(d极)的正对面积较大。crss较大,直接导致器件的ciss、coss等参数较大,从而增加器件的开关损耗。

7、2、关于器件尺寸的缩减:

8、器件尺寸的缩减主要体现在单个元胞尺寸的缩减,主要与工艺材料的特性、质量等因素有关,也与光刻机的能力及器件结构设计有关。(器件单个元胞尺寸标注如图3所示)

9、单个元胞尺寸的缩减,主要与各膜层材料特性有关。器件设计端主要考虑的问题在于如何减少l9。减少l9的主要途径在于l1与l5尺寸的减小。目前国际市场上的碳化硅vdmosfet器件l1尺寸基本都维持在2um左右,这主要因为当前器件采用了jfet区(l1)注入技术,增加了jfet区载流子浓度,从而缩减了l1,但由于过高的jfet区浓度会使器件击穿电压降低,所以l1的尺寸基本趋于稳定。同理,由于器件p-well区受l2、l3、l4的限制,而l2、l3、l4又受l6、l7、l8的限制,l6、l7、l8受材料特性及光刻尺寸的限制,导致器件的元胞尺寸很难进一步减小。u槽mosfet结构的发明,大大缩减了单个元胞尺寸,但其对刻蚀要求过于严苛,且经常出现各种缺陷,让各大厂家望而却步。

10、在材料特性被设计者应用到极限程度后,如何进一步缩小器件尺寸,成为行业内开发者需要面临的新的难题。

11、很多行业内部开发者在元胞尺寸达到材料极限后,采用改变元胞形状的方法来增加器件电流密度,从而达到类似缩减元胞尺寸的相同效果。(如图4-6所示)

12、从以上几种元胞形状可知,不论采用哪种元胞形状,都将面临元胞尺寸无法继续缩减的问题以及开启电压较大和开关损耗较大的问题,并且由于多边形的元胞的排布方式变换栅极的互联方式也是比较困难的问题。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种增加jfet区源极接触的锥型槽vdmosfet结构,以解决传统的vdmosfet器件其pn结体二极管的开启电压相对较大导致正向压降较大,还有多晶硅栅对衬底漏极的正对面积较大导致开关损耗和开关时间较长,以及传统条形元胞在材料应用极限后、排布应用极限后及刻蚀工艺应用极限后尺寸无法继续缩小使电流密度无法继续缩小等一系列问题。

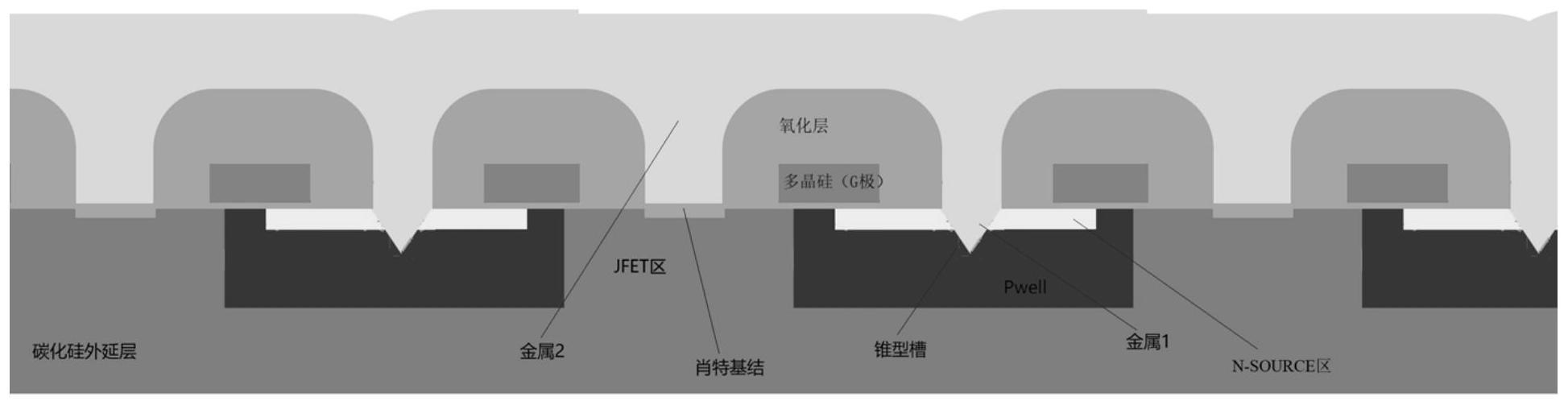

2、为解决以上技术问题,本发明提供一种增加jfet区源极接触的锥型槽vdmosfet结构,包括碳化硅外延层,所述碳化硅外延层上在二维平面内阵列排布有注入区,所述注入区包括pwell区、n-source区和jfet区,所述碳化硅外延层通过离子注入形成所述pwell区,所述pwell区上通过离子注入形成有n-source区,所述碳化硅外延层上淀积有多晶硅(g极),所述多晶硅(g极)外围包裹有氧化层,以上结构在定义单位范围内形成互相并联的六边形元胞1,所述jfet区上方顶端具有肖特基结,所述肖特基结上方多晶硅(g极)断裂,使g极与d极正对面积减小,所述肖特基结上方淀积有金属2,用于形成肖特基接触,所述碳化硅外延层表面还刻蚀形成有一锥型槽,所述锥型槽开口向上并贯穿所述n-source区下方并深入至所述pwell区内,所述锥型槽内淀积有金属1,用于形成欧姆接触。

3、在一些实施例中优选地方案,所述六边形元胞1在空间上包括pwell区、pwell区两侧相邻的jfet区的一半,在空间上所述pwell区及任意一侧相邻的jfet区可视作形成六边形元胞2,所述六边形元胞1与六边形元胞2尺寸相同。

4、在一些实施例中优选地方案,所述肖特基结位于所述jfet区顶端中部或至多靠近任意一侧所述pwell区但不接触。

5、在一些实施例中优选地方案,所述多晶硅(g极)至少部分位于所述jfet区上侧。

6、在一些实施例中优选地方案,所述氧化层包括位于所述多晶硅(g极)底部的栅氧氧化层及淀积在所述多晶硅(g极)侧面和顶部的氧化层,以形成栅源隔离的氧化层。

7、在一些实施例中优选地方案,所述金属1和金属2均为s极金属,所述金属1为ni用于欧姆接触,所述金属2为ti用于肖特基接触,所述ti上淀积有al。

8、在一些实施例中优选地方案,所述锥型槽为圆锥或四棱锥或五棱锥或六棱锥。

9、在一些实施例中优选地方案,所述锥型槽位于所述六边形元胞1的中心,其中,所述锥型槽位于所述n-source区中心部位。

10、在一些实施例中优选地方案,所述jfet区上方相邻的氧化层之间具有栅极互联金属槽,所述栅极互联金属槽内淀积有栅极金属,所述栅极金属由氧化层包裹与源极隔离,所述栅极金属与所述多晶硅(g极)接触形成栅极互联。

11、在一些实施例中优选地方案,该结构还包括位于所述碳化硅外延层底部的衬底层,所述衬底层底部具有漏极金属层。

12、与现有技术相比,本发明具有如下优点:

13、1、本发明的碳化硅vdmosfet结构在六边形元胞内部挖槽,将六边形元胞的优势与锥型槽的优势结合起来,进一步缩小了元胞尺寸。

14、2、在相同器件尺寸下,本发明的碳化硅vdmosfet结构将拥有更大的电流密度。

15、3、本发明的增加jfet区源极接触的锥型槽vdmosfet结构在jfet区顶端采用肖特基接触,可以大幅度降低碳化硅mosfet器件的体二极管的开启电压,从而降低体二极管正向压降。即将体二极管从原有的pn结二极管变成了具备抗浪涌特性的肖特基二极管,降低了体二极管开启电压、降低了体二极管正向压降。

16、4、本发明的增加jfet区源极接触的锥型槽vdmosfet结构将多晶硅栅分裂开,降低g极与d极的正对面积,大幅降低了器件的crss、ciss、coss、qg、qgd、开通损耗eon、关断损耗eoff等参数,进一步大幅度降低器件的开关损耗。

17、5、本发明采用栅极打孔互联方式,不对互联方向和组合做限制,解决六边形元胞的错位排布特点和体二极管从原有的pn结二极管变成了具备抗浪涌特性的肖特基二极管后多晶硅栅极彼此分立互联困难的问题。

- 还没有人留言评论。精彩留言会获得点赞!