半导体结构及其制作方法与流程

本发明涉及半导体,尤其涉及一种半导体结构及其制作方法。

背景技术:

1、传统封装工艺把各种有源器件和无源器件安装在基板上,占用面积大,可靠性差,不能满足封装系统越来越小型化的趋势,而基于标准硅工艺的三维异构封装技术,例如系统级封装(system in a package,简称sip)运用硅通孔(through-silicon via,简称tsv)技术和空腔结构将不同衬底上不同功能的半导体器件集成在一起,能在较小的区域内实现芯片的堆叠和互联,大大减小了半导体器件占用的面积并增加了其可靠性,因此,如何优化三维异构封装技术的工艺成为该产业未来发展的方向。

2、基于空腔结构的三维异构技术,往往需要在空腔内形成多个导电柱。这样,能够使得埋置在空腔内的半导体器件与导电柱电连接,进而能够将不同半导体器件通过导电柱实现电连接;或者,半导体器件通过导电柱进行散热或接地。其中,半导体器件与导电柱必须接触。然而,形成空腔及导电柱的工艺条件的精度不易控制,导致导电柱与半导体器件接触的表面不平整,降低电性效果;且制作导电柱的工艺步骤较多、难度较大,导致工艺成本较大。

技术实现思路

1、有鉴于此,本发明实施例提供的半导体结构及其制作方法能够提高导电柱与半导体器件的电性接触效果,且降低半导体结构的工艺难度和成本。

2、为达到上述目的,本发明的技术方案是这样实现的:

3、一方面,本发明实施例提供了一种半导体结构的制作方法,所述制作方法包括:提供第一衬底。在所述第一衬底表面形成至少一个凹槽。在所述至少一个凹槽内填充导电材料,形成多个导电柱。沿所述导电柱延伸方向,在所述导电柱的相对两端中的至少一端所在结构中形成第一空腔,所述第一空腔暴露所述导电柱的端面。在所述第一空腔中形成第一半导体器件,所述第一半导体器件与所述导电柱电连接。

4、在一些示例中,所述在所述导电柱的相对两端中的至少一端所在结构中形成第一空腔,包括:在所述第一衬底的所述凹槽开口所在表面形成第一半导体层,并在所述第一半导体层上形成所述第一空腔。

5、在一些示例中,所述在所述导电柱的相对两端中的至少一端所在结构中形成第一空腔,包括:

6、所述第一衬底的远离所述凹槽开口所在表面的一侧表面与所述凹槽底部所在平面之间的间距大于或等于所述半导体器件的厚度,在所述第一衬底远离所述凹槽开口所在表面的一侧表面形成所述第一空腔。或者,所述第一衬底的远离所述凹槽开口所在表面的一侧表面与所述凹槽底部所在平面之间的间距小于所述半导体器件的厚度,在所述第一衬底的远离所述凹槽开口所在表面的一侧表面形成第二半导体层,形成贯穿所述所述第二半导体层且延伸至所述导电柱的端面的所述第一空腔。

7、在一些示例中,所述第一衬底包括第一表面和第二表面,所述第一表面形成所述凹槽。在所述第二表面形成所述第一空腔之前,在所述第一表面键合支撑层。在所述第二表面形成所述第一空腔之后,去除所述支撑层。

8、在一些示例中,所述第一衬底包括第一表面和第二表面,所述第一表面形成所述凹槽。在所述凹槽内形成所述导电柱后,在所述第一表面形成所述第一半导体层。减薄所述第一衬底远离所述第一表面的一侧,至暴露所述导电柱靠近所述第一衬底的第二表面的端面。在所述第一半导体层远离所述第一衬底的一侧表面形成所述第一空腔。

9、在一些示例中,所述制作方法还包括:在所述第一衬底被减薄的表面形成第三半导体层,并在所述第三半导体层上形成第二空腔;所述第二空腔的底部暴露所述导电柱靠近所述第一衬底的第一表面的端面。在所述第二空腔中形成第二半导体器件,所述第二半导体器件与所述导电柱电连接。

10、在一些示例中,所述多个导电柱包括多组,一组所述导电柱的高度相同;不同组所述导电柱的高度相同或不同。所述第一空腔包括多个,一个所述第一空腔的底部所在平面与所述一组导电柱靠近所述第一空腔的端面大致齐平。

11、本发明实施例提供的半导体结构的制作方法,在第一衬底的一侧表面形成至少一个凹槽,以及在至少一个凹槽内形成至少一个导电柱后,此时导电柱的一个端面与第一衬底的一侧表面大致齐平。通过判断凹槽底部所在平面(即导电柱沿其延伸方向的另一端面)与第一衬底的远离凹槽开口所在表面的一侧表面之间的间距,和第一半导体器件的厚度的大小关系,来判断在导电柱的另一端所在结构通过后续工艺设置第一空腔或是在凹槽开口所在的第一衬底的表面通过后续工艺设置第一空腔。这样,形成的导电柱可以直接与后续在第一空腔内形成的第一半导体器件电连接,不需要先做较深的凹槽和较高的导电柱,然后在后续工艺中去除多余高度的导电柱,从而,降低导电柱和第一空腔的工艺步骤和成本,并且,避免因去除多余长度的导电柱过程中的工艺条件导致导电柱端面不平整的问题,进而降低导电柱与第一半导体器件的不良的电性连接效果的几率。

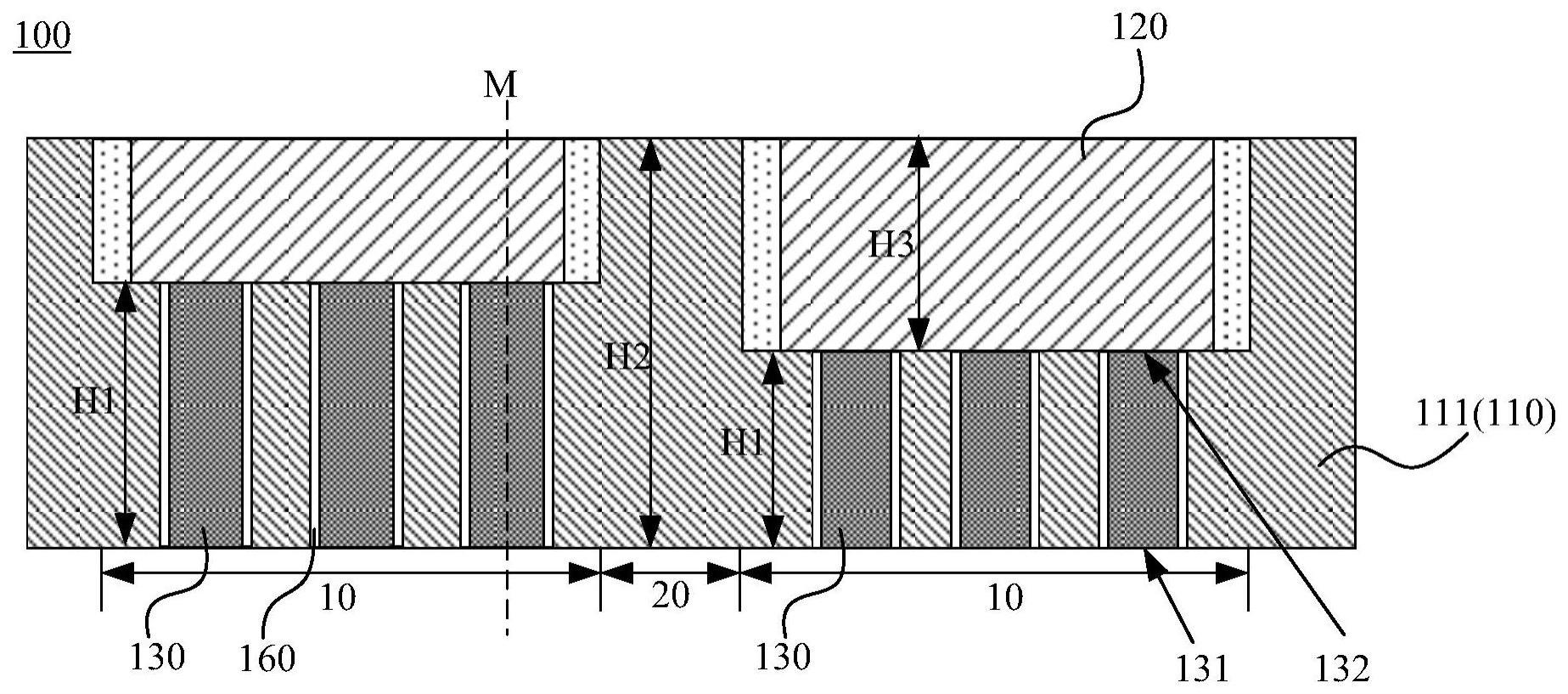

12、另一方面,本发明实施例提供了一种半导体结构。半导体结构包括半导体基底结构、第一半导体器件和至少一个导电柱。第一半导体器件部分贯穿所述半导体基底结构。至少一个导电柱部分贯穿所述半导体基底结构,具有沿所述导电柱延伸方向相对设置的第一端面和第二端面;所述第一端面与所述半导体基底结构远离所述第一半导体器件的表面基本齐平,所述第二端面与所述第一半导体器件接触且电连接。

13、在一些示例中,所述半导体基底结构包括第一基底;或者,所述半导体基底结构包括沿所述导电柱延伸方向层叠设置的第一基底和半导体层。

14、在一些示例中,所述半导体基底结构包括沿所述导电柱延伸方向层叠设置的所述第一基底和第一半导体层,所述导电柱贯穿所述第一基底,所述第一半导体器件贯穿所述第一半导体层;或者,所述半导体基底结构包括沿所述导电柱延伸方向层叠设置的第一基底和第二半导体层,所述导电柱贯穿所述第一基底,所述第一半导体器件贯穿所述第二半导体层且部分贯穿所述第一基底。

15、在一些示例中,所述半导体结构还包括第二半导体器件和第三半导体层;第二半导体器件贯穿所述第三半导体层;所述第三半导体层与所述半导体基底结构沿所述导电柱延伸方向层叠设置;所述导电柱的第二端面与所述第二半导体器件接触且电连接。

16、在一些示例中,所述第一半导体器件远离所述导电柱的表面与所述半导体基底结构远离所述导电柱的表面基本齐平;和/或,所述第二半导体器件远离所述导电柱的表面与所述第三半导体层远离所述导电柱的表面基本齐平。

17、在一些示例中,多个所述导电柱包括多组,一组所述导电柱的高度相同;不同组的所述导电柱的高度相同或不同。

18、在一些示例中,半导体结构还包括至少一个绝缘层,所述至少一个绝缘层中的一个包覆一个所述导电柱的侧壁。

19、本发明实施例提供的半导体结构中,导电柱与第一半导体器件沿导电柱延伸方向(即半导体基底结构厚度方向)依次排列设置,其中,至少一个导电柱部分贯穿半导体基底结构,导电柱的高度小于半导体基底结构的厚度;并且,第一半导体器件部分贯穿半导体基底结构,且与至少一个导电柱接触且电连接。这样,第一半导体器件能够稳定嵌设于半导体基底结构中,实现与导电柱的良好的接触和稳定的电性连接的效果。

20、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!