半导体装置、基座侧的半导体芯片以及粘贴侧的半导体芯片的制作方法

本公开涉及半导体装置、基座侧的半导体芯片以及粘贴侧的半导体芯片。

背景技术:

1、在专利文献1中公开了能够进行可靠性较高的倒装片安装的技术。另外,在专利文献2中公开了能够在将多个半导体集成电路芯片贴合的状态下检查半导体集成电路芯片间的电连接的技术。

2、专利文献1:日本特开2002-111148号公报

3、专利文献2:日本特开2004-20550号公报

4、此处,现有的检查半导体集成电路芯片间的电连接的检查方法是使半导体芯片具备的内部电路动作来进行检查,直到检查结束为止需要时间。

技术实现思路

1、因此,本公开的目的在于减少在将多个半导体芯片贴合的状态下检查半导体芯片间的电连接的检查时间。

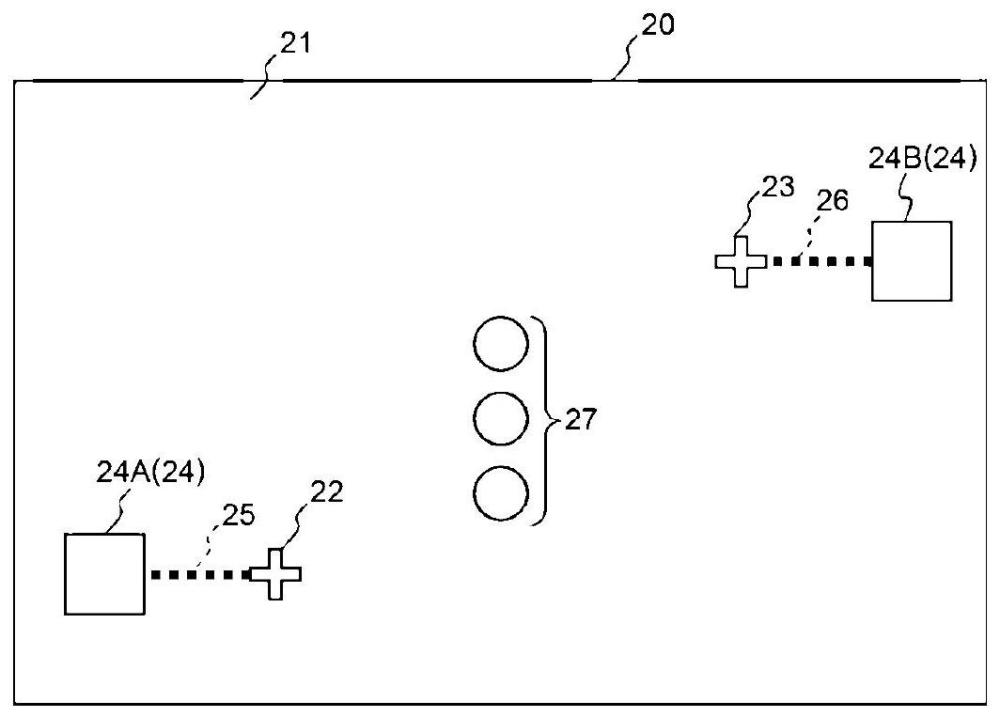

2、本公开的半导体装置具备:第一半导体芯片,设置有第一对准标记、第二对准标记、用于测定导通的第一端子及第二端子、将上述第一对准标记及上述第一端子电连接的布线、以及将上述第二对准标记及上述第二端子电连接的布线;和第二半导体芯片,设置有第三对准标记、第四对准标记、以及将上述第三对准标记及上述第四对准标记电连接的布线,并以上述第一对准标记及上述第三对准标记和上述第二对准标记及上述第四对准标记重叠的方式与上述第一半导体芯片贴合。

3、本公开的基座侧的半导体芯片具备:设置多个的基座侧的对准标记;用于测定导通的测定用端子;以及将上述基座侧的对准标记以及上述测定用端子电连接的布线,在以上述基座侧的对准标记和设置于粘贴侧的半导体芯片的多个粘贴侧的对准标记重叠的方式贴合有上述粘贴侧的半导体芯片的情况下,上述测定用端子能够进行导通的测定。

4、本公开的粘贴侧的半导体芯片设置有:设置多个的粘贴侧的对准标记;以及将上述粘贴侧的对准标记彼此电连接的布线,在以上述粘贴侧的对准标记和多个基座侧的对准标记重叠的方式与基座侧的半导体芯片贴合的情况下,上述布线将上述基座侧的对准标记彼此电连接,其中,上述基座侧的对准标记设置于上述基座侧的半导体芯片,并与用于测定导通的测定用端子电连接。

5、根据本公开,能够减少在将多个半导体芯片贴合的状态下检查半导体芯片间的电连接的检查时间。

技术特征:

1.一种半导体装置,具备:

2.根据权利要求1所述的半导体装置,其中,

3.根据权利要求1所述的半导体装置,其中,

4.根据权利要求1所述的半导体装置,其中,

5.一种基座侧的半导体芯片,具备:

6.一种粘贴侧的半导体芯片,设置:

技术总结

本公开的目的在于减少在将多个半导体芯片贴合的状态下检查半导体芯片间的电连接的检查时间。半导体装置具备:第一半导体芯片,设置有第一对准标记、第二对准标记、用于测定导通的第一端子及第二端子、将上述第一对准标记及上述第一端子电连接的布线、以及将上述第二对准标记及上述第二端子电连接的布线;和第二半导体芯片,设置有第三对准标记、第四对准标记、以及将上述第三对准标记及上述第四对准标记电连接的布线,并以上述第一对准标记及上述第三对准标记和上述第二对准标记及上述第四对准标记重叠的方式与上述第一半导体芯片贴合。

技术研发人员:池田淳一,本多一行

受保护的技术使用者:蓝碧石科技株式会社

技术研发日:

技术公布日:2024/4/8

- 还没有人留言评论。精彩留言会获得点赞!