电子元件的制作方法

本发明涉及一种包括芯片焊盘和从所述芯片焊盘延伸的悬垂端子的电子元件。

背景技术:

1、jp6938118 b2中公开的发明涉及一种电子元件,其包括芯片、芯片被固定在其上的芯片焊盘、从所述芯片焊盘延伸的悬垂端子以及电连接到所述芯片的引线端子,其中,所述悬垂端子具有从模制树脂中露出的露出面,并且该露出面被电绝缘层覆盖。

2、由于与所述芯片电连接的所述引线端子设置在悬垂端子附近,为了防止在施加高电压时所述引线端子与所述悬垂端子之间出现漏电起痕现象,所述悬垂端子具有覆盖有电绝缘层的露出面。

3、本发明的目的是提供一种电子元件,其包括具有未被电绝缘层覆盖的露出面的悬垂端子并且能够抑制漏电起痕现象。

技术实现思路

1、本发明一实施方式的电子元件包括:芯片;芯片焊盘,其上固定有所述芯片;悬垂端子,其从所述芯片焊盘延伸;引线端子,其与所述芯片电连接;以及虚设端子,其中,所述悬垂端子设置为比所述引线端子更靠近所述虚设端子。

2、本发明一实施方式的电子元件包括:芯片;芯片焊盘,其上固定有所述芯片;悬垂端子,其从所述芯片焊盘延伸;引线端子,其与所述芯片电连接;以及虚设端子,其中,所述悬垂端子用作所述虚设端子。

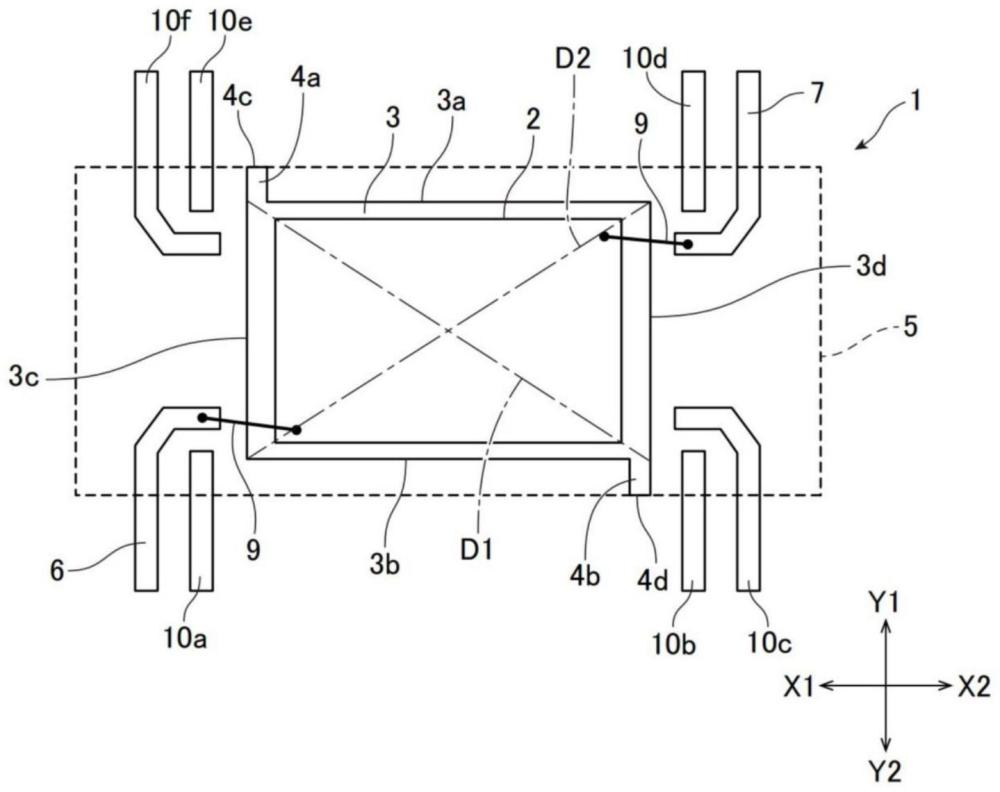

3、根据本发明的每个上述实施方式,优选地,基于在所述芯片焊盘的表面上相交的第一对角线和第二对角线,所述悬垂端子从与所述第一对角线相交的所述芯片焊盘的端部附近延伸,并且所述引线端子设置在与所述第二对角线相交的所述芯片焊盘的端部附近。

4、根据本发明的一实施方式,由于悬垂端子与引线端子之间的距离较长,因此可以利用具有未被绝缘树脂覆盖的露出面的悬垂端子来抑制漏电起痕现象。

技术特征:

1.一种电子元件,具备:

2.一种电子元件,具备:

3.根据权利要求1所述的电子元件,其特征在于,基于在所述芯片焊盘的表面上相交的第一对角线和第二对角线,所述悬垂端子从与所述第一对角线相交的所述芯片焊盘的端部附近延伸,并且所述引线端子被设置在与所述第二对角线相交的所述芯片焊盘的端部附近。

4.根据权利要求2所述的电子元件,其特征在于,基于在所述芯片焊盘的表面上相交的第一对角线和第二对角线,所述悬垂端子从与所述第一对角线相交的所述芯片焊盘的端部附近延伸,并且所述引线端子被设置在与所述第二对角线相交的所述芯片焊盘的端部附近。

技术总结

本发明一实施方式的电子元件包括:芯片;芯片焊盘,其上固定有所述芯片;悬垂端子,其从所述芯片焊盘延伸;引线端子,其与所述芯片电连接;以及虚设端子,其中,所述悬垂端子被设置为比所述引线端子更靠近所述虚设端子。

技术研发人员:久保田博史,小口友规

受保护的技术使用者:KOA株式会社

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!