一种逻辑晶体管及存储器

本公开涉及半导体,尤其涉及一种逻辑晶体管及存储器。

背景技术:

1、晶体管,是一种固体半导体器件,可以用于检波、整流、放大、开关、稳压、信号调制和许多其它功能。晶体管作为一种可变开关,基于输入的电压,控制流出的电流,因此晶体管可作为电流的开关,和一般机械开关不同处在于晶体管是利用电讯号来控制,而且开关速度可以非常之快,在实验室中的切换速度可达100ghz以上。

2、晶体管是逻辑电路中的核心部件。逻辑电路是一种离散信号的传递和处理,以二进制为原理、实现数字信号逻辑运算和操作的电路,主要分为组合逻辑电路和时序逻辑电路,由最基本的与门电路、或门电路和非门电路组成。

3、传统意义上的逻辑电路,为了实现不同的逻辑门运算,需要使用不同类型、不同种类、不同数目的晶体管,因此对于大面积制作逻辑电路的工艺提出了较高的要求,包括用不同的掩膜版、不同的工艺、不同的材料以及不同的设计,因此制造过程比较复杂,逻辑电路的成品率难以保证。

技术实现思路

1、本公开提供了一种逻辑晶体管及存储器,以至少解决现有技术中存在的以上技术问题。

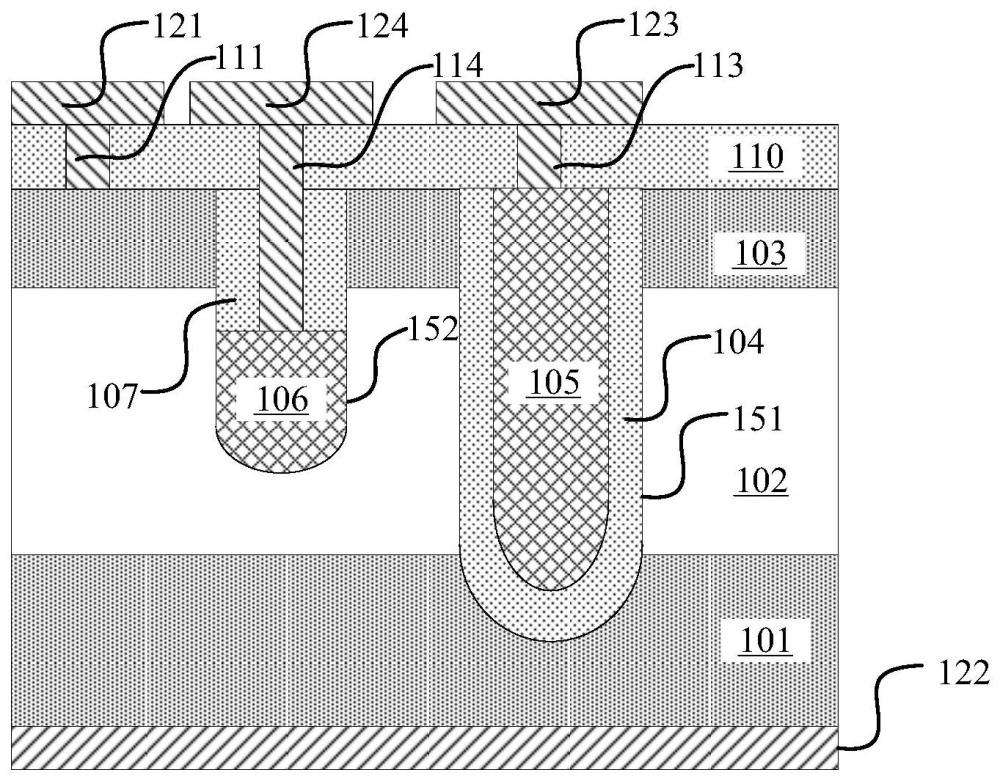

2、根据本公开的第一方面,提供了一种逻辑晶体管,包括:

3、半导体衬底;

4、位于所述半导体衬底上的半导体层;

5、至少一个部分位于所述半导体层内的第一沟槽,以及至少一个延伸至所述半导体层中的第二沟槽;

6、栅叠层,位于所述第一沟槽内;所述栅叠层包括覆盖所述第一沟槽的底部和侧壁的栅极介质层以及由所述栅极介质层包裹的栅极导体;

7、沟道控制电极,位于所述第二沟槽的内部,并与所述半导体层接触,以提取沟道局部电学性能作为输出的电极;其中,

8、所述半导体层位于所述第一沟槽和所述第二沟槽之间的部分形成为所述逻辑晶体管的沟道区,所述栅极导体为所述逻辑晶体管的输入端,所述沟道控制电极为所述逻辑晶体管的输出端。

9、在一可实施方式中,所述逻辑晶体管还包括:

10、位于所述半导体层中的导体区;其中,

11、所述半导体衬底和所述导体区分别形成为所述逻辑晶体管的源区和漏区。

12、在一可实施方式中,所述逻辑晶体管还包括:

13、覆盖所述沟道控制电极,并位于所述第二沟槽上部的第一绝缘层;其中,

14、所述沟道控制电极的顶面低于所述漏区的底面,所述第一绝缘层隔离所述沟道控制电极和所述漏区。

15、在一可实施方式中,所述逻辑晶体管还包括:

16、位于所述导体区上的第二绝缘层;

17、位于所述第二绝缘层上的漏极、栅极和控制栅极,以及位于所述半导体衬底的远离所述半导体层的表面上的源极;其中,

18、所述漏极与所述漏区电连接,所述栅极与所述栅极导体电连接,所述控制栅极与所述沟道控制电极电连接,所述源极与所述源区电连接。

19、在一可实施方式中,所述栅极导体为所述逻辑晶体管的输入端,所述沟道控制电极为所述逻辑晶体管的输出端,包括:

20、与所述栅极导体连接的所述栅极为所述逻辑晶体管的输入电极,与所述沟道控制电极连接的所述控制栅极为所述逻辑晶体管的输出电极。

21、在一可实施方式中,所述沟道控制电极,位于所述第二沟槽的内部,包括:所述沟道控制电极位于所述第二沟槽的下部。

22、在一可实施方式中,所述栅叠层包括一个栅叠层,根据对所述一个栅叠层的输入端的信号执行逻辑运算的结果,使所述逻辑晶体管操作为非门电路结构。

23、在一可实施方式中,所述栅叠层包括多个栅叠层,根据对所述多个栅叠层的输入端的信号执行逻辑运算的结果,使所述逻辑晶体管选择性地操作为与门电路结构、或门电路结构、与非门电路结构以及或非门电路结构中的任意一种。

24、在一可实施方式中,所述使所述逻辑晶体管选择性地操作为双输入逻辑门、多输入逻辑门、双输出逻辑门、多输出逻辑门结构中的任意一种,包括:使所述逻辑晶体管实现或非、与非、或、与、同或、异或逻辑功能中的任意一种。

25、在一可实施方式中,所述至少一个部分位于所述半导体层内的第一沟槽,包括:

26、所述第一沟槽贯穿所述半导体层并延伸至所述半导体衬底内,或者,

27、所述第一沟槽延伸至所述半导体层内。

28、在一可实施方式中,所述沟道控制电极包括一个沟道控制电极,所述一个沟道控制电极至少部分围绕所述栅叠层,以获得预定的结面积。

29、在一可实施方式中,所述沟道控制电极包括多个沟道控制电极,所述多个沟道控制电极间隔围绕所述栅叠层,并分别与所述半导体层接触,以形成多个结电容。

30、在一可实施方式中,所述至少一个沟道控制电极由选自导体、半导体、或导体与半导体的任意叠层组成。

31、在一可实施方式中,所述导体包括选自金属、合金、ito、掺杂硅、掺杂多晶硅、金属氮化物、金属硅化物中的至少一种。

32、在一可实施方式中,所述沟道控制电极通过掺杂工艺、或/和沉积工艺、或/和外延工艺、或/和自组装工艺、或/和旋涂工艺、或/和自组装工艺、或/和roll-to-roll工艺、或/和水热法工艺、或/和压印工艺、或/和滚压工艺、或/和打印工艺、或/和蒸镀工艺加工形成。

33、根据本公开的第二方面,提供了一种存储器,包括如上述实施方式中任一项所述的逻辑晶体管。

34、本公开的逻辑晶体管及存储器,通过以栅极导体作为输入端,以沟道控制电极作为输出端,通过改变输入端的电压改变沟道区的载流子密度从而改变输出端的输出状态,从而通过一个晶体管实现多种逻辑输出,即让同一个晶体管实现多个逻辑电路功能,例如与门、或门、与非门、或非门等,能够减少逻辑电路中晶体管的个数,使逻辑电路的制备方法简单,器件面积减少。并且本公开实施例提供的逻辑晶体管为垂直结构晶体管,逻辑晶体管的源区和漏区分别位于半导体层的相对表面上,不仅可以减小源区和漏区的总计芯片面积,而且可以减小栅极长度限制、布线更加灵活以及减小源极和漏极的总计布线面积。因此,对于每个存储单元而言,可以减小逻辑晶体管的单元尺寸,从而提高存储器的存储密度。

35、应当理解,本部分所描述的内容并非旨在标识本公开的实施例的关键或重要特征,也不用于限制本公开的范围。本公开的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种逻辑晶体管,其特征在于,包括:

2.根据权利要求1所述的逻辑晶体管,其特征在于,所述逻辑晶体管还包括:

3.根据权利要求2所述的逻辑晶体管,其特征在于,所述逻辑晶体管还包括:

4.根据权利要求3所述的逻辑晶体管,其特征在于,所述逻辑晶体管还包括:

5.根据权利要求4所述的逻辑晶体管,其特征在于,

6.根据权利要求1所述的逻辑晶体管,其特征在于,

7.根据权利要求1所述的逻辑晶体管,其特征在于,

8.根据权利要求1所述的逻辑晶体管,其特征在于,

9.根据权利要求8所述的逻辑晶体管,其特征在于

10.根据权利要求1所述的逻辑晶体管,其特征在于,

11.根据权利要求1所述的逻辑晶体管,其特征在于,

12.根据权利要求1所述的逻辑晶体管,其特征在于,

13.根据权利要求1所述的逻辑晶体管,其特征在于,

14.根据权利要求13所述的逻辑晶体管,其特征在于,

15.根据权利要求1所述的逻辑晶体管,其特征在于,所述沟道控制电极通过掺杂工艺、或/和沉积工艺、或/和外延工艺、或/和自组装工艺、或/和旋涂工艺、或/和自组装工艺、或/和roll-to-roll工艺、或/和水热法工艺、或/和压印工艺、或/和滚压工艺、或/和打印工艺、或/和蒸镀工艺加工形成。

16.一种存储器,其特征在于,包括如上述权利要求1-15中任一项所述的逻辑晶体管。

技术总结

本公开提供了一种逻辑晶体管即存储器,其中,所述逻辑晶体管包括:半导体衬底;位于所述半导体衬底上的半导体层;至少一个部分位于所述半导体层内的第一沟槽,以及至少一个延伸至所述半导体层中的第二沟槽;栅叠层,位于所述第一沟槽内;所述栅叠层包括覆盖所述第一沟槽的底部和侧壁的栅极介质层以及由所述栅极介质层包裹的栅极导体;沟道控制电极,位于所述第二沟槽的内部,并与所述半导体层接触,以提取沟道局部电学性能作为输出的电极;其中,所述半导体层位于所述第一沟槽和所述第二沟槽之间的部分形成为所述逻辑晶体管的沟道区,所述栅极导体为所述逻辑晶体管的输入端,所述沟道控制电极为所述逻辑晶体管的输出端。

技术研发人员:戴明志,薛志彪

受保护的技术使用者:中国科学院宁波材料技术与工程研究所

技术研发日:

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!