用于异质管芯集成应用的具有EMIB和玻璃芯的混合扇出架构的制作方法

本公开的实施例涉及电子封装,并且更具体地,涉及具有带有玻璃芯的多个互连的管芯的电子封装。

背景技术:

1、对于单片管芯的尺寸,常规的管芯制造技术正在被推向它们的极限,然而,应用却渴望使用最新技术(例如,7nm栅极长度)实现大尺寸集成电路的能力。随着单片管芯变大,对于较小的管芯可以忽略不计的微小差异无法弥补,并且可能常常会大大减小良率。当前的解决方案可能涉及使用与半导体内插器互连或与嵌入在硅衬底中的硅桥集成的较小的集成电路,以提供异质芯片封装。

2、在涉及多个管芯与硅桥的集成的实施例中,管芯通过桥通信耦合以便提供期望的功能,但是封装中增加的复杂性是显著的挑战。例如,管芯、管芯背侧膜(dbf)、堆积电介质层、和包封材料之间的cte不匹配会导致显著的管芯翘曲。在使用该方法来使铜柱和管芯背侧互连(穿硅过孔,tsv)显露的大多数架构方式所需的平面化操作期间,这尤其是有问题的。管芯翘曲阻止铜柱和管芯互连两者在不去除管芯的绝大部分的情况下不能根据需要同时被暴露,从而导致良率降低。减小所涉及的材料的cte不匹配可以减小管芯翘曲,但由于材料配方限制,因此不能完全消除翘曲。

技术实现思路

技术特征:

1.一种电子器件封装,包括:

2.根据权利要求1所述的电子器件封装,其中,所述芯是玻璃芯。

3.根据权利要求1所述的电子器件封装,其中,所述包封层围绕所述桥管芯。

4.根据权利要求1所述的电子器件封装,其中,所述芯具有的垂直厚度大于所述桥管芯的垂直厚度。

5.根据权利要求1所述的电子器件封装,其中,所述第一导电过孔和所述第二导电过孔一直延伸穿过所述芯。

6.根据权利要求1所述的电子器件封装,其中,所述芯具有的cte与所述包封层的cte基本相同。

7.根据权利要求1所述的电子器件封装,其中,所述芯具有的厚度在50-150微米的范围内。

8.根据权利要求1所述的电子器件封装,其中,所述包封层垂直地位于所述桥管芯之上。

9.根据权利要求1所述的电子器件封装,其中,所述桥管芯包括多个穿硅过孔(tsv),所述多个tsv耦合到所述再分布层。

10.根据权利要求1所述的电子器件封装,其中,所述包封层具有与所述第一管芯或所述第二管芯中的一个或两个的最上表面共面的最上表面。

11.根据权利要求1所述的电子器件封装,其中,所述第一管芯通过第一多个第一级互连耦合到所述桥管芯,并且所述第二管芯通过第二多个第一级互连耦合到所述桥管芯。

12.一种电子器件封装,包括:

13.根据权利要求12所述的电子器件封装,其中,所述多个堆积层包括多个导电迹线和过孔。

14.根据权利要求12所述的电子器件封装,其中,所述芯材料包括玻璃。

15.根据权利要求12所述的电子器件封装,其中,所述芯材料具有的垂直厚度大于所述第一管芯的垂直厚度,并且其中,所述第一导电过孔和所述第二导电过孔一直延伸穿过所述芯材料。

16.一种系统,包括:

17.根据权利要求16所述的系统,还包括:

18.根据权利要求16所述的系统,还包括:

19.根据权利要求16所述的系统,还包括:

20.根据权利要求16所述的系统,还包括:

技术总结

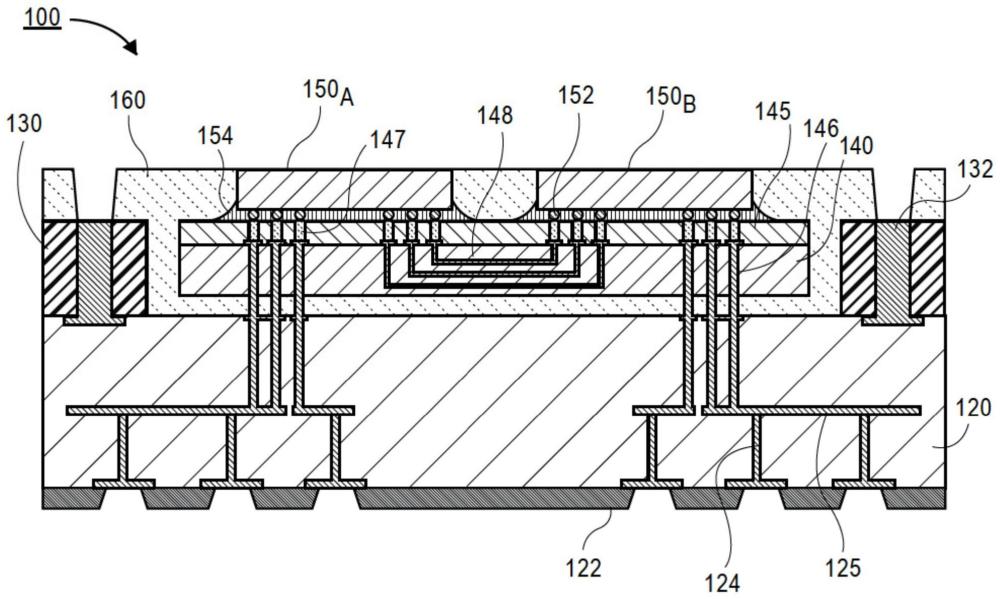

本发明涉及用于异质管芯集成应用的具有EMIB和玻璃芯的混合扇出架构。本文公开的实施例包括电子封装以及形成这样的封装的方法。在实施例中,微电子器件封装可以包括再分布层(RDL)和RDL之上的内插器。在实施例中,玻璃芯可以形成在RDL之上并且包围内插器。在实施例中,微电子器件封装还可以包括内插器之上的多个管芯。在实施例中,多个管芯与内插器通信耦合。

技术研发人员:S·皮耶塔姆巴拉姆,R·马内帕利,段刚

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/5

- 还没有人留言评论。精彩留言会获得点赞!