一种功率芯片、功率芯片制作方法及功率因数校正电路与流程

本发明涉及集成电路应用领域,尤其涉及一种功率芯片、功率芯片制作方法及功率因数校正电路。

背景技术:

1、传统的分立器件设计通常会占用较大的电路板面积,这不仅增加了电路设计的成本,也可能导致散热问题。因此,需要一种能够减小分立器件在功率因数校正(powerfactor correction,pfc)电路上的占板面积的解决方案。

技术实现思路

1、鉴于以上现有技术存在的问题,本发明提出一种功率芯片、功率芯片制作方法及功率因数校正电路,主要解决现有的功率器件占板面积大导致成本高的问题。

2、为了实现上述目的及其他目的,本发明采用的技术方案如下。

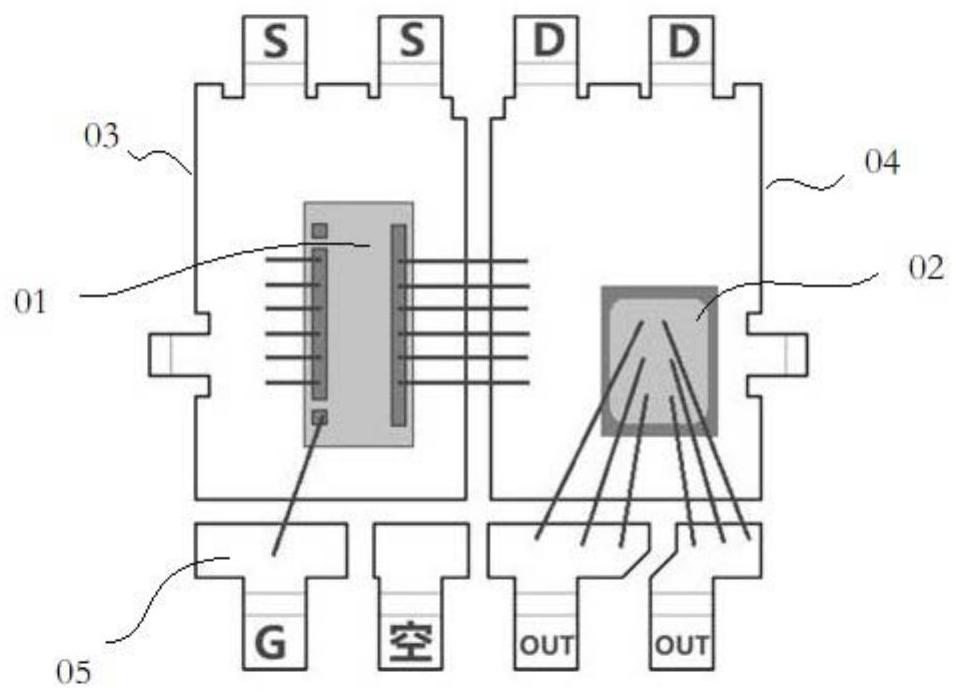

3、本申请提供一种功率芯片,包括:晶体管和二极管;框架,其包括相互独立的第一基岛和第二基岛,所述晶体管设置于所述第一基岛上,且所述晶体管的源极与所述第一基岛电性连接,所述二极管设置于所述第二基岛上,所述二极管的正端分别连接所述第二基岛和所述晶体管的漏极,所述二极管的负端作为输出端;金属引脚,设置于所述框架的侧方,以引出所述晶体管的栅极和所述输出端;封装体,用于覆盖所述第一基岛、所述第二基岛、所述晶体管以及所述二极管。

4、在本申请一实施例中,所述晶体管包括氮化镓高电子迁移率晶体管。

5、在本申请一实施例中,所述二极管包括碳化硅二极管。

6、在本申请一实施例中,所述第一基岛包括至少一个源电极,在完成封装后,通过所述源电极引出所述晶体管的源极。

7、在本申请一实施例中,所述第二基岛包括至少一个漏电极,所述晶体管的漏极通过键合线与所述第二基岛键合,以在完成封装后通过所述漏电极引出所述所述晶体管的漏极。

8、在本申请一实施例中,所述晶体管的栅极和所述二极管的负端分别通过键合线与对应的金属引脚键合。

9、在本申请一实施例中,所述封装体包括dfn封装。

10、本申请还提供一种功率芯片制作方法,包括:提供晶体管、二极管、金属引脚和框架,所述框架包括相互独立的第一基岛和第二基岛;将所述晶体管设置于所述第一基岛上,所述晶体管的源极与所述第一基岛电性连接;将所述二极管设置于所述第二基岛上,所述二极管的正端分别连接所述第二基岛和所述晶体管的漏极,所述二极管的负端作为输出端;将所述晶体管的栅极和所述输出端分别引出到对应的金属引脚上;通过注塑封装形成封装体以覆盖所述第一基岛、所述第二基岛、所述晶体管以及所述二极管。

11、本申请还提供一种功率因数校正电路,包括:功率芯片;整流模块,用于对输入交流电压进行整流,得到直流电压;所述整流模块输出的直流电压由所述功率芯片的漏电极流入,从所述功率芯片的输出端输出至直流电源。

12、如上所述,本发明提出的一种功率芯片、功率芯片制作方法及功率因数校正电路,具有以下有益效果。

13、本申请通过将功率校正电路的晶体管和二极管合封在一起,不仅减少了对应器件在pfc电路上的占板面积,还可提高器件之间的集成度,从而提高整体电路的性能;此外采用两个基岛的框架,可实现更好的导热和电绝缘,提高芯片的稳定性和可靠性。

技术特征:

1.一种功率芯片,其特征在于,包括:

2.根据权利要求1所述的功率芯片,其特征在于,所述晶体管包括氮化镓高电子迁移率晶体管。

3.根据权利要求1所述的功率芯片,其特征在于,所述二极管包括碳化硅二极管。

4.根据权利要求1所述的功率芯片,其特征在于,所述第一基岛包括至少一个源电极,在完成封装后,通过所述源电极引出所述晶体管的源极。

5.根据权利要求1所述的功率芯片,其特征在于,所述第二基岛包括至少一个漏电极,所述晶体管的漏极通过键合线与所述第二基岛键合,以在完成封装后通过所述漏电极引出所述所述晶体管的漏极。

6.根据权利要求1所述的功率芯片,其特征在于,所述晶体管的栅极和所述二极管的负端分别通过键合线与对应的金属引脚键合。

7.根据权利要求1所述的功率因数校正电路的功率芯片,其特征在于,所述封装体包括dfn封装。

8.一种功率芯片制作方法,其特征在于,包括:

9.一种功率因数校正电路,其特征在于,包括:

技术总结

本申请提供一种功率芯片、功率芯片制作方法及功率因数校正电路,该功率芯片包括:晶体管和二极管;框架,其包括相互独立的第一基岛和第二基岛,所述晶体管设置于所述第一基岛上,且所述晶体管的源极与所述第一基岛电性连接,所述二极管设置于所述第二基岛上,所述二极管的正端分别连接所述第二基岛和所述晶体管的漏极,所述二极管的负端作为输出端;金属引脚,设置于所述框架的侧方,以引出所述晶体管的栅极和所述输出端;封装体,用于覆盖所述第一基岛、所述第二基岛、所述晶体管以及所述二极管。本申请可有效减少PFC电路中器件的占板面积,提高器件的稳定性。

技术研发人员:陈云乔,顾璐,成亮,张航,敖华阳,陈苗,简洋,周玉凤,王瀚

受保护的技术使用者:重庆平伟实业股份有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!