一种亚微米源漏的宽禁带半导体HEMT器件及其制作方法与流程

本发明涉及半导体器件,具体涉及一种亚微米源漏的宽禁带半导体hemt器件及其制作方法。

背景技术:

1、宽禁带半导体材料具有禁带宽度大、击穿场强高、迁移率高的特点,使得hemt器件在高压和高频领域具有很大优势。随着移动无线通信技术以及雷达技术的发展,对器件频率、效率、带宽以及功率的要求进一步提高,宽禁带半导体材料的电学特性非常适合用于制作新一代大功率微波毫米波和太赫兹器件。

2、随着高电子迁移率晶体管工作频率的不断提高,器件尺寸也进行等比例的缩小,因此器件制造面临极大挑战。

3、

4、

5、

6、根据公式(2)和(3)可知,增加跨导gm,可以提高ft和fmax;根据公式(1),通过降低膝点电压vknee可以有效提高gm,进而提高ft和fmax。然而受光刻工艺影响,源漏尺寸一般大于1.5μm,很难进一步降低尺寸。因此,通过缩短源漏间距方案,来降低沟道寄生,改善vknee的研究方案很少。

7、本发明提出一种亚微米源漏间距的ga2o3 hemt及其制作方法,源漏间距小于1μm,对提高ft和fmax十分有意义。

技术实现思路

1、基于上述表述,本发明提供了一种亚微米源漏的宽禁带半导体hemt器件及其制作方法,以通过缩短源漏间距来降低沟道寄生,改善vknee,以提高hemt器件的频率特性。

2、本发明解决上述技术问题的技术方案如下:

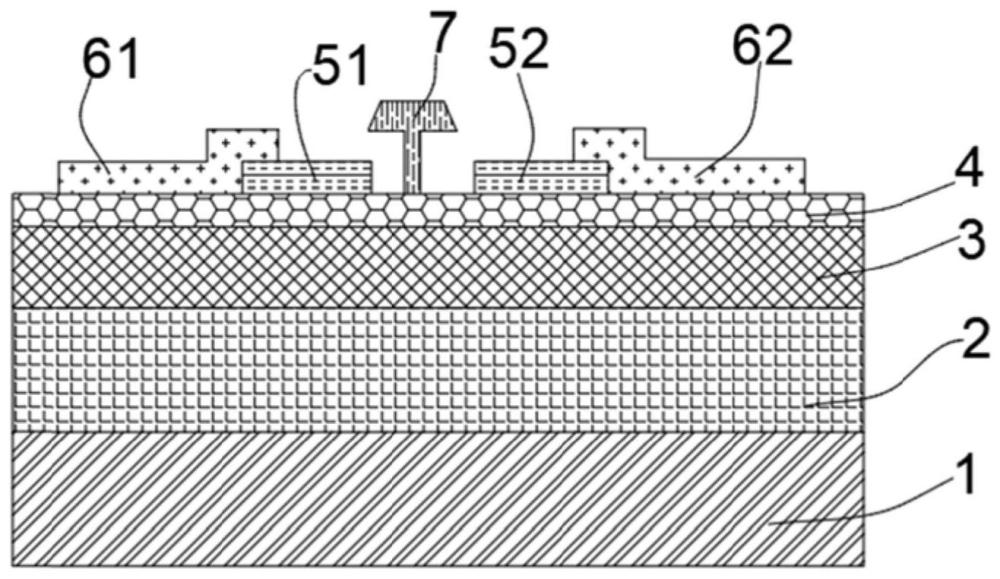

3、第一方面,本发明提供一种亚微米源漏的宽禁带半导体hemt器件,包括:衬底、缓冲层、沟道层、势垒层、第一欧姆金属层及第二欧姆金属层;

4、所述沟道层、所述缓冲层和所述势垒层依次叠加设置于所述衬底上;

5、所述第一欧姆金属层包括第一欧姆金属部和第二欧姆金属部,所述第一欧姆金属部和所述第二欧姆金属部均布设于所述势垒层上,所述第一欧姆金属部与所述第二欧姆金属部之间存在第一间距;

6、所述第二欧姆金属层包括第三欧姆金属部和第四欧姆金属部,所述第三欧姆金属部和所述第四欧姆金属部均布设于所述势垒层上,且所述第三欧姆金属部与所述第一欧姆金属部部分交叠重合,所述第四欧姆金属部与所述第二欧姆金属部部分交叠重合。

7、在上述技术方案的基础上,本发明还可以做如下改进。

8、进一步的,所述第一间距为小于1μm。

9、进一步的,所述第三欧姆金属部和所述第四欧姆金属部的单侧截面均呈阶梯状。

10、进一步的,所述第三欧姆金属部与所述第一欧姆金属部的交叠重合区域为0.5~2μm。

11、进一步的,所述第四欧姆金属部与所述第二欧姆金属部的交叠重合区域为0.5~2μm。

12、进一步的,所述第一欧姆金属部和所述第三欧姆金属部作为源极;所述第二欧姆金属部和所述第四欧姆金属部作为漏极。

13、进一步的,所述亚微米源漏的宽禁带半导体hemt器件还包括栅极;

14、所述栅极设于所述第一间距处,且与所述势垒层接触。

15、进一步的,所述栅极为t型栅。

16、第二方面,本发明还提供一种用于制作如第一方面所述的亚微米源漏的宽禁带半导体hemt器件的制作方法,包括:

17、在衬底层上依次外延生长缓冲层、沟道层和势垒层;

18、在所述势垒层上旋涂两层电子束胶,对第一欧姆区域进行曝光显影,蒸镀金属后剥离,形成第一欧姆金属层;

19、在所述势垒层和所述第一欧姆金属层上旋涂正胶,对第二欧姆区域进行曝光显影,蒸镀金属后剥离,形成第二欧姆金属层。

20、在上述技术方案的基础上,本发明还可以做如下改进。

21、进一步的,在形成第二欧姆金属层之后,还包括:

22、退火处理后,进行光刻胶掩膜,注入b离子隔离后去胶;

23、旋涂双层胶后,曝光显影制备t型栅。

24、与现有技术相比,本申请的技术方案具有以下有益技术效果:

25、本发明提供的亚微米源漏的宽禁带半导体hemt器件通过设置衬底、缓冲层、沟道层、势垒层、第一欧姆金属层及第二欧姆金属层,其中,第一欧姆金属层包括第一欧姆金属部和第二欧姆金属部,第一欧姆金属部和第二欧姆金属部均布设于势垒层上,第一欧姆金属部与第二欧姆金属部之间存在第一间距;第二欧姆金属层包括第三欧姆金属部和第四欧姆金属部,第三欧姆金属部和第四欧姆金属部均布设于势垒层上,且第三欧姆金属部与第一欧姆金属部部分交叠重合,第四欧姆金属部与第二欧姆金属部部分交叠重合。

26、相较于现有技术,本发明提供的亚微米源漏的宽禁带半导体hemt器件及其制作方法具有如下优点:由第一欧姆金属层及第二欧姆金属层形成的源漏电极为双层欧姆金属交叠形成,能够实现缩小源漏间距小于1μm的水平,对提高hemt器件的频率特性有重要作用,具有低成本高效率的优势。

技术特征:

1.一种亚微米源漏的宽禁带半导体hemt器件,其特征在于,包括:衬底、缓冲层、沟道层、势垒层、第一欧姆金属层及第二欧姆金属层;

2.根据权利要求1所述的亚微米源漏的宽禁带半导体hemt器件,其特征在于,所述第一间距为小于1μm。

3.根据权利要求1所述的亚微米源漏的宽禁带半导体hemt器件,其特征在于,所述第三欧姆金属部和所述第四欧姆金属部的单侧截面均呈阶梯状。

4.根据权利要求3所述的亚微米源漏的宽禁带半导体hemt器件,其特征在于,所述第三欧姆金属部与所述第一欧姆金属部的交叠重合区域为0.5~2μm。

5.根据权利要求3所述的亚微米源漏的宽禁带半导体hemt器件,其特征在于,所述第四欧姆金属部与所述第二欧姆金属部的交叠重合区域为0.5~2μm。

6.根据权利要求1所述的亚微米源漏的宽禁带半导体hemt器件,其特征在于,所述第一欧姆金属部和所述第三欧姆金属部作为源极;所述第二欧姆金属部和所述第四欧姆金属部作为漏极。

7.根据权利要求1所述的亚微米源漏的宽禁带半导体hemt器件,其特征在于,所述亚微米源漏的宽禁带半导体hemt器件还包括栅极;

8.根据权利要求7所述的亚微米源漏的宽禁带半导体hemt器件,其特征在于,所述栅极为t型栅。

9.一种用于制作如权利要求1至8任一项所述的亚微米源漏的宽禁带半导体hemt器件的制作方法,其特征在于,包括:

10.根据权利要求9所述的制作方法,其特征在于,在形成第二欧姆金属层之后,还包括:

技术总结

本发明涉及半导体器件技术领域,提供一种亚微米源漏的宽禁带半导体HEMT器件及其制作方法,HEMT器件包括衬底、缓冲层、沟道层、势垒层、第一欧姆金属层及第二欧姆金属层;第一欧姆金属层包括第一欧姆金属部和第二欧姆金属部,第一欧姆金属部和第二欧姆金属部均布设于势垒层,第一欧姆金属部与第二欧姆金属部之间存在第一间距;第二欧姆金属层包括第三欧姆金属部和第四欧姆金属部,第三欧姆金属部与第一欧姆金属部部分交叠重合,第四欧姆金属部与第二欧姆金属部交叠重合。该HEMT器件的第一欧姆金属层及第二欧姆金属层形成的源漏电极为双层欧姆金属交叠形成,能够实现缩小源漏间距至小于1μm,对提高器件的频率特性有重要作用,具有低成本高效率的优势。

技术研发人员:李程程,吴畅,刘安,王凯,刘捷龙

受保护的技术使用者:湖北九峰山实验室

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!