形成集成电路的方法与流程

本发明实施例涉及一种形成集成电路的方法。

背景技术:

1、三维集成电路(3dic)组件可以包含两个或更多个垂直堆叠并且沿着接合线接合集成电路(ic)管芯。3dic组件可以通过使用晶圆接合操作,诸如晶圆上晶圆(wow)接合操作,将包含两个或更多个ic管芯的两个或更多个半导体衬底的堆叠来形成之。在接合操作之后,可以从两个或更多个半导体衬底的堆叠切割出包含两个或更多个ic管芯的3dic组件并将其封装在半导体管芯封装中。

技术实现思路

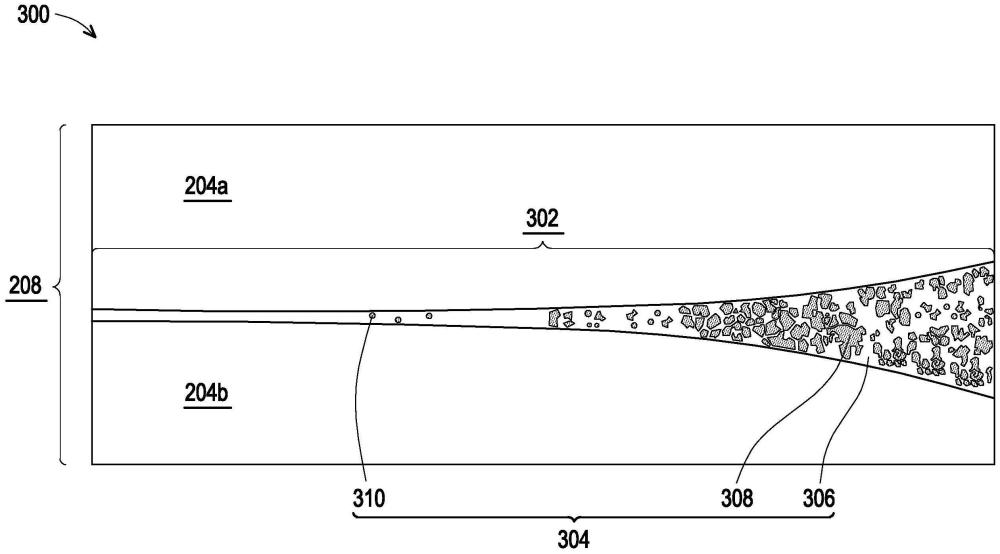

1、依据本发明实施例,一种形成集成电路的方法,包括以下步骤。在第一半导体衬底上形成第一集成电路管芯。在第二半导体衬底上形成第二集成电路管芯。通过连接所述第一半导体衬底和所述第二半导体衬底形成半导体衬底的堆叠。在所述半导体衬底的堆叠之间的倾斜边缘的侧向间隙区中形成支撑填充混合物,所述支撑填充混合物包括与第一尺寸范围的第一复合颗粒和第二尺寸范围的第二复合颗粒混合的密封剂。所述第一尺寸范围的中值小于所述第二尺寸范围的中值。从所述半导体衬底的堆叠中移除包含所述第二集成管芯连接的所述第一集成电路管芯的集成电路管芯的堆叠。

2、依据本发明实施例,一种形成集成电路的方法,包括以下步骤。在第一半导体衬底上形成第一集成电路管芯。在第二半导体衬底上形成第二集成电路管芯。通过连接所述第一半导体衬底和所述第二半导体衬底形成半导体衬底的堆叠。在所述半导体衬底的堆叠的倾斜边缘之间的侧向间隙区中形成支撑填充混合物,所述支撑填充混合物包括与近似第一形状的第一复合颗粒和近似第二形状的第二复合颗粒混合的密封剂。所述第二形状不同于所述第一形状。从所述半导体衬底的堆叠中移除包含与所述第二集成管芯连接的所述第一集成电路管芯的集成电路管芯的堆叠。

3、依据本发明实施例,一种形成集成电路的方法,包括以下步骤。连接两个或多个半导体衬底,以形成两个或多个半导体衬底的堆叠。在所述两个或多个半导体衬底的堆叠的倾斜边缘之间的侧向间隙区中形成包括第一复合颗粒和第二复合颗粒的支撑填充混合物。所述第一复合颗粒的第一尺寸范围的第一中值大于所述第二复合颗粒的第二尺寸范围的第二中值。薄化所述两个或更多半导体衬底的堆叠的顶部半导体衬底。

技术特征:

1.一种形成集成电路的方法,其特征在于,包括:

2.根据权利要求1所述的形成集成电路的方法,其特征在于,其中所述第一尺寸范围对应于约0.7微米至约2.5微米的范围,所述第二尺寸范围对应于约0.4微米至约1.0微米的范围。

3.根据权利要求1所述的形成集成电路的方法,其特征在于,其中所述侧向间隙区包括:

4.根据权利要求1所述的形成集成电路的方法,其特征在于,其中:

5.一种形成集成电路的方法,其特征在于,包括:

6.根据权利要求5所述的形成集成电路的方法,其特征在于,其中所述第一形状对应于具有光滑曲率的近似圆形,所述第二形状对应于包括至少一个具有锯齿轮廓的表面的多表面形状。

7.根据权利要求5所述的形成集成电路的方法,其特征在于,其中所述第一复合颗粒的第一浓度与所述第二复合颗粒的第二浓度的比率随着所述侧向间隙区内的侧向的位置改变。

8.一种形成集成电路的方法,其特征在于,包括:

9.根据权利要求8所述的形成集成电路的方法,其特征在于,还包括:

10.根据权利要求8所述的形成集成电路的方法,其特征在于,其中形成所述支撑填充混合物包括:

技术总结

本文描述的一些实施包括形成集成电路的方法。此方法包括使用支撑填充混合物,其包括在半导体衬底的堆叠的侧向间隙区中以及沿着半导体衬底的堆叠的周边区的各种类型的复合颗粒的组合。组合中包含的一种类型的复合颗粒可以是尺寸相对较小,并包含光滑的表面,可允许复合颗粒深入到侧向间隙区中。包含多种类型的复合颗粒组合的支撑填充混合物的特性可以控制下游制造期间的热诱导应力,以减少支撑填充混合物及/或半导体衬底的堆叠中出现缺陷的可能性。

技术研发人员:吴国铭,杨开云,陈昇照,萧豪毅,杨哲维,蔡正原,喻中一

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!