一种电容及其制备方法与流程

本发明涉及的电容制备,尤其涉及一种电容及其制备方法。

背景技术:

1、高稳态存储器是在逻辑芯片基础上,使用high-k铁电材料作为电容介质,利用铁电材料极性实现存储功能的一种新型存储器,其电容结构采用内嵌方式,在顶层绕线层嵌入铁电电容;而铁电电容作为核心存储器件,首先在介电层上刻蚀深孔,然后依次填入金属阻隔层,下电极层,high-k层,上电极等。由于cell孔深宽比大于10:1,使用常规的掩膜的光刻及干刻方案,孔内会有光刻胶残留无法去除干净,从而可能导致膜层附着力变差以及产品污染等风险。

2、因此只能用无掩膜方案直接进行干刻去除表面电极材料。而无掩膜版方案主要是根据等离子刻蚀过程中的负载效应来实现的,也就是单位面积内反应气体分子数相同,而深孔等于增大了刻蚀面积,所以深孔内刻蚀速远远小于相同位置晶圆表面刻蚀速率,利用刻蚀速率差达到表面刻蚀,孔内膜层保留的目的。由于在进行干刻工艺时,cell孔内的薄膜虽然刻蚀速度较慢,但是也会减薄,针对上下电极板来说,为了保证刻蚀后膜层连续,通常需要增加氮化钛的厚度。

3、但对于电介质层的高介电铁电材料,根据电容公式c=εa/d,ε是介质电容常数,a表示平行板面积,d表示平行板间距,介质层厚度d直接影响电容,无掩膜干刻对介质层造成的刻蚀不均匀会直接影响电容特性,因此需要尽量避免此道工序的无掩膜刻蚀。

4、所以为了改善现有制程中频繁使用无掩膜干刻的问题,作出能够取代现有铁电电容制程中的上下电极以及电容介电层无掩膜刻蚀工艺,并且取消上电极板。

技术实现思路

1、鉴于上述现有2.5d铁电电容存在的孔内会有光刻胶残留无法去除干净,从而导致膜层附着力变差以及产品污染风险问题,提出了本发明。

2、因此,本发明目的是提供一种2.5d铁电电容,其目的在于:通过结构防止孔内无残留污染。

3、为解决上述技术问题,本发明提供如下技术方案:包括电容孔、下电极、上电极和填充空间,其中下电极,其设置于所述介电层上的电容孔内,并在所述下电极的上部形成填充空间;上电极,其填充于所述填充空间内,并与所述下电极之间形成隔绝,并于所述上电极及晶圆表面处形成介质;板线,其沉积于介质表面,所述板线驱动连接一端仅穿过介质与晶圆表面与驱动线相连,另一端仅穿过介质与同一阵列内的上电极相连。

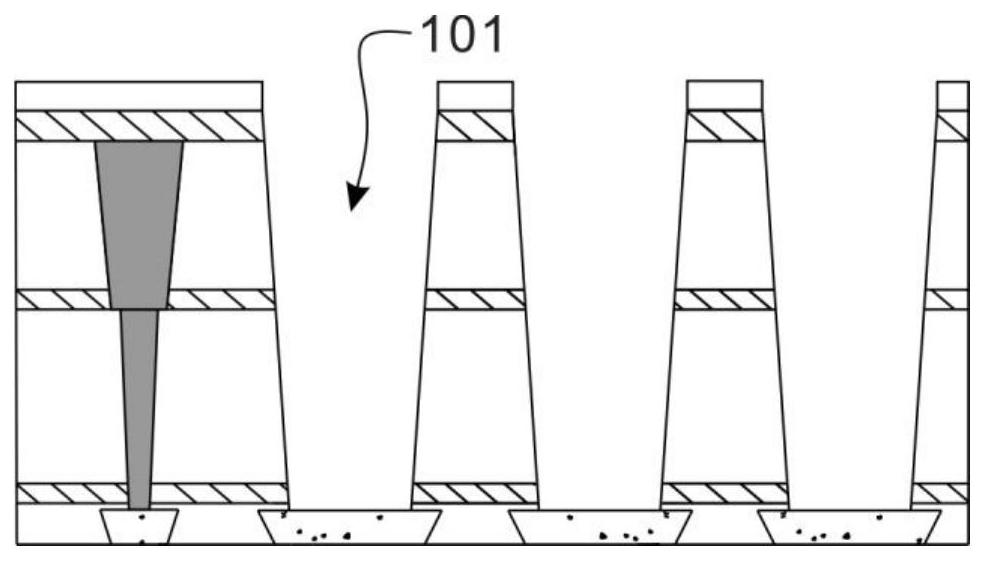

4、作为本发明所述2.5d铁电电容的一种优选方案,其中:存储单元,其包括开设于介电层上的立体电容孔、设置于所述立体电容孔内表面的阻隔层、设置在所述阻隔层上的下电极、设置于所述下电极内表面的高介电材料层、设置在所述高介电材料层内表面的种子层、设置在种子层上的上电极、设置在晶圆表面的介质层,以及设置在介质层上并延伸至上电极处连接的板线;

5、所述板线一端还与介电层内的驱动线相连。

6、作为本发明所述2.5d铁电电容的一种优选方案,其中:所述立体电容孔的孔径小于200nm;

7、所述阻隔层、下电极和高介电材料层的厚度均为9~12nm,所述阻隔层为氮化钽材料,所述下电极为氮化钽材料,所述高介电材料层采用铁电材料;

8、所述上电极为铜材料;

9、所述板线为钛与铝材料叠加形成。

10、作为本发明所述2.5d铁电电容的一种优选方案,其中:所述立体电容孔的孔径优选150nm;

11、所述阻隔层、下电极和高介电材料层的厚度优选为10nm;

12、所述上电极为2000nm的铜材料;

13、所述介质层为厚度2000nm的二氧化硅材料;

14、所述板线为150nm的钛、2000nm的铝和150nm的钛叠加形成。

15、本发明2.5d铁电电容的有益效果:通过增加介质层,利用介质层开孔以及板线进行跳线,实现板线与驱动线相连,减少了聚酰亚胺pi工艺和重布线层工艺流程。

16、鉴于上述现有2.5d铁电电容制备方法存在无掩膜干刻对介质层造成的刻蚀不均匀会直接影响电容特性的问题,提出了本发明。

17、因此,本发明目的是提供一种2.5d铁电电容制备方法,其目的在于:整体工艺流程缩短,减少多道干刻刻蚀工艺。

18、为解决上述技术问题,本发明提供如下技术方案:在电容的下电极沉积之后,填充电容孔并研磨去除晶圆表面多余材料,以形成上电极,并使得所述上电极与所述下电极形成隔绝。

19、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述电容的上电极与下电极之间沉积有介电层。

20、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:通过电镀填充电容孔并研磨去除晶圆表面多余材料,所述下电极与上电极之间设置有种子层,所述种子层与所述上电极贴合。

21、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:在立体电容孔及晶圆表面连续沉积阻隔层、下电极、高介电材料层和种子层,于种子层上通过电镀上电极并填充立体电容孔,利用研磨去除晶圆表面多余材料。

22、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:于介电层上制备立体电容孔并沉积出阻隔层、下电极、高介电材料层和种子层;

23、于种子层处进行电镀上电极并进行研磨后,制备介质层并进行光刻和刻蚀;

24、通过沉积板线后进行光刻和刻蚀。

25、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述制备方法具体为:

26、于存储单元的介电层上制备立体电容孔,并在晶圆表面和立体电容孔中连续沉积阻隔层、下电极、高介电材料层和上电极种子层;

27、于上电极处进行电镀并填充立体电容孔内部,通过研磨将晶圆表面的阻隔层、下电极、高介电材料层和上电极种子层去除;

28、于晶圆表面沉积介质层进行光刻和刻蚀后,沉积板线;

29、将板线进行光刻和刻蚀。

30、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述立体电容孔于存储单元的介电层上利用干刻形成的圆柱孔,其孔径为小于200nm。

31、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述介电层为氧化硅和氮化硅的叠加组合成厚度1200nm的晶圆层,所述立体电容孔的孔径为150nm。

32、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述隔离层采用原子层沉积的方式沉积一层厚度为10nm的氮化钽薄膜,防止金属于介电层中扩散。

33、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述所述下电极采用原子层沉积的方式在阻挡层上沉积一层厚度为10nm的氮化钛作为电容的下电极板。

34、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述高介电材料层采用原子层沉积的方式将铁电材料在下电极上沉积一层厚度为9~11nm的薄膜,作为电容的电介质。

35、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述上电极种子层采用磁控溅射的方式在高介电材料层上沉积一层10nm的钛金属和100nm的铜金属作为种子层。

36、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:通过电化学镀的方式于上电极种子层镀上一层厚铜并完全填充立体电容孔,厚度为2000nm。

37、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述上电极利用化学机械研磨的方式将晶圆表面的上电极、下电极、高介电材料层和阻隔层磨除,停留至氮化硅。

38、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述介质层利用黄光工艺于晶圆表面涂布光刻胶将掩膜版的图案转移至晶圆表面光刻胶并通过干刻将开孔处的二氧化硅去除,露出驱动线。

39、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述板线利用磁控溅射的方式于晶圆表面沉积厚度为2000nm~2300nm的金属。

40、作为本发明所述2.5d铁电电容制备方法的一种优选方案,其中:所述板线沉积的金属为钛和铝,叠层为钛150nm、铝2000nm和钛150nm的金属层;

41、所述板线采用黄光工艺在晶圆表面涂布光刻胶,将掩膜版的图案转移至晶圆表面的光刻胶,并利用刻蚀将不需要区域的金属移除,并联存储阵列内的电容,实现板线与驱动线连接。

42、本发明2.5d铁电电容制备方法的有益效果:通过优化工艺流程,以cmp化学机械研磨工艺,取代现有电容下电极,高介电材料介质以及上电极制程中的无掩膜干刻工艺,避免了无掩膜工艺干刻对电容各膜层可能造成的影响,使电容特性更加稳定。

- 还没有人留言评论。精彩留言会获得点赞!