屏蔽栅功率器件及其制造方法与流程

本发明涉及半导体集成电路制造领域,特别是涉及一种屏蔽栅(sgt)功率器件;本发明还涉及一种屏蔽栅功率器件的制造方法。

背景技术:

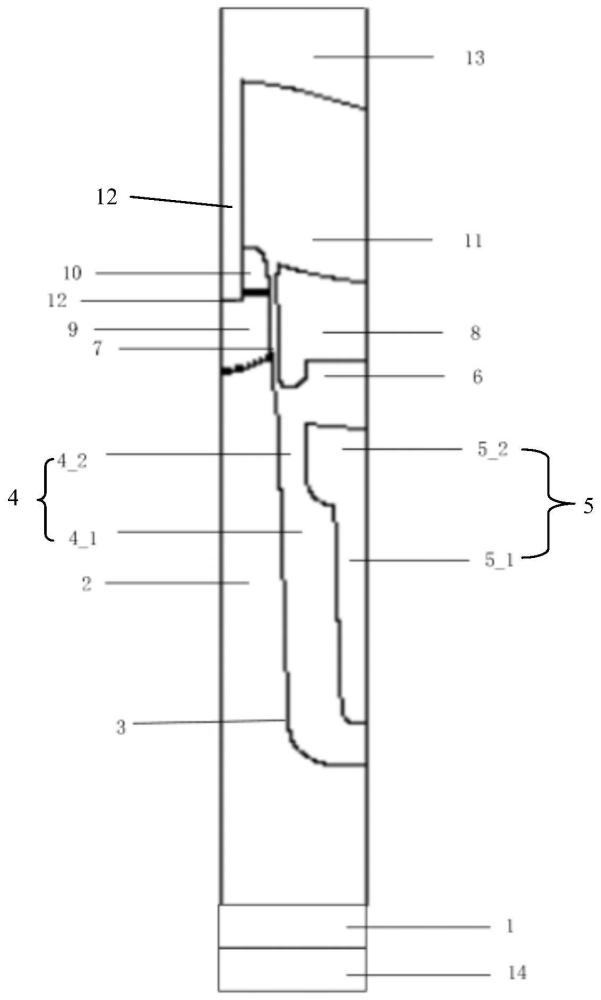

1、如图1所示,是现有屏蔽栅功率器件的结构示意图;以n型屏蔽栅功率mosfet为例,现有屏蔽栅功率器件的导通区由多个原胞周期性排列组成,各所述原胞的栅极结构包括:

2、沟槽103,形成于具有n型掺杂的第一外延层102中,所述第一外延层102形成于半导体衬底101表面。

3、图1中,显示了半个所述原胞的剖面结构,在图1的剖面上,另一半所述原胞的剖面结构沿沟槽103的中心位置左右对称。一个所述原胞的范围包括所述沟槽103以及所述沟槽103之间的间隔区。

4、屏蔽栅氧化膜104,形成于所述沟槽103的底部表面和底部区域的侧面上,在所述沟槽103的侧面上。

5、屏蔽栅多晶硅层105,形成于所述沟槽103中且将所述屏蔽栅氧化膜104所围区域完全填充。

6、栅介质膜107,形成于所述屏蔽栅氧化膜104顶部的所述沟槽103侧面上。

7、栅极多晶硅层108,形成于所述沟槽103的顶部区域,所述栅极多晶硅层108和所述沟槽103之间间隔有所述栅介质膜107;在所述栅极多晶硅层108和所述屏蔽栅多晶硅层105之间间隔有栅间介质膜106。

8、还包括:

9、沟道区,由形成于所述第一外延层102中的p型掺杂的第一阱区109组成,在纵向上,所述栅介质膜107穿过所述第一阱区109,被所述栅极多晶硅层108侧面覆盖的所述沟道区的表面用于形成沟道。

10、所述沟道区底部的所述第一外延层102组成漂移区。

11、n型重掺杂的源区110,形成于所述沟道区的表面且所述沟槽103的侧面自对准。

12、在所述源区110顶部形成有穿过所述源区110的接触孔112。

13、正面电极通过对所述正面金属层13进行图形化形成,包括源极和栅极。所述源极位于所述源区110的顶部并和所述源区110和所述第一阱区109相连,所述屏蔽栅多晶硅层105也连接到所述源极。所述栅极多晶硅层108和所述栅极相连。

14、n型重掺杂的漏区,形成于所述漂移区背面;所述半导体衬底101具有n型重掺杂,所述漏区由背面减薄后的所述半导体衬底101组成。或者,所述漏区由形成于背面减薄后的所述半导体衬底101中的n型重掺杂的背面离子注入区组成。

15、在所述漏区的背面形成有背面金属层114,由背面金属层114组成漏极。

16、屏蔽栅功率mosfet,其导通电阻由五部分组成,分别为有源区电阻,导电沟道电阻,栅极电极积累区电阻,漂移区电阻和衬底电阻。随着器件的击穿电压逐渐增大,漂移区电阻逐渐增加,其对导通功耗的影响越来越明显,为了降低导通功耗,不得不降低漂移区电阻,即增加第一导电类型半导体漂移区掺杂浓度,导致主结即沟道区和漂移区也即第一阱区109和底部的第一外延层102形成的pn结处的电场峰值逐渐增加,最终使得击穿位置转移到主结处。主结处的最高的电场峰值会带来一定的可靠性问题,因为主结处的高电场峰值会产生大量的电子空穴对,空穴在高电场的趋动下会隧穿到栅介质膜中,导致电参数发生漂移,严重会导致可靠性失效。

技术实现思路

1、本发明所要解决的技术问题是提供一种屏蔽栅功率器件,能改善屏蔽栅导电材料层所覆盖区域的电场分布,并降低器件主结的最高电场峰值,从而能提高器件的可靠性,并有利于提升漂移区的掺杂浓度并从而降低器件的导通功耗,还不需要增加额外的掩模版,工艺成本低。为此,本发明还提供一种屏蔽栅功率器件的制造方法。

2、为解决上述技术问题,本发明提供的屏蔽栅功率器件的导通区由多个原胞周期性排列组成,各所述原胞的栅极结构包括:

3、沟槽,形成于具有第一导电类型掺杂的第一外延层中,所述第一外延层形成于半导体衬底表面。

4、屏蔽栅介质膜,形成于所述沟槽的底部表面和底部区域的侧面上,在所述沟槽的侧面上,所述屏蔽栅介质膜具有阶梯结构且所述阶梯结构具有两个以上的介质膜段,从所述沟槽的底部到顶部方向上,各所述介质膜段的厚度依次减小。

5、屏蔽栅导电材料层,形成于所述沟槽中且将所述屏蔽栅介质膜所围区域完全填充,所述屏蔽栅导电材料层至少具有互相叠加的多个导电材料段,所述导电材料段的数量和所述介质膜段的数量相同。

6、各相邻的所述介质膜段中,令位于底部的为第一介质膜段以及位于顶部的为第二介质膜段,填充于所述第一介质膜段所围区域中的所述导电材料段为所述第一导电材料段,填充于所述第二介质膜段所围区域中的所述导电材料段为所述第二导电材料段。

7、所述第二介质膜段的厚度小于所述第一介质膜段的厚度。

8、所述第二介质膜段和所述第一介质膜段都由第一介质膜层组成,位于所述第二介质膜段的形成区域的所述第一介质膜层的厚度从所述第一介质膜段的厚度减薄到所述第二介质膜段的厚度并从而形成所述第二介质膜段;所述第一介质膜段的顶部表面由所述第一导电材料段自对准定义,所述第二介质膜段的减薄区域由所述第一导电材料段自对准定义。

9、栅介质膜,形成于所述屏蔽栅介质膜顶部的所述沟槽侧面上。

10、栅极导电材料层,形成于所述沟槽的顶部区域,所述栅极导电材料层和所述沟槽之间间隔有所述栅介质膜;在所述栅极导电材料层和所述屏蔽栅导电材料层之间间隔有栅间介质膜。

11、进一步的改进是,所述屏蔽栅功率器件还包括:

12、沟道区,由形成于所述第一外延层中的第二导电类型掺杂的第一阱区组成,在纵向上,所述栅介质膜穿过所述第一阱区,被所述栅极导电材料层侧面覆盖的所述沟道区的表面用于形成沟道。

13、所述沟道区底部的所述第一外延层组成漂移区。

14、第一导电类型重掺杂的源区,形成于所述沟道区的表面且所述沟槽的侧面自对准。

15、第一导电类型重掺杂的漏区,形成于所述漂移区背面;所述半导体衬底具有第一导电类型重掺杂,所述漏区由背面减薄后的所述半导体衬底组成;或者,所述漏区由形成于背面减薄后的所述半导体衬底中的第一导电类型重掺杂的背面离子注入区组成。

16、进一步的改进是,所述第一介质膜层的材料采用氧化膜,所述第一介质膜层的初始厚度为最底部的所述介质膜段的厚度。

17、进一步的改进是,所述第一介质膜层由热氧化膜和化学气相淀积的氧化膜叠加形成。

18、进一步的改进是,所述漂移区分成多个漂移区子层;

19、所述漂移区子层的数量和所述介质膜段的数量相同,各所述漂移区子层分别被一个所述介质膜段侧面覆盖,从而底部到顶部方向上,各所述漂移区子层的掺杂浓度逐渐增加。

20、进一步的改进是,所述屏蔽栅导电材料层的材料包括第一导电类型重掺杂的多晶硅。

21、所述栅极导电材料层的材料包括第一导电类型重掺杂的多晶硅。

22、进一步的改进是,在俯视面上,所述原胞的形状包括:条形、方形、六角形或圆形。

23、进一步的改进是,屏蔽栅功率器件为n型器件,第一导电类型为n型,第二导电类型为p型;或者,屏蔽栅功率器件为p型器件,第一导电类型为p型,第二导电类型为n型。

24、为解决上述技术问题,本发明提供的屏蔽栅功率器件的制造方法中,屏蔽栅功率器件的导通区由多个原胞周期性排列组成,各所述原胞的栅极结构的形成步骤包括

25、步骤一、提高表面形成有第一导电类型掺杂的第一外延层的半导体衬底,在所述第一外延层中形成沟槽。

26、步骤二、形成屏蔽栅介质膜和屏蔽栅导电材料层。

27、所述屏蔽栅介质膜形成于所述沟槽的底部表面和底部区域的侧面上,在所述沟槽的侧面上,所述屏蔽栅介质膜具有阶梯结构且所述阶梯结构具有两个以上的介质膜段,从所述沟槽的底部到顶部方向上,各所述介质膜段的厚度依次减小。

28、所述屏蔽栅导电材料层,形成于所述沟槽中且将所述屏蔽栅介质膜所围区域完全填充,所述屏蔽栅导电材料层至少具有互相叠加的多个导电材料段,所述导电材料段的数量和所述介质膜段的数量相同。

29、各相邻的所述介质膜段中,令位于底部的为第一介质膜段以及位于顶部的为第二介质膜段,填充于所述第一介质膜段所围区域中的所述导电材料段为第一导电材料段,填充于所述第二介质膜段所围区域中的所述导电材料段为第二导电材料段。

30、各相邻的所述介质膜段的形成工艺包括如下分步骤:

31、步骤21、提供厚度等于所述第一介质膜段的厚度的第一介质膜层,所述第一介质膜层位于所述沟槽的侧面。

32、步骤22、在所述第一介质膜层所围区域的所述沟槽中进行第一次填充形成所述第一导电材料段。

33、步骤23、进行回刻将所述第一导电材料段的顶部表面降低到定义所述第一介质膜段的顶部表面的位置处。

34、步骤24、以所述第一导电材料段为自对准掩膜对所述第一介质膜层进行刻蚀,被刻蚀的所述第一介质膜的厚度减薄到所述第二介质膜段的厚度,由未被刻蚀的所述第一介质膜层组成所述第一介质膜段,所述第一介质膜段的顶部表面由所述第一导电材料段的顶部表面自对准定义。

35、步骤25、在所述第一介质膜层所围区域的所述沟槽中进行第二次填充形成所述第二导电材料段。

36、步骤26、进行回刻将所述第二导电材料段的顶部表面降低到定义所述第二介质膜段的顶部表面的位置处。

37、步骤三、形成栅间介质膜、栅介质膜和栅极导电材料层。

38、所述栅介质膜形成于所述屏蔽栅介质膜顶部的所述沟槽侧面上。

39、所述形成于所述沟槽的顶部区域,所述栅极导电材料层和所述沟槽之间间隔有所述栅介质膜;在所述栅极导电材料层和所述屏蔽栅导电材料层之间间隔有所述栅间介质膜。

40、进一步的改进是,还包括如下步骤:

41、步骤四、在所述第一外延层中形成第二导电类型掺杂的第一阱区,沟道区由所述第一阱区组成,在纵向上,所述栅介质膜穿过所述第一阱区,被所述栅极导电材料层侧面覆盖的所述沟道区的表面用于形成沟道。

42、所述沟道区底部的所述第一外延层组成漂移区。

43、步骤五、形成第一导电类型重掺杂的源区,形成于所述沟道区的表面且所述沟槽的侧面自对准。

44、完成正面工艺后,还包括:

45、步骤六、对所述半导体衬底进行背面减薄,在所述漂移区背面形成第一导电类型重掺杂的漏区。

46、所述半导体衬底具有第一导电类型重掺杂,所述漏区直接由背面减薄后的所述半导体衬底组成;或者,所述漏区由形成于背面减薄后的所述半导体衬底中的第一导电类型重掺杂的背面离子注入区组成。

47、进一步的改进是,所述第一介质膜层的材料采用氧化膜;所述第一介质膜层的初始厚度为最底部的所述介质膜段的厚度。

48、进一步的改进是,所述第一介质膜层由热氧化膜和化学气相淀积的氧化膜叠加形成。

49、进一步的改进是,所述漂移区分成多个漂移区子层;

50、所述漂移区子层的数量和所述介质膜段的数量相同,各所述漂移区子层分别被一个所述介质膜段侧面覆盖,从而底部到顶部方向上,各所述漂移区子层的掺杂浓度逐渐增加。

51、进一步的改进是,所述屏蔽栅导电材料层的材料包括第一导电类型重掺杂的多晶硅。

52、所述栅极导电材料层的材料包括第一导电类型重掺杂的多晶硅。

53、进一步的改进是,屏蔽栅功率器件为n型器件,第一导电类型为n型,第二导电类型为p型;或者,屏蔽栅功率器件为p型器件,第一导电类型为p型,第二导电类型为n型。

54、本发明将屏蔽栅介质膜设置为阶梯结构,且从底部到顶部方向上各介质膜段的厚度依次递减,这样,从底部到顶部方向上屏蔽栅导电材料层对侧面覆盖区域如漂移区的耦合能力也会依次增加,在器件反偏时,顶部区域的屏蔽栅导电材料层对侧面所覆盖区域的耗尽能力会增加,更多的电力线会终止到屏蔽栅导电材料层上,从而能调节顶部区域电场分布,减小由于主结产生的电力线的集中,降低主结处的电场峰值,使屏蔽栅导电材料层的侧面所覆盖区域的电场强度均匀化,能防止漂移区的掺杂浓度所带来的主结处的高电场峰值,从而能提高器件的可靠性,有利于提升漂移区的掺杂浓度并从而降低器件的导通功耗,。

55、另外,本发明的屏蔽栅介质膜的阶梯结构通过将屏蔽栅导电材料层分成多个导电材料段逐级自对准定义,而导电材料段的顶部表面本身通过回刻即可定义,故本发明的屏蔽栅介质膜的阶梯结构不需要增加额外的掩模版,工艺成本低。

- 还没有人留言评论。精彩留言会获得点赞!