一种提升场效应晶体管表面势的结构及制备方法

本发明属于微电子,具体涉及一种提升场效应晶体管的表面势的结构及制备方法。

背景技术:

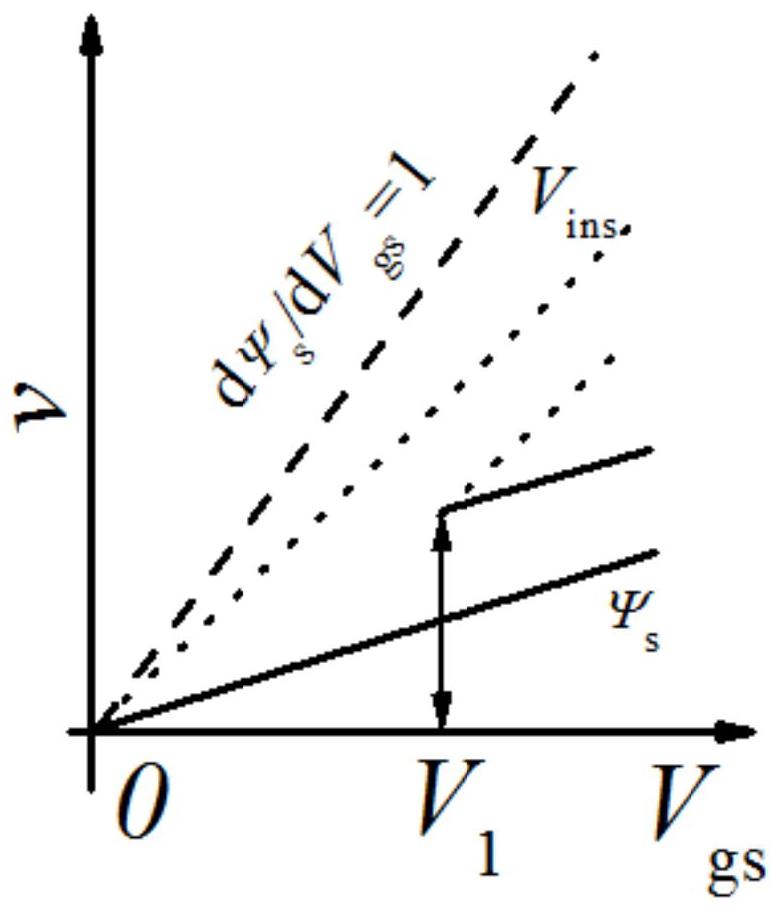

1、场效应晶体管(field-effect transistor,以下简称晶体管)是现代电子工业的基本单元和核心元件,其工作原理是:通过改变栅极电压vgs(电场)调控沟道的导通与否。沟道开启时,在源漏电压vds驱动下载流子定向运动产生源漏电流ids。应用范围主要包括开关器件、信号调制和放大等。晶体管作为开关器件时的电性能参数主要有亚阈值电压摆幅(subthreshold swing,ss)、阈值电压(vth)、ioff电流,以及开关态电流比、迁移率等,可通过电性能表征实验测量晶体管的转移ids-vgs和输出曲线ids-vds得到。其中,ss的定义为电流每增加一个数量级所需的最小电压,ss=dvgs/dlogids=(dvgs/dψs)(dψs/dlogids),单位是mv/decade,表征器件的开关速度,其中ψs是半导体上的压降,即表面势。同时ss值还影响晶体管的可实现的最小电压值,即影响器件的能耗和小型化,需要尽可能小的值。对于放大电路,本征增益ai是一个重要参数,它表征对信号的调制能力,由跨导gm和输出电阻ro的乘积决定,其中跨导定义为gm=dids/dvgs=(dids/dψs)(dψs/dvgs),输出电阻定义为ro=dvds/dids。以上可知,ss和ai受栅压直接调控。

2、随着晶体管物理尺寸的持续降低,需要更小的工作电压来应对性能、散热能力和能耗等方面的挑战。此外,低栅压时晶体管临近关态,电流小,输出电阻大,有利于提高本征增益。然而,受到器件工作机制和材料物理性质的约束,在低栅压时保持高性能面临诸多困难。

3、工作机制方面,晶体管中绝缘体层-半导体层组成串联电容器,对沟道的调节也是通过串联电容调控,即场效应。在传统认知中,绝缘体层主要起到阻挡电荷传输的作用,且电容基本为常数,这导致必定有一部分电压被绝缘体层分走,即栅压不能全部用于沟道的调控并使得dvgs/dψs>1。材料物理性质方面,晶体管中组成源流电流的电荷主要来自电极,即源电极。然而金属中电子的boltzmann分布给dψs/dlogids设置了一个极限,室温时为60mv/decade。两者共同作用导致室温时ss不能小于60mv/decade。由跨导gm的表达式可知栅压分配方式同时也限制了ai的提升。

4、现有的机制中,改变电子源虽然可以实现ss<60mv/decade(k.gopalakrishnan,p.b.griffin,j.d.plummer,impact ionization mos(i-mos)-part i:device andcircuit simulations.ieee trans.electron dev.52,69-76,2005)或者较大的增益(s.s.lee and a.nathan,subthreshold schottky-barrier thin-film transistorswith ultralow power and high intrinsic gain.science 354,302-304,2016),但是对降低栅压没有作用;采用铁电体做绝缘体,理论上可以实现对沟道的直接调控,但是需要铁电极化(铁电畴)反转的参与,既需要额外的能量源,又引入了电压匹配问题。

5、通过对晶体管工作机制及影响ss和ai性能的因素分析可知,默认绝缘体主要起到阻挡电荷传输的作用且电容基本为常数禁止了晶体管性能的提升。2015年有研究报道在金属-绝缘体-半导体-金属(metal-insulator-semiconductor-metal,mism)结构中绝缘体层可以充当电荷输运的作用(e.k.lee,j.lee,j.h.kim,k.h.lim,j.s.byun,j.ko,y.d.kim,y.park,y.s.kim,direct electron injection into an oxide insulator using acathode buffer layer.nat.commun.6,6785,2015)。而在金属-绝缘体-金属(metal-insulator-metal,mim)结构中,绝缘体仍充当电荷阻挡任务。但受限于电荷传输机制的限制,无法在单个mim或mism器件中实现绝缘体层阻挡-输运电荷的可逆转变,也无法提升晶体管的性能。

技术实现思路

1、本发明的目的在于,针对上述问题,本发明提出一种允许绝缘体层发生阻挡-输运电荷的可逆转变的结构,并用于提升晶体管表面势,以实现低栅压vgs下提升亚阈值电压摆幅(ss)和本征增益(ai)性能。本发明的另一个目的是提供上述结构的制备方法。

2、本发明的结构采用的技术方案为:

3、一种提升场效应晶体管表面势的结构,包括绝缘体层、半导体层、栅电极、漏电极和源电极,绝缘体层设置在栅电极和半导体层之间以隔绝栅电极和半导体层,源电极、漏电极和半导体层接触;所述源电极同时与所述半导体层和绝缘体层接触,使源电极、绝缘体层、栅电极构成的mim部分和源电极、绝缘体层、半导体层、栅电极构成的mism部分形成并联电路。

4、进一步地,所述场效应晶体管为底栅交错型、底栅共平面型、顶栅交错型或顶栅共平面型。

5、进一步地,所述栅电极采用重掺p-si作为栅电极。

6、进一步地,所述绝缘体层的厚度为2-200nm。

7、进一步地,所述源电极和漏电极厚度为2-300nm。

8、进一步地,所述源电极和漏电极的面积为10nm2-1000μm2。

9、进一步地,所述源电极与所述半导体层和绝缘体层接触的覆盖面积为2nm2-900μm2。

10、本发明还提供一种提升场效应晶体管表面势的结构的制备方法,该方法包括如下步骤:

11、步骤1,在栅电极上生长一层绝缘体层,并进行清洗处理;

12、步骤2,在所述绝缘体层上方生长一层半导体层,然后在大气环境中进行热退火处理;

13、步骤3,在经步骤2热退火处理后的结构表面沉积金属膜,作为源电极和漏电极,所述源电极同时与所述半导体层和绝缘体层接触,使源电极、绝缘体层、栅电极构成的mim部分和源电极、绝缘体层、半导体层、栅电极构成的mism部分形成并联电路。

14、进一步地,所述步骤2中,热退火处理的温度为200-600℃。

15、进一步地,所述步骤2中,热退火处理的时间为0.5至3小时。

16、目前的现有技术中对晶体管的ss值和本征增益的调控主要通过改变电子源,这导致两个结果:1)小的ss值或大的ai不一定能在小的栅压时获得,2)小的ss值和大的ai不能同时在同一栅压下实现。本发明通过将mim部分和mism部分集成为并联结构,允许绝缘体层发生阻挡-输运电荷的可逆转变,可提升晶体管表面势,实现低栅压vgs下提升亚阈值电压摆幅(ss)和本征增益(ai)性能。本发明实施例优选在0.3v的小栅压下同时实现了亚阈值电压摆幅突破boltzmann极限,即达到36mv/decade,和本征增益达到10000以上。

- 还没有人留言评论。精彩留言会获得点赞!