半导体集成电路及其制备方法与流程

本发明涉及半导体,特别涉及一种半导体集成电路及其制备方法。

背景技术:

1、bcd(bipolar cmosdmos)器件中集成有双极型晶体管bipolar、cmos器件与dmos器件,它综合了双极型晶体管bipolar其高跨导、强负载驱动能力、cmos器件的集成度高、低功耗的特点,以及dmos器件的高压大电流驱动等优点,并且bcd器件具有低成本、易封装、易设计和外围芯片更简洁等特点,从而被快速发展并广泛应用于各个领域中。以及,功率晶体管器件由于其具有较低的导通电阻和较快的切换速度,从而可被应用于模拟电路中。

2、随着半导体技术的发展,产品趋于小型化的需求不断增长,为此希望可以在不影响各自器件的性能的基础上,实现功率晶体管器件和bcd器件集成在同一芯片上。

技术实现思路

1、本发明的目的在于提供一种半导体集成电路的制备方法,用于实现功率晶体管器件和bcd器件可集成在同一芯片上,并且还借助bcd器件的工艺优化功率晶体管器件的性能。

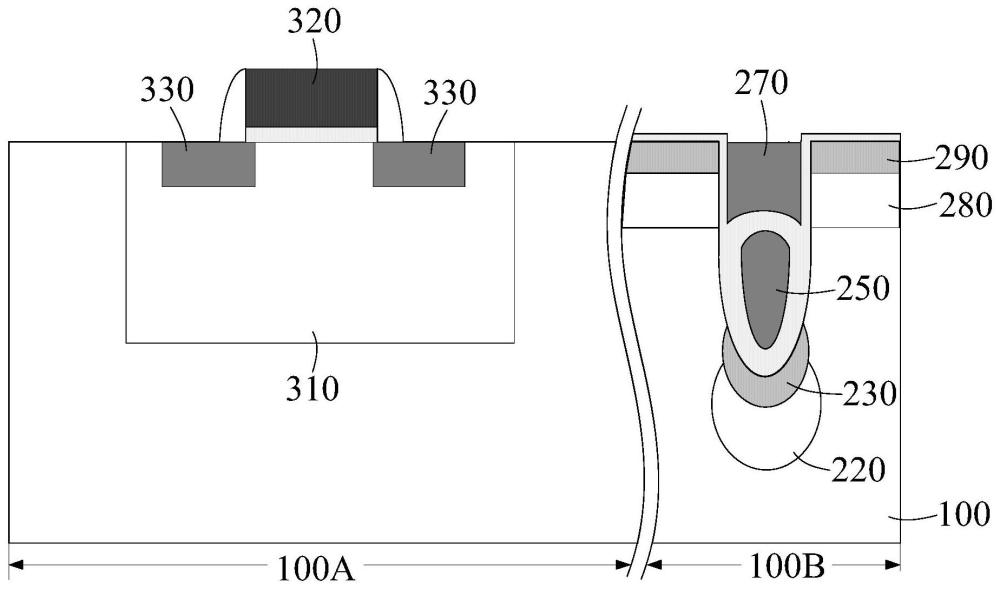

2、本发明提供的一种半导体集成电路的制备方法,包括:提供衬底,所述衬底具有bcd器件区和功率器件区,并在所述功率器件区的衬底内形成有栅极沟槽;执行第一离子注入工艺,以在所述bcd器件区的衬底内形成第一掺杂区,同时在所述栅极沟槽的下方形成第二掺杂区,其中所述功率器件区的衬底区域具有第一导电类型,所述第一掺杂区和所述第二掺杂区具有第二导电类型;以及,在所述栅极沟槽内形成功率晶体管器件的栅电极,在所述bcd器件区的衬底上形成bcd器件。

3、可选的,所述第二掺杂区间隔设置在所述栅极沟槽的下方。

4、可选的,所述第二掺杂区从所述栅极沟槽的沟槽底部向下扩展;以及,在形成所述第二掺杂区之后,还包括:执行第二离子注入工艺,以在以在所述栅极沟槽的下方形成第一导电类型的第三掺杂区,所述第三掺杂区从所述栅极沟槽的沟槽底部向下扩展,并且所述第三掺杂区向下扩展的深度位置高于所述第二掺杂区向下扩展的深度位置,以使所述第二掺杂区靠近沟槽底部的部分替代为所述第三掺杂区。

5、可选的,所述第三掺杂区的宽度至少大于所述栅极沟槽的沟槽底部的宽度尺寸,以使所述第三掺杂区包围所述栅极沟槽的沟槽底部。

6、可选的,所述第一掺杂区用作所述bcd器件区内的dmos管或者cmos管的阱区。

7、可选的,所述功率晶体管器件包括屏蔽栅场效应晶体管。

8、本发明还提供了一种半导体集成电路,包括:衬底,所述衬底具有bcd器件区和功率器件区;功率晶体管器件,形成在所述衬底的功率器件区内,所述功率器件区的衬底区域具有第一导电类型,以及在所述功率器件区的衬底内形成有栅极沟槽,所述功率晶体管器件的栅电极形成在所述栅极沟槽内,并且在所述栅极沟槽的下方形成有第二导电类型的第二掺杂区;以及,bcd器件,形成在所述衬底的bcd器件区,并在所述bcd器件区的衬底内形成有第二导电类型的第一掺杂区。

9、可选的,所述第二掺杂区间隔设置在所述栅极沟槽的下方。

10、可选的,在所述栅极沟槽的下方还形成有第一导电类型的第三掺杂区,所述第三掺杂区从所述栅极沟槽的沟槽底部向下扩展,并且所述第三掺杂区向下扩展的深度位置高于所述第二掺杂区向下扩展的深度位置,以使所述第二掺杂区和所述栅极沟槽之间间隔有所述第三掺杂区。

11、可选的,所述第三掺杂区的宽度至少大于所述栅极沟槽的沟槽底部的宽度尺寸,以使所述第三掺杂区包围所述栅极沟槽的沟槽底部。

12、可选的,所述第一掺杂区用作所述bcd器件区内的dmos管或者cmos管的阱区。

13、可选的,所述功率晶体管器件包括屏蔽栅场效应晶体管。

14、本发明提供的半导体集成电路的制备方法中,在执行第一离子注入工艺以在bcd器件区内形成第一掺杂区的同时,还借助该第一离子注入工艺在栅极沟槽的下方形成第二掺杂区,通过在栅极沟槽的下方设置第二掺杂区以实现对衬底内的电场调制作用,使得电场可向衬底的更深位置中扩展,有效提高了功率晶体管器件的击穿电压。或者说,可以在维持功率晶体管器件的耐压性能的基础上,降低栅极沟槽的深度,从而可避免由于沟槽的深度过大而导致基片容易发生形变的问题。

技术特征:

1.一种半导体集成电路的制备方法,其特征在于,包括:

2.如权利要求1所述的半导体集成电路的制备方法,其特征在于,所述第二掺杂区间隔设置在所述栅极沟槽的下方。

3.如权利要求2所述的半导体集成电路的制备方法,其特征在于,所述第二掺杂区从所述栅极沟槽的沟槽底部向下扩展;以及,在形成所述第二掺杂区之后,还包括:

4.如权利要求3所述的半导体集成电路的制备方法,其特征在于,所述第三掺杂区的宽度至少大于所述栅极沟槽的沟槽底部的宽度尺寸,以使所述第三掺杂区包围所述栅极沟槽的沟槽底部。

5.如权利要求1所述的半导体集成电路的制备方法,其特征在于,所述第一掺杂区用作所述bcd器件区内的dmos管或者cmos管的阱区。

6.如权利要求1所述的半导体集成电路的制备方法,其特征在于,所述功率晶体管器件包括屏蔽栅场效应晶体管。

7.一种半导体集成电路,其特征在于,包括:

8.如权利要求7所述的半导体集成电路,其特征在于,所述第二掺杂区间隔设置在所述栅极沟槽的下方。

9.如权利要求8所述的半导体集成电路,其特征在于,在所述栅极沟槽的下方还形成有第一导电类型的第三掺杂区,所述第三掺杂区从所述栅极沟槽的沟槽底部向下扩展,并且所述第三掺杂区向下扩展的深度位置高于所述第二掺杂区向下扩展的深度位置,以使所述第二掺杂区和所述栅极沟槽之间间隔有所述第三掺杂区。

10.如权利要求9所述的半导体集成电路,其特征在于,所述第三掺杂区的宽度至少大于所述栅极沟槽的沟槽底部的宽度尺寸,以使所述第三掺杂区包围所述栅极沟槽的沟槽底部。

11.如权利要求7所述的半导体集成电路,其特征在于,所述第一掺杂区用作所述bcd器件区内的dmos管或者cmos管的阱区。

12.如权利要求7所述的半导体集成电路,其特征在于,所述功率晶体管器件包括屏蔽栅场效应晶体管。

技术总结

本发明提供了一种半导体集成电路及其制备方法。该制备方法中,通过执行第一离子注入工艺以在BCD器件区内形成第一掺杂区,同时还利用该第一离子注入工艺在栅极沟槽的下方形成第二掺杂区,通过在栅极沟槽的下方设置第二掺杂区以实现对衬底内的电场调制作用,使得电场可向衬底的更深位置中扩展,有效提高了功率晶体管器件的击穿电压。或者,可以在维持功率晶体管器件的耐压性能的基础上,降低栅极沟槽的深度,从而可避免由于沟槽的深度过大而导致基片容易发生形变的问题。

技术研发人员:黄艳,赵晓燕,钟鹏,石磊,陆凌杰

受保护的技术使用者:芯联集成电路制造股份有限公司

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!