一种多芯片并联的全桥封装结构和封装方法与流程

本发明涉及芯片封装,特别是一种多芯片并联的全桥封装结构和封装方法。

背景技术:

1、电力电子技术在航空航天、轨道交通、电动汽车以及电力系统等多个领域应用广泛,全电路因为其结构简单、可扩展性强,在工业领域被大范围使用。现有商用模块存在寄生电感较大、开关管不均流、通流能力不高问题。

技术实现思路

1、为解决上述问题,本发明提出一种多芯片并联的全桥封装结构,该全桥封装结构可提高模块的流通能力,降低主回路寄生电感。本发明还提出了封装方法。

2、为实现上述目的,本发明采用的技术方案是:

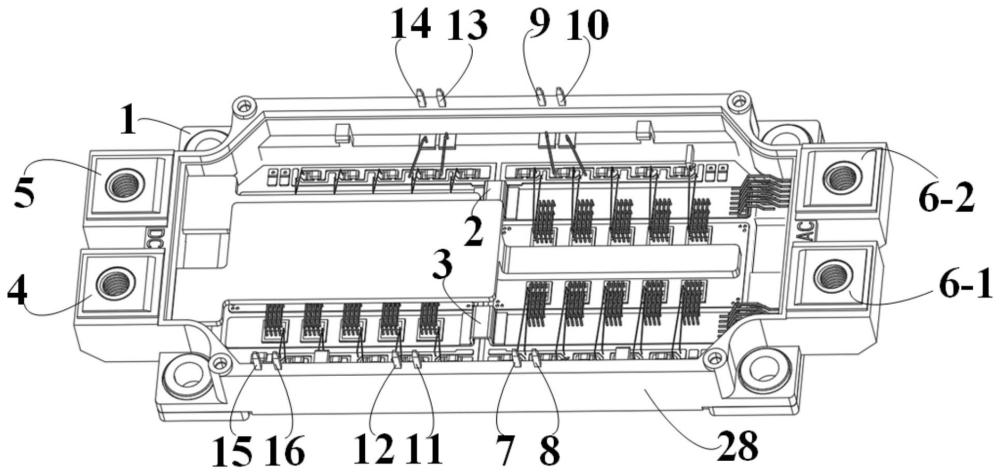

3、在第一个技术方案中,一种多芯片并联的全桥封装结构,包括dbc基板,dbc基板具有电路层,所述电路层包括a区铜箔和b区铜箔,a区铜箔包括负极dc-铜箔、以及位于负极dc-铜箔两侧的下桥的交流ac铜箔,所述b区铜箔包括正极dc+铜箔、以及位于正极dc+铜箔两侧的上桥的交流ac铜箔,且所述a区铜箔和b区铜箔对称设置,所述下桥的交流ac铜箔和上桥的交流ac铜箔分别通过铜块连接;

4、下桥第一部分的n颗芯片焊接在一个下桥的交流ac铜箔上,下桥第二部分的n颗芯片焊接在另一个下桥的交流ac铜箔上;上桥第一部分的n颗芯片焊接在正极dc+铜箔上并靠近一个上桥的交流ac铜箔,上桥第二部分的n颗芯片焊接在正极dc+铜箔上并靠近另一个上桥的交流ac铜箔上,且n为大于2的正整数;

5、下桥第一部分的n颗芯片并联、下桥第二部分的n颗芯片并联、上桥第一部分的n颗芯片并联、上桥第二部分的n颗芯片并联,且下桥第一部分的n颗芯片组、下桥第二部分的n颗芯片组、上桥第一部分的n颗芯片组和上桥第二部分的n颗芯片组串联形成全桥封装。

6、在第一个技术方案中,作为优选的,所述下桥第一部分的n颗芯片组、下桥第二部分的n颗芯片组、上桥第一部分的n颗芯片组和上桥第二部分的n颗芯片组均为直线排列的芯片。

7、在第一个技术方案中,作为优选的,所述下桥第一部分的n颗芯片组和下桥第二部分的n颗芯片组镜像设置;上桥第一部分的n颗芯片组和上桥第二部分的n颗芯片组镜像设置。

8、在第一个技术方案中,作为优选的,所述负极dc-铜箔两侧的两个下桥的交流ac铜箔宽度相同,并以负极dc-铜箔的中心线对称。

9、在第一个技术方案中,作为优选的,所述正极dc+铜箔两侧的两个上桥的交流ac铜箔宽度相同,并以正极dc+铜箔的中心线对称。

10、在第一个技术方案中,作为优选的,所述dbc基板上还具有dc+接线端子和dc-接线端子,dc+接线端子通过超声焊接工艺与正极dc+铜箔进行电气连接;dc-接线端子通过超声焊接技术与负极dc-铜箔进行电气连接。

11、在第一个技术方案中,作为优选的,所述a区铜箔以及焊接在a区铜箔上的芯片构成下桥驱动回路,所述b区铜箔以及焊接在b区铜箔上的芯片构成上桥驱动回路;

12、所述上桥驱动回路上下对称且左右对称;

13、所述下桥驱动回路上下对称且左右对称。

14、在第一个技术方案中,作为优选的,所述dbc基板具有下层铜箔,所述下层铜箔距离边缘一定距离处也刻蚀了一圈小孔。

15、在第一个技术方案中,作为优选的,所述上层铜箔最外边沿距离陶瓷基板边缘设置为1mm,下层铜箔最外边沿距离陶瓷基板边缘设置为1mm。

16、在第一个技术方案中,一种封装方法,用于封装如在第一个技术方案中任一项所述的多芯片并联的全桥封装结构,包括如下步骤,

17、s1、根据拟封装的功率模块的结构制备相应的覆铜陶瓷基板,刻蚀所述覆铜陶瓷基板的正面金属层和底面金属层,之后进行表面镀镍处理;

18、s2、采用第一焊料将功率芯片焊接或烧结到所述覆铜陶瓷基板的对应铜箔位置上;

19、s3、将功率半导体芯片的表面电极与所述覆铜陶瓷基板的铜箔通过引线键合工艺进行电气连接;

20、s4、采用第二焊料将驱动电阻、热敏电阻焊接至绝缘基板的上表面金属层的对应位置上;

21、s5、将外壳固定在散热基板上,采用引线键合工艺将外壳中的驱动端子和交流ac端子与绝缘基板的相应金属层进行电连接,采用超声键合工艺将外壳中的直流正极dc+和直流负极dc-端子与基板进行电连接。

22、s6、将绝缘凝胶注入外壳中,抽真空,然后加热或室温静置使绝缘凝胶固化;安装盖板后获得封装好的功率模块。

23、使用本发明的有益效果是:

24、本多芯片并联的全桥封装结构由于在上桥和下桥均采用多芯片并联,可以提高模块的通流能力;dbc基板正面的铜箔分为两个区,并且结构对称,主回路寄生电感较小;正负极大铜排端子可提高电流到芯片的电流强度;加工方法可靠、封装结构可实现、成本低、可靠性高。

技术特征:

1.一种多芯片并联的全桥封装结构,其特征在于:包括dbc基板,dbc基板具有电路层,所述电路层包括a区铜箔和b区铜箔,a区铜箔包括负极dc-铜箔、以及位于负极dc-铜箔两侧的下桥的交流ac铜箔,所述b区铜箔包括正极dc+铜箔、以及位于正极dc+铜箔两侧的上桥的交流ac铜箔,且所述a区铜箔和b区铜箔对称设置,所述下桥的交流ac铜箔和上桥的交流ac铜箔分别通过铜块连接;

2.根据权利要求1所述的多芯片并联的全桥封装结构,其特征在于:所述下桥第一部分的n颗芯片组、下桥第二部分的n颗芯片组、上桥第一部分的n颗芯片组和上桥第二部分的n颗芯片组均为直线排列的芯片。

3.根据权利要求1所述的多芯片并联的全桥封装结构,其特征在于:所述下桥第一部分的n颗芯片组和下桥第二部分的n颗芯片组镜像设置;上桥第一部分的n颗芯片组和上桥第二部分的n颗芯片组镜像设置。

4.根据权利要求1所述的多芯片并联的全桥封装结构,其特征在于:所述负极dc-铜箔两侧的两个下桥的交流ac铜箔宽度相同,并以负极dc-铜箔的中心线对称。

5.根据权利要求1所述的多芯片并联的全桥封装结构,其特征在于:所述正极dc+铜箔两侧的两个上桥的交流ac铜箔宽度相同,并以正极dc+铜箔的中心线对称。

6.根据权利要求1所述的多芯片并联的全桥封装结构,其特征在于:所述dbc基板上还具有dc+接线端子和dc-接线端子,dc+接线端子通过超声焊接工艺与正极dc+铜箔进行电气连接;dc-接线端子通过超声焊接技术与负极dc-铜箔进行电气连接。

7.根据权利要求1所述的多芯片并联的全桥封装结构,其特征在于:所述a区铜箔以及焊接在a区铜箔上的芯片构成下桥驱动回路,所述b区铜箔以及焊接在b区铜箔上的芯片构成上桥驱动回路;

8.根据权利要求1所述的多芯片并联的全桥封装结构,其特征在于:所述dbc基板具有下层铜箔,所述下层铜箔距离边缘一定距离处也刻蚀了一圈小孔。

9.根据权利要求8所述的多芯片并联的全桥封装结构,其特征在于:所述上层铜箔最外边沿距离陶瓷基板边缘设置为1mm,下层铜箔最外边沿距离陶瓷基板边缘设置为1mm。

10.一种封装方法,用于封装如权利要求1-9任一项所述的多芯片并联的全桥封装结构,其特征在于:包括如下步骤,

技术总结

本发明涉及芯片封装技术领域,具体公开了一种多芯片并联的全桥封装结构和封装方法。所述封装结构包括:散热底板、覆铜陶瓷基板、功率半导体芯片、键合线、驱动电阻、热敏电阻、正负极铜排、灌封胶、外壳及接线端子。散热底板上焊接覆铜陶瓷基板,所述DBC基板上焊接功率半导体芯片、热敏电阻、接线端子;功率半导体芯片表面电极通过键合线与DBC基板实现电气连接。本发明提供的封装结构通过合理的DBC基板布局优化,实现了紧凑、兼容多颗芯片并联、高可靠性、低杂散电感且均流的封装模块,驱动回路采用Kelvin结构,减小了共源寄生电感对驱动回路的负反馈影响,提高了开关速度。相应方法使得该封装结构得以实现,且成本低、加工质量可靠。

技术研发人员:毛锦进,黄志召,李宇雄,李杰,张建行

受保护的技术使用者:武汉羿变电气有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!