用多晶硅作源区的SGT-MOSFET结构及制备方法与流程

本发明涉及功率sgt-mosfet器件领域,尤其涉及一种用多晶硅作源区的sgt-mosfet结构及制备方法。

背景技术:

1、随着功率mos器件工艺和设计的不断发展,国内外功率mos器件的竞争也越来越激烈,降低器件的成本、提高器件的性能及可靠性也越来越迫切。现有的sgt-mosfet结构如图1所示,在外延层刻蚀形成沟槽,在沟槽里生长场氧化层,然后填充源极多晶硅,生长一层场氧,再在沟槽内填充栅极多晶硅,再体区上表面铺设源极,源极处于台面顶部,体区位于源极下面,源极和体区之间短接,接触孔打到外延层里面,其中沟槽底部的源极多晶硅通过版图布局最终是和正面金属层短接的。现有技术中源极是通过注入形成的,在缩小尺寸的过程中,就会出现如下问题:

2、1)接触孔到栅极的距离减少,接触孔对位余量不足,容易出现接触孔打偏,从而短接栅极和源极从而出现漏电;

3、2)接触孔尺寸减小,使得器件抗单脉冲雪崩击穿能量和抗浪涌能力变弱;

4、3)器件参数稳定性差,特别是阈值电压参数稳定性变差;这是因为接触孔到栅极的距离过小,导致接触孔注入影响到沟道浓度,从而导致阈值电压漂移。

5、因此,亟待解决上述问题。

技术实现思路

1、发明目的:本发明的第一目的是提供一种用多晶硅作源区的sgt-mosfet结构,本发明通过用多晶硅作源区来避免现有技术中的接触孔对位问题,进一步增大接触尺寸,改善单脉冲雪崩击穿能量和浪涌能力。

2、本发明的第二目的是提供一种用多晶硅作源区的sgt-mosfet结构的制备方法。

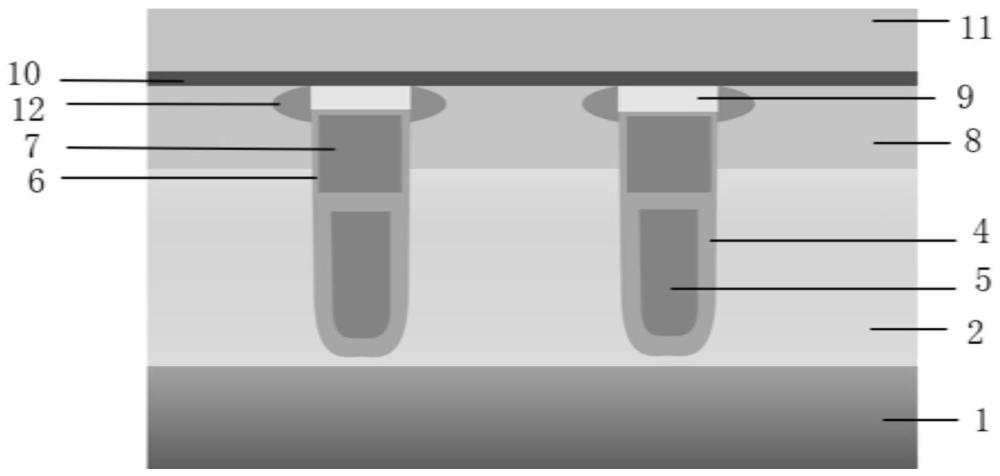

3、技术方案:为实现以上目的,本发明公开了一种用多晶硅作源区的sgt-mosfet结构,包括自下而上依次设置的衬底、外延层、外延层表面注入离子形成的体区以及接触层,所述体区和外延层内设置有沟槽,该沟槽内自下而上依次填充有作为场板的第一源极多晶硅、栅极多晶硅和作为源区的第二源极多晶硅,其中接触层与第二源极多晶硅和体区直接接触。

4、优选的,第一源极多晶硅的底部和两侧包覆有一层场氧化层,第一源极多晶硅的上表面包覆有一层隔离氧化层,栅极多晶硅的两侧包覆有一层栅氧,栅极多晶硅的上表面包覆有一层隔离氧化层。

5、其中,接触层上方淀积有正面金属层。

6、本发明一种用多晶硅作源区的sgt-mosfet结构的制备方法,包括如下步骤:

7、(1)生长外延层:根据mosfet的特性需求选择合适的外延圆片,该外延圆片由低范围电阻率的衬底和定值电阻率的外延层组成,在衬底上进行外延生长形成一外延层;

8、(2)沟槽刻蚀:在外延层上进行沟槽刻蚀形成沟槽,

9、(3)场氧化层生长:生长氧化层,在沟槽侧壁、底部和外延层表面生长出一层场氧化层;

10、(4)源极多晶硅淀积并回刻:在沟槽内淀积源极多晶硅,并对源极多晶硅进行回刻,至沟槽内剩余空间具有一定高度,形成作为场板的第一源极多晶硅;

11、(5)隔离氧化层淀积:对外延层表面和沟槽内淀积一层隔离氧化层;

12、(6)隔离氧化层回刻:回刻去掉外延层表面和沟槽内侧壁表面的隔离氧化层,在沟槽内源极多晶硅上表面形成一层隔离氧化层;

13、(7)栅氧生长:对外延层表面和沟槽内壁表面进行牺牲氧化,并去掉表面氧化层;在沟槽和外延层表面形成一层氧化层,即为栅氧;

14、(8)栅极多晶硅淀积并回刻:在沟槽内淀积栅极多晶硅,并对栅极多晶硅进行回刻,至沟槽内剩余空间具有一定高度;

15、(9)体区注入:对外延层进行离子的注入,形成体区;

16、(10)隔离氧化层淀积并回刻:对外延层表面和沟槽内淀积一层隔离氧化层,回刻去掉外延层表面和沟槽内侧壁表面的隔离氧化层,回刻至沟槽内栅极多晶硅上表面形成一层隔离氧化层;

17、(11)源极多晶硅淀积并回刻:在沟槽内淀积源极多晶硅,并对源极多晶硅进行回刻,至沟槽内源极多晶硅低于体区上表面,形成作为源区的第二源极多晶硅,即第二源极多晶硅杂质扩散形成源区;

18、(12)接触层和正面金属层淀积并回刻:在体区上表面淀积并回刻形成一层接触层(10),再在接触层上表面淀积并回刻形成一层正面金属层。

19、其中,所述步骤(1)中衬底可选用单晶硅、砷化镓gaas或碳化硅sic。

20、进一步,所述步骤(2)中沟槽深度为1~10μm,相邻沟槽之间间隔为0.3~4μm。

21、优选的,所述步骤(3)中场氧化层的厚度为500~15000a。

22、再者,所述步骤(6)中隔离氧化层的厚度为500~4500a。

23、进一步,所述步骤(7)中栅氧的厚度为200~1000a。

24、再者,所述步骤(10)中隔离氧化层厚度为250~600a。

25、有益效果:与现有技术相比,本发明具有以下显著优点:本发明的源区是通过重掺杂的第二源极多晶硅来充当,由于源区不是通过注入形成,使得体区直接处于外延层表面;这样就不用打接触孔到外延层里面;而是通过一大块的接触层直接连接沟槽表面的第二源极多晶硅和体区,第二源极多晶硅提供杂质扩散形成源区;这样即可以避免现有技术中的接触孔对位问题,又可以进一步增大接触尺寸,改善单脉冲雪崩击穿能量和浪涌能力。

技术特征:

1.一种用多晶硅作源区的sgt-mosfet结构,其特征在于:包括自下而上依次设置的衬底(1)、外延层(2)、外延层表面注入离子形成的体区(8)以及接触层(10),所述体区(8)和外延层(2)内设置有沟槽(3),该沟槽(3)内自下而上依次填充有作为场板的第一源极多晶硅(5)、栅极多晶硅(7)和杂质扩散形成源区(12)的第二源极多晶硅(9),其中接触层(10)与第二源极多晶硅(9)和体区(8)直接接触。

2.根据权利要求1所述的用多晶硅作源区的sgt-mosfet结构,其特征在于:所述第一源极多晶硅(5)的底部和两侧包覆有一层场氧化层(4),第一源极多晶硅(5)的上表面包覆有一层隔离氧化层,栅极多晶硅(7)的两侧包覆有一层栅氧(6),栅极多晶硅(7)的上表面包覆有一层隔离氧化层。

3.根据权利要求1所述的用多晶硅作源区的sgt-mosfet结构,其特征在于:所述接触层上方淀积有正面金属层(11)。

4.一种基于权利要求1至3任一所述的用多晶硅作源区的sgt-mosfet结构的制备方法,其特征在于,包括如下步骤:

5.根据权利要求4所述的用多晶硅作源区的sgt-mosfet结构的制备方法,其特征在于:所述步骤(1)中衬底(1)可选用单晶硅、砷化镓gaas或碳化硅sic。

6.根据权利要求4所述的用多晶硅作源区的sgt-mosfet结构的制备方法,其特征在于:所述步骤(2)中沟槽深度为1~10μm,相邻沟槽之间间隔为0.3~4μm。

7.根据权利要求4所述的用多晶硅作源区的sgt-mosfet结构的制备方法,其特征在于:所述步骤(3)中场氧化层(4)的厚度为500~15000a。

8.根据权利要求4所述的用多晶硅作源区的sgt-mosfet结构的制备方法,其特征在于:所述步骤(6)中隔离氧化层的厚度为500~4500a。

9.根据权利要求4所述的用多晶硅作源区的sgt-mosfet结构的制备方法,其特征在于:所述步骤(7)中栅氧(6)的厚度为200~1000a。

10.根据权利要求4所述的用多晶硅作源区的sgt-mosfet结构的制备方法,其特征在于:所述步骤(10)中隔离氧化层厚度为250~600a。

技术总结

本发明公开了一种用多晶硅作源区的SGT‑MOSFET结构及制备方法,包括自下而上依次设置的衬底、外延层、外延层表面注入离子形成的体区以及接触层,所述体区和外延层内设置有沟槽,该沟槽内自下而上依次填充有作为场板的第一源极多晶硅、栅极多晶硅和杂质扩散形成源区的第二源极多晶硅,其中接触层与第二源极多晶硅和体区直接接触。本发明通过用多晶硅作源区来避免现有技术中的接触孔对位问题,进一步增大接触尺寸,改善单脉冲雪崩击穿能量和浪涌能力。

技术研发人员:李承杰,代萌,周佛坤,陆彬彬

受保护的技术使用者:江苏格瑞宝电子有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!