二极管的制备方法与流程

本申请涉及半导体,特别是涉及一种二极管的制备方法。

背景技术:

1、当前,大功率高压肖特基势垒二极管逐渐向高可靠性方向发展,大功率高压肖特基势垒二极管的可靠性受到越来越多的客户重视,典型的可靠性指标有htrb(hightemperature reverse bias,高温反偏试验)、pct(positive temperature coefficient,正温度系数)、ifsm(maximum forward surge current,最大正向浪涌电流)、esd(electro-static discharge,静电放电)、ssg(反向浪涌电流)等,其中esd能力尤其受到高压大功率sbd(schottky barrier diode,肖特基二极管)客户的关注。

2、然而,尺寸越大,esd能力越强,像32mil及以下等小尺寸高电压产品esd能力仍旧面临挑战。

技术实现思路

1、本申请主要解决的技术问题是提供一种二极管的制备方法,解决现有技术中小尺寸二极管的esd能力提升困难的问题。

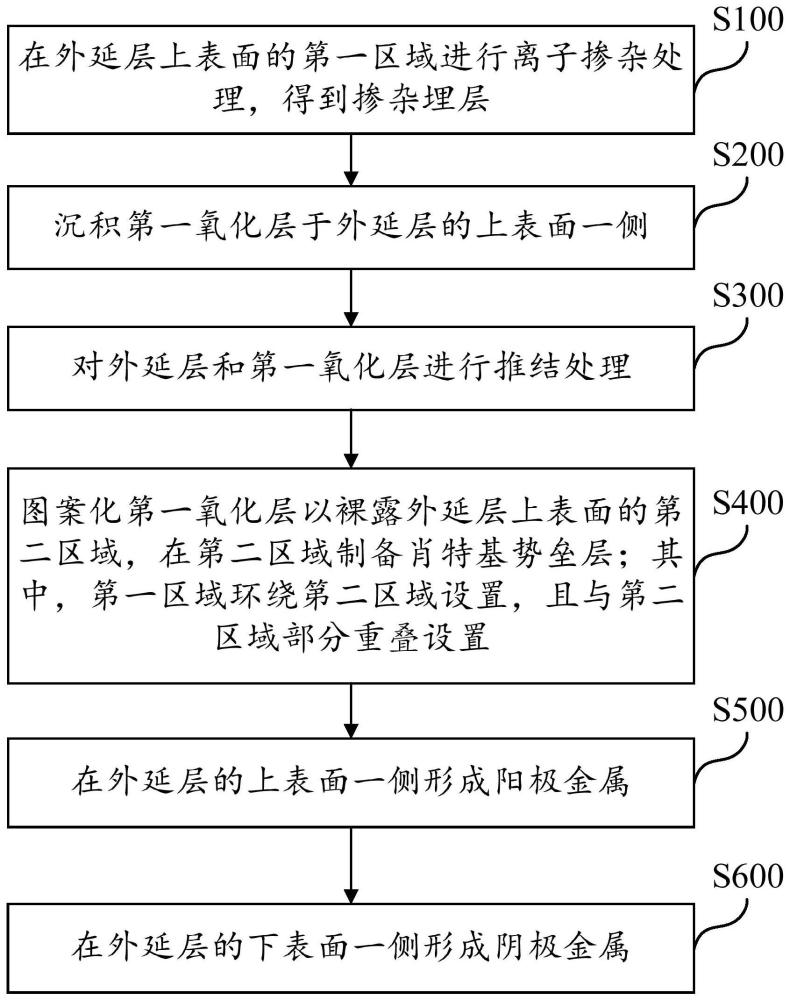

2、为了解决上述技术问题,本申请提供的第一个技术方案为:提供一种二极管的制备方法,其中,包括:

3、在外延层上表面的第一区域进行离子掺杂处理,得到掺杂埋层;

4、沉积第一氧化层于所述外延层的上表面一侧;

5、对所述外延层和所述第一氧化层进行推结处理;

6、图案化所述第一氧化层以裸露所述外延层上表面的第二区域,在所述第二区域制备肖特基势垒层;其中,所述第一区域环绕所述第二区域设置,且与所述第二区域部分重叠设置。

7、其中,所述在外延层上表面的第一区域进行离子掺杂处理,得到掺杂埋层的步骤包括:

8、在所述外延层的上表面生长第二氧化层;

9、刻蚀所述第二氧化层以裸露所述外延层的上表面的所述第一区域;

10、向所述第一区域注入硼离子,以在所述外延层内形成所述掺杂埋层。

11、其中,所述沉积第一氧化层于所述外延层的上表面一侧的步骤包括:

12、采用气相沉积工艺沉积所述第一氧化层,使所述第一氧化层覆盖所述第一区域和所述第二氧化层。

13、其中,所述对所述外延层和所述第一氧化层进行推结处理的步骤包括:

14、采用氮气对所述第一氧化层进行退火处理;

15、对所述外延层和所述第一氧化层进行推结处理,推结温度大于1000摄氏度。

16、其中,所述图案化所述第一氧化层以裸露所述外延层上表面的第二区域,在所述第二区域制备肖特基势垒层的步骤包括:

17、刻蚀所述第一氧化层和所述第二氧化层,以裸露所述外延层上表面的第二区域;

18、采用真空蒸发或溅射的方法在所述第二区域淀积一层势垒金属层;并对所述势垒金属层和所述外延层进行低温处理,形成所述肖特基势垒层;所述肖特基势垒层覆盖部分所述掺杂埋层。

19、其中,所述掺杂埋层的厚度小于100埃;所述肖特基势垒层的厚度小于100埃,且小于所述掺杂埋层的厚度。

20、其中,所述第一氧化层的厚度为5000埃±1000埃。

21、其中,所述掺杂埋层的导电类型为p型,所述外延层的导电类型为n型。

22、其中,所述图案化所述第一氧化层以裸露所述外延层上表面的第二区域,在所述第二区域制备肖特基势垒层的步骤之后还包括:

23、在所述外延层的上表面一侧形成阳极金属。

24、其中,所述图案化所述第一氧化层以裸露所述外延层上表面的第二区域,在所述第二区域制备肖特基势垒层的步骤之后还包括:

25、在所述外延层的下表面一侧形成阴极金属。

26、本申请的有益效果:区别于现有技术,本申请提供了一种二极管的制备方法,二极管的制备方法包括:在外延层上表面的第一区域进行离子掺杂处理,得到掺杂埋层;沉积第一氧化层于外延层的上表面一侧;对外延层和第一氧化层进行推结处理;图案化第一氧化层以裸露外延层上表面的第二区域,在第二区域制备肖特基势垒层;其中,第一区域环绕第二区域设置,且与第二区域部分重叠设置。本申请通过在推结处理前采用沉积的方式形成第一氧化层,替代现有技术中在推结处理过程中采用热氧化的方式形成第一氧化层,从而在推结处理过程中避免掺杂埋层中掺杂离子纵向扩散出外延层的表面,以及在推结处理后避免掺杂埋层中掺杂离子纵向扩散出外延层的上表面,相比于现有技术,本申请可以进一步防止掺杂埋层中的掺杂离子浓度的降低,能显著提升二极管的esd能力。

技术特征:

1.一种二极管的制备方法,其特征在于,包括:

2.根据权利要求1所述的二极管的制备方法,其特征在于,所述在外延层上表面的第一区域进行离子掺杂处理,得到掺杂埋层的步骤包括:

3.根据权利要求2所述的二极管的制备方法,其特征在于,所述沉积第一氧化层于所述外延层的上表面一侧的步骤包括:

4.根据权利要求2所述的二极管的制备方法,其特征在于,所述对所述外延层和所述第一氧化层进行推结处理的步骤包括:

5.根据权利要求2所述的二极管的制备方法,其特征在于,所述图案化所述第一氧化层以裸露所述外延层上表面的第二区域,在所述第二区域制备肖特基势垒层的步骤包括:

6.根据权利要求5所述的二极管的制备方法,其特征在于,所述掺杂埋层的厚度小于100埃;所述肖特基势垒层的厚度小于100埃,且小于所述掺杂埋层的厚度。

7.根据权利要求1所述的二极管的制备方法,其特征在于,所述第一氧化层的厚度为5000埃±1000埃。

8.根据权利要求1所述的二极管的制备方法,其特征在于,所述掺杂埋层的导电类型为p型,所述外延层的导电类型为n型。

9.根据权利要求1所述的二极管的制备方法,其特征在于,所述图案化所述第一氧化层以裸露所述外延层上表面的第二区域,在所述第二区域制备肖特基势垒层的步骤之后还包括:

10.根据权利要求1所述的二极管的制备方法,其特征在于,所述图案化所述第一氧化层以裸露所述外延层上表面的第二区域,在所述第二区域制备肖特基势垒层的步骤之后还包括:

技术总结

本申请提供了一种二极管的制备方法。二极管的制备方法包括:在外延层上表面的第一区域进行离子掺杂处理,得到掺杂埋层;沉积第一氧化层于外延层的上表面一侧;对外延层和第一氧化层进行推结处理;图案化第一氧化层以裸露外延层上表面的第二区域,在第二区域制备肖特基势垒层;第一区域环绕第二区域设置,且与第二区域部分重叠设置。本申请通过在推结处理前采用沉积的方式形成第一氧化层,替代现有技术中在推结处理过程中通过热氧化形成第一氧化层,从而在推结处理过程中以及在推结处理后,避免掺杂埋层中掺杂离子纵向扩散出外延层的上表面,相比于现有技术,本申请可以进一步防止掺杂埋层中的掺杂离子浓度的降低,能显著提升二极管的ESD能力。

技术研发人员:李京兵,王钢,石晓宇,杨忠武,王国峰

受保护的技术使用者:青岛惠科微电子有限公司

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!