功率MOSFET器件结构及其制造方法与流程

本技术涉及半导体,具体涉及一种功率mosfet器件结构及其制造方法。

背景技术:

1、现代电力电子装置正朝着高功率密度和高效率的方向发展。碳化硅功率器件因其卓越的高压、高频、高温和高功率密度等器件特性,近年来在高效电能转换领域得到了迅速发展。碳化硅器件的卓越性能来自于碳化硅材料的宽禁带特征,使碳化硅器件可以承受很高的反向偏压。碳化硅器件的终端受pn结边缘电场的集中效应的限制,通常会远小于材料所预期的理论值,如何设计碳化硅器件的终端结构尽可能缓解边缘电场的集中效应就成为高击穿电压碳化硅器件研发的一个关键环节。目前主流的设计有结终端延伸(junctiontermination extension,jte)和场限环(field limit ring,flr)两种结构,但jte结构存在对表面电荷敏感,容易受到界面电荷的影响,影响器件击穿电压及可靠性;而flr结构设计复杂,同时flr结构带来的不利影响是终端区占据芯片总面积大,不利于提高电流密度。

技术实现思路

1、本技术的目的在于,本技术实施例提供一种功率mosfet器件结构及其制造方法,以解决现有技术中存在的问题,具有至少一个优点:减小该功率mosfet器件结构的终端尺寸的同时,增加了该功率mosfet器件的耐压性能。

2、根据本技术的一方面,本技术一实施例提供了一种功率mosfet器件结构,包括:

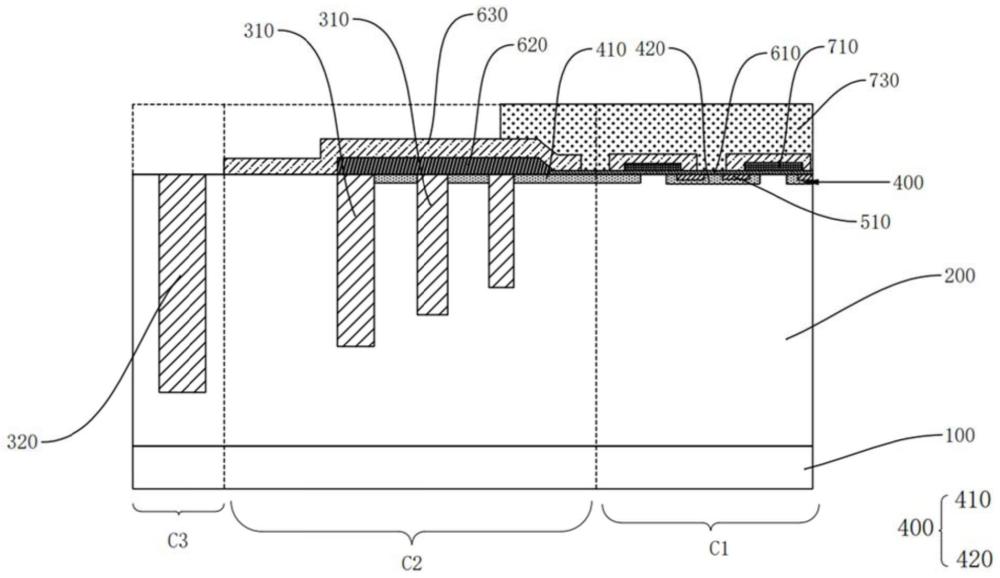

3、碳化硅衬底,以及设置在所述碳化硅衬底上的轻掺杂的n型外延层,其中,所述n型外延层包括有源区、环绕所述有源区设置的终端区和环绕所述终端区设置的切割道区;

4、在所述终端区的所述n型外延层中嵌设有多个第一氧化硅柱,在所述n型外延层的厚度方向上,每个所述第一氧化硅柱的高度至少大于或者等于所述n型外延层厚度的1/3,并且所述第一氧化硅柱的一侧端面从所述n型外延层背离所述碳化硅衬底的一侧表面露出;

5、p型结注入层,所述p型结注入层嵌设于所述n型外延层中,其中,沿平行于所述n型外延层所在平面的方向,所述p型结注入层在所述终端区的截止位置设置在距离所述切割道区最近的一个第一氧化硅柱的背离所述切割道区的一侧。

6、在一些实施方式中,沿所述切割道区指向所述终端区的方向,多个所述第一氧化硅柱的截面深度递减,多个所述第一氧化硅柱的截面宽度递减。

7、在一些实施方式中,沿平行于所述n型外延层所在平面的方向,每个所述第一氧化硅柱呈环形,多个所述第一氧化硅柱呈同心设置。

8、在一些实施方式中,多个所述第一氧化硅柱的数量大于或者等于3个,其中,相邻两个所述第一氧化硅柱之间的间距相等。

9、在一些实施方式中,在所述切割道区的所述n型外延层中嵌设有至少一个第二氧化硅柱,并且所述第二氧化硅柱的一侧端面从所述n型外延层背离所述碳化硅衬底的一侧露出;

10、所述第二氧化硅柱的截面深度大于距离所述切割道区最近的一个第一氧化硅柱的截面深度;

11、所述第二氧化硅柱的截面宽度大于距离所述切割道区最近的一个第一氧化硅柱的截面宽度。

12、在一些实施方式中,在所述终端区和在所述有源区,p型结注入层注入所述n型外延层中的深度一致,并且在所述碳化硅衬底的厚度方向上,所述p型结注入层背离所述碳化硅衬底的一侧表面与所述n型外延层背离所述碳化硅衬底的一侧表面平齐。

13、在一些实施方式中,沿平行于所述n型外延层所在平面的方向,所述p型结注入层包括第一p型结注入体和第二p型结注入体,其中,所述第一p型结注入体由所述终端区延伸至所述有源区内,所述第二p型结注入体位于所述有源区内。

14、在一些实施方式中,在所述终端区还设置有场氧化层和包覆所述场氧化层的绝缘介电层,所述场氧化层位于所述n型外延层的背离所述碳化硅衬底的一侧表面,所述场氧化层覆盖于所述多个第一氧化硅柱和部分所述第一p型结注入体,且所述场氧化层与所述多个第一氧化硅柱露出的端面以及所述第一p型结注入体直接接触。

15、根据本技术的另一方面,还提供了一种功率mosfet器件结构的制造方法,所述方法包括:

16、提供具有轻掺杂的n型外延层的碳化硅衬底,其中,所述n型外延层包括有源区、环绕所述有源区设置的终端区和环绕所述终端区设置的切割道区;

17、刻蚀所述n型外延层,以形成对应目标区域的多个沟槽,所述沟槽在厚度方向上至少贯穿所述n型外延层厚度的1/3以上;

18、在所述沟槽内形成第一氧化硅层,所述第一氧化硅层覆盖于所述沟槽的内壁以及位于所述沟槽附近的所述n型外延层的表面;

19、在所述沟槽内形成多晶硅材料层,所述多晶硅材料层覆盖于所述第一氧化硅层,并对所述多晶硅材料层进行氧化处理,以得到氧化硅材料层;

20、去除位于所述n型外延层表面的所述氧化硅材料层,使得所述n型外延层的表面露出,以得到多个氧化硅柱;

21、形成p型结注入层,沿平行于所述n型外延层所在平面的方向上,所述p型结注入层在所述终端区的截止位置设置在距离所述切割道区最近的一个氧化硅柱的背离所述切割道区的一侧。

22、在一些实施方式中,沿所述切割道区指向所述终端区的方向,多个所述沟槽的截面深度递减,多个所述沟槽的截面宽度递减。

23、在一些实施方式中,沿平行于所述n型外延层所在平面的方向,每个所述沟槽呈环形,多个所述沟槽呈同心设置。

24、在一些实施方式中,多个所述沟槽的数量大于或者等于3个,其中,相邻两个所述沟槽之间的间距相等。

25、在一些实施方式中,所述多个氧化硅柱包括位于所述终端区的多个第一氧化硅柱和位于所述切割道区的至少一个第二氧化硅柱。

26、所述第二氧化硅柱的截面深度大于距离所述切割道区最近的一个第一氧化硅柱的截面深度;

27、所述第二氧化硅柱的截面宽度大于距离所述切割道区最近的一个第一氧化硅柱的截面宽度。

28、在一些实施方式中,所述刻蚀所述n型外延层,以形成对应目标区域的多个沟槽的方法包括:

29、在所述n型外延层上形成第零氧化硅层;

30、刻蚀所述第零氧化硅层,以形成对应所述目标区域的多个镂空槽,所述镂空槽在厚度方向上贯穿所述第零氧化硅层;

31、通过所述镂空槽处刻蚀所述n型外延层,以形成多个所述沟槽;

32、去除位于所述n型外延层上的剩余所述第零氧化硅层。

33、在一些实施方式中,所述去除位于所述n型外延层表面的所述氧化硅材料层,以得到多个氧化硅柱的方法包括:

34、采用cmp工艺对所述氧化硅材料层的表面进行研磨处理,以露出所述n型外延层的表面。

35、在一些实施方式中,在所述终端区和在所述有源区,p型结注入层注入所述n型外延层中的深度一致,并且在所述碳化硅衬底的厚度方向上,所述p型结注入层背离所述碳化硅衬底的一侧表面与所述n型外延层背离所述碳化硅衬底的一侧表面平齐。

36、在一些实施方式中,沿平行于所述n型外延层所在平面的方向,所述p型结注入层包括第一p型结注入体和第二p型结注入体,其中,所述第一p型结注入体由所述终端区延伸至所述有源区内,所述第二p型结注入体位于所述有源区内。

37、在一些实施方式中,所述方法还包括:

38、形成场氧化层和包覆所述场氧化层的绝缘介电层,所述场氧化层位于所述终端区内,所述场氧化层覆盖于所述多个第一氧化硅柱和部分所述第一p型结注入体,且所述场氧化层与所述多个第一氧化硅柱的端部以及所述第一p型结注入体直接接触。

39、本技术技术方案的优点在于:利用嵌设于n型外延层中的多个第一氧化硅柱作为硬隔离,起到表面隔离的作用,可以有效阻挡界面态和表面可动离子在外延电场作用下的移动,进而提升功率mosfet器件的可靠性。通过在终端区的n型外延层内设置多个第一氧化硅柱与p型结注入层相配合组成终端环,以将位于终端区内体结的耗尽层展宽,进而实现在较小的终端尺寸内,提升功率mosfet器件结构的击穿电压。

- 还没有人留言评论。精彩留言会获得点赞!