一种晶体管的制备方法及晶体管

本发明涉及半导体,尤其涉及一种晶体管的制备方法及晶体管。

背景技术:

1、薄膜晶体管(thin film transistor,tft)是一种特殊类型的场效应晶体管,它是通过在称为基板的柔性材料上简单地沉积有源半导体薄膜、介电层和栅电极层而制成的。

2、传统的tft器件普遍采用单栅结构,器件性能不可动态调控,往往不能根据实际应用的需要进行灵活的调控,因此图1中的双栅结构的tft器件结构被提出。这种结构可以在一定范围内调控tft的阈值电压,器件的稳定性也优于单栅结构器件。如图1所示,双栅结构的tft包括背栅、绝缘体、沟道区、源极/漏极、沟道钝化层、顶栅。根据应用背栅和顶栅是由金属制成,背栅和顶栅可以触发源极和漏极之间的接触或者改变晶体管的阈值电压。绝缘体和沟道钝化层是由绝缘材料制成,用于避免沟道区和栅电极之间的电短路。源极和漏极是晶体管的电极层,根据应用是由导体制成。

3、这种双栅晶体管是基于一种典型的三明治结构,半导体沟道区被两层栅介质夹在中间,其也可以看作是一个背栅晶体管和顶栅晶体管共用沟道的复合晶体管。由于这种双栅晶体管具有极低的关态电流、高迁移率以及低温沉积等特点,使得其在显示、动态随机存取存储器(dynamic random access memory,dram)和三维集成等高密度、高集成度应用中,底层的tft会出现阈值电压漂移的问题,影响tft性能的稳定性。

技术实现思路

1、鉴于上述的分析,本发明实施例旨在提供一种晶体管的制备方法及晶体管,用以解决现有技术中薄膜晶体管在高密度、高集成度应用中出现阈值电压漂移的问题。

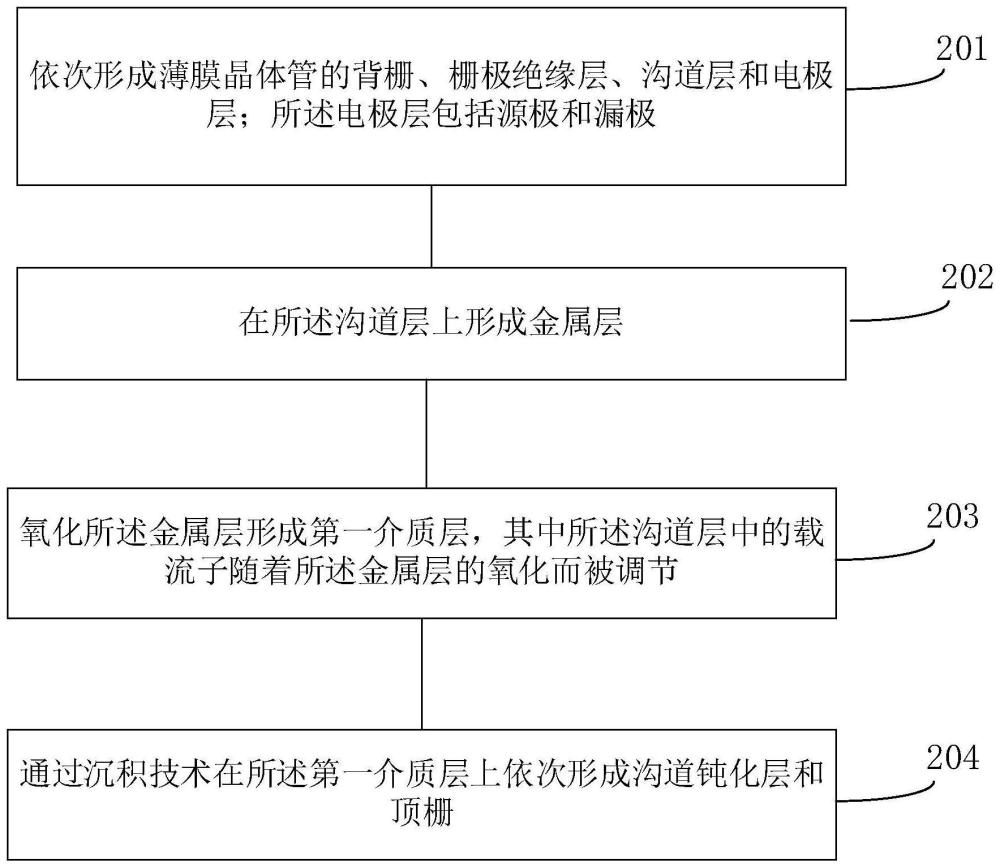

2、一方面,本发明实施例提供了一种晶体管的制备方法,包括如下步骤:

3、依次形成薄膜晶体管的背栅、栅极绝缘层、沟道层和电极层;所述电极层包括源极和漏极;

4、在所述沟道层上形成金属层;

5、氧化所述金属层形成第一介质层,其中所述沟道层中的载流子随着所述金属层的氧化而被调节;以及

6、通过沉积技术在所述第一介质层上依次形成沟道钝化层和顶栅。

7、基于上述方法的进一步改进,在所述沟道层上形成金属层包括:

8、采用磁控溅射沉积法或等离子体增强化学的气相沉积法在所述沟道层上沉积预定厚度的钽或铝并图形化。

9、基于上述方法的进一步改进,氧化所述金属层形成第一介质层包括:

10、将所述金属层置于高温、氧气环境下以氧化所述金属层,其中所述沟道层中的氧空位随着所述金属层的氧化而被调节。

11、基于上述方法的进一步改进,所述金属层的厚度是根据所述薄膜晶体管的阈值电压漂移程度确定的。

12、基于上述方法的进一步改进,通过沉积技术形成沟道层包括:

13、采用磁控溅射沉积法或原子层沉积法在栅极绝缘层上沉积4纳米至10纳米厚的氧化铟镓锌并图形化。

14、基于上述方法的进一步改进,通过沉积技术在所述第一介质层上形成沟道钝化层包括:

15、采用原子层沉积法依次在所述第一介质层上沉积第二介质层和第三介质层,其中,所述第二介质层和所述第三介质层的厚度之和为6纳米至30纳米,或者

16、采用原子层沉积法沉积第二介质层,其中,所述第二介质层的厚度为6纳米至30纳米。

17、基于上述方法的进一步改进,所述采用原子层沉积法依次沉积第二介质层和第三介质层包括:

18、采用原子层沉积法沉积2纳米厚的氧化铪;以及

19、采用原子层沉积法沉积8纳米厚的氧化铝。

20、基于上述方法的进一步改进,通过沉积技术形成薄膜晶体管的电极层或顶栅包括:

21、采用电子束沉积法沉积20纳米至60纳米厚的镍或金并剥离;或者,

22、采用原子层沉积法沉积20纳米至60纳米厚的氧化铟锌并图形化。

23、另一方面,本发明实施例提供了一种晶体管,包括:

24、薄膜晶体管的背栅、栅极绝缘层、沟道层、电极层、沟道钝化层、顶栅以及位于所述薄膜晶体管的沟道层和沟道钝化层之间的第一介质层;

25、其中,所述第一介质层的材料为金属氧化物且在所述第一介质层被氧化之前,所述第一介质层的材料为金属材料;

26、其中,所述沟道层中的载流子随着所述金属材料的氧化而被调节。

27、基于上述方法的进一步改进,所述金属层的材料为钽,所述第一介质层的材料为氧化钽。

28、与现有技术相比,本发明至少可实现如下有益效果之一:

29、1、本发明提供的晶体管可以根据要求调节薄膜晶体管的阈值电压,从而改善薄膜晶体管由于其极低的关态电流、高迁移率以及低温沉积等特点,使得其在显示、动态随机存取存储器(dynamic random access memory,dram)和三维集成等高密度、高集成度应用中出现的阈值电压漂移的问题。

30、2、本发明提供的晶体管利用了氧化钽高介电常数的特性,从而提供了更好的隔离效果,进一步缓解了薄膜晶体管由于其极低的关态电流、高迁移率以及低温沉积等特点,使得其在显示、动态随机存取存储器(dynamic random access memory,dram)和三维集成等高密度、高集成度应用中出现的阈值电压漂移的问题。

31、本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

技术特征:

1.一种晶体管的制备方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的晶体管的制备方法,其特征在于,在所述沟道层上形成金属层包括:

3.根据权利要求2所述的晶体管的制备方法,其特征在于,氧化所述金属层形成第一介质层包括:

4.根据权利要求2所述的晶体管的制备方法,其特征在于,所述金属层的厚度是根据所述薄膜晶体管的阈值电压漂移程度确定的。

5.根据权利要求1或2所述的晶体管的制备方法,其特征在于,通过沉积技术形成沟道层包括:

6.根据权利要求1或2所述的晶体管的制备方法,其特征在于,通过沉积技术在所述第一介质层上形成沟道钝化层包括:

7.根据权利要求6所述的晶体管的制备方法,其特征在于,所述采用原子层沉积法依次沉积第二介质层和第三介质层包括:

8.根据权利要求1所述的晶体管的制备方法,其特征在于,通过沉积技术形成薄膜晶体管的电极层或顶栅包括:

9.一种晶体管,其特征在于,包括:

10.根据权利要求9所述的晶体管,其特征在于,所述金属层的材料为钽,所述第一介质层的材料为氧化钽。

技术总结

本发明涉及一种晶体管的制备方法及晶体管,属于半导体技术领域,解决了现有技术中薄膜晶体管在高密度、高集成度应用中出现的阈值电压漂移问题。该晶体管的制备方法包括如下步骤:依次形成薄膜晶体管的背栅、栅极绝缘层、沟道层和电极层;所述电极层包括源极和漏极;在所述沟道层上形成金属层;氧化所述金属层形成第一介质层,其中所述沟道层中的载流子随着所述金属层的氧化而被调节;以及通过沉积技术在所述第一介质层上依次形成沟道钝化层和顶栅。

技术研发人员:杨冠华,廖福锡,李泠

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!