避免晶圆边缘电弧放电的钝化层刻蚀方法、结构及应用与流程

本发明涉及半导体加工,尤其涉及一种避免晶圆边缘电弧放电的钝化层刻蚀方法、结构及应用。

背景技术:

1、在半导体集成电路制造工艺中,钝化层(passivation)作为集成电路器件和金属连线的保护结构,一方面提供一定的应力缓冲,使器件不被后续切割、清洗、封装等工艺破坏,另一方面保护产品免受潮气、沾污及保护内部结构不被腐蚀。

2、钝化层使用的介电材料通常为氧化硅和氮化硅,其结构通常是先沉积一层或多层sio2,最后沉积一层致密的si3n4。后端钝化层蚀刻工艺主要用于对钝化层开口以形成焊盘(pad),通常采用等离子体刻蚀钝化层,由于其特有的较高的射频功率(rf power),导致其成为发生晶圆电弧放电频率最高的工艺制程,这也是目前集成电路钝化层蚀刻(passivation etch)工艺面临的主要常见问题之一,电弧放电区域通常为晶圆标记(wafermark)、划片槽(scribe line)、封闭环(seal ring)、晶圆边缘等区域。

3、晶圆边缘区域发生电弧放电主要有两种情况:

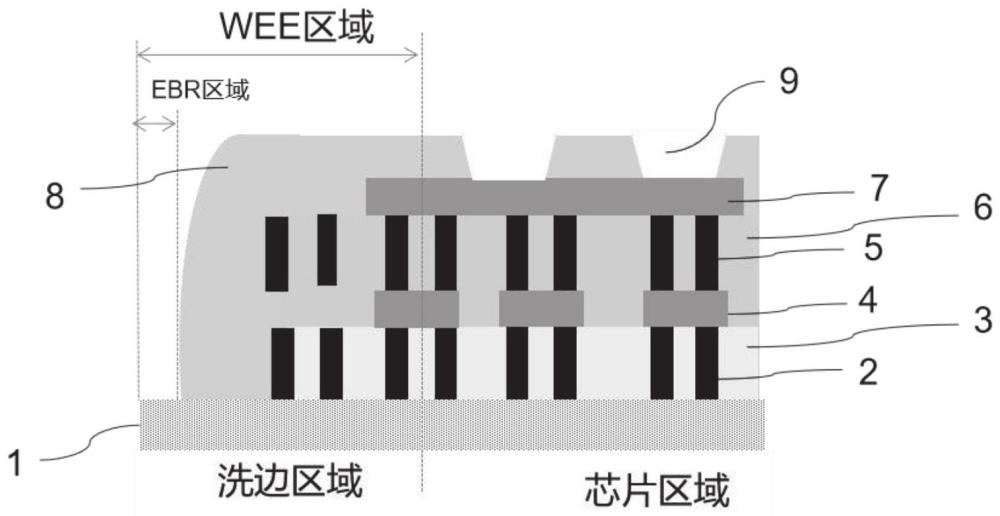

4、1.不健康的洗边条件:如图1所示,当metal层洗边小于ct层或者via层洗边时,边缘区域的via层钨塞就处于floating状态。在钝化层蚀刻步骤,晶圆边缘开窗时,大量电荷就会在这些钨塞附近聚集,由于钨塞处于floating状态,无法及时通过金属导线导出聚集的电荷。当电荷达到一定能量时,就会发生电弧放电,损坏晶圆;

5、2.边缘对位不准:如图2所示,晶圆边缘附近,形貌最差,高低起伏严重,可能会引起metal与via层对位不准。这也会造成floating状态的钨塞,引起电弧放电,损坏晶圆。

6、由此可见,目前的芯片制造工艺,容易在钝化层蚀刻步骤,在晶圆边缘发生电弧放电,引起晶圆良率损失。尤其对一些质量卡控较严的产品,只要晶圆发生电弧放电,不管对晶圆损伤多大,整片晶圆都需要报废,造成了成本的巨大损失。

技术实现思路

1、针对现有技术的不足,本发明的目的在于提供一种避免晶圆边缘电弧放电的钝化层刻蚀方法、结构及应用。

2、为实现前述发明目的,本发明采用的技术方案包括:

3、第一方面,本发明提供一种避免晶圆边缘电弧放电的钝化层刻蚀方法,其包括:

4、提供晶圆,所述晶圆包括衬底以及形成于所述衬底表面的芯片层,所述芯片层表面覆盖有钝化层,且所述衬底的边缘凸出于所述芯片层的边缘;

5、在所述钝化层的表面覆盖负性光刻胶层,且所述负性光刻胶层还覆盖所述钝化层和芯片层边缘的侧壁;

6、在处于所述晶圆中部的芯片区进行图案化曝光,以使未被曝光的部分所述负性光刻胶层能够被显影去除;

7、对处于所述晶圆边缘的边缘区进行边缘曝光;

8、对经过所述图案化曝光和边缘曝光的所述负性光刻胶层进行显影,形成图案化开口;

9、利用所述图案化开口,对所述钝化层进行等离子体刻蚀。

10、第二方面,本发明还提供一种上述钝化层刻蚀方法在制备半导体器件中的应用。

11、第三方面,本发明还提供一种钝化层刻蚀结构,所述钝化层刻蚀结构形成于晶圆上,所述晶圆包括处于处于所述晶圆中部的芯片区以及处于所述晶圆边缘的边缘区,且所述晶圆的表面覆设有钝化层;所述芯片区内的所述钝化层经刻蚀形成有贯通所述钝化层的钝化开口,所述边缘区的钝化层为连续钝化层,未形成所述钝化开口。

12、基于上述技术方案,与现有技术相比,本发明的有益效果至少包括:

13、本发明利用边缘的光刻胶层和钝化层保护晶圆边缘的部分未良好电连接的导电结构,防止边缘电弧放电的发生,从而显著提高了晶圆钝化层刻蚀时的良率,具有极佳的应用前景。

14、上述说明仅是本发明技术方案的概述,为了能够使本领域技术人员能够更清楚地了解本申请的技术手段,并可依照说明书的内容予以实施,以下以本发明的较佳实施例并配合详细附图说明如后。

技术特征:

1.一种避免晶圆边缘电弧放电的钝化层刻蚀方法,其特征在于,包括:

2.根据权利要求1所述的钝化层刻蚀方法,其特征在于,在进行所述显影时,处于所述边缘区的负性光刻胶层得以保留;在进行所述等离子体刻蚀时,处于所述边缘区的所述钝化层未与所述等离子体接触。

3.根据权利要求1所述的钝化层刻蚀方法,其特征在于,所述芯片层包括垂直互联结构以及水平互联亚层,处于所述边缘区的部分所述垂直互联结构存在未与对应的所述水平互联亚层连接的状态。

4.根据权利要求3所述的钝化层刻蚀方法,其特征在于,沿远离所述衬底的方向,所述芯片层依次包括半导体层、第一介质层、第一水平互联亚层、第二介质层和第二水平互联亚层;

5.根据权利要求4所述的钝化层刻蚀方法,其特征在于,处于所述边缘区的部分所述第二垂直结构未与所述第二水平互联亚层相连接。

6.根据权利要求1所述的钝化层刻蚀方法,其特征在于,还包括:

7.根据权利要求1所述的钝化层刻蚀方法,其特征在于,所述钝化层采用化学气相沉积的方式进行制备。

8.权利要求1-7中任意一项所述的钝化层刻蚀方法在制备半导体器件中的应用。

9.一种钝化层刻蚀结构,其特征在于,所述钝化层刻蚀结构形成于晶圆上,所述晶圆包括处于处于所述晶圆中部的芯片区以及处于所述晶圆边缘的边缘区,且所述晶圆的表面覆设有钝化层;

10.根据权利要求9所述的钝化层刻蚀结构,其特征在于,所述钝化层形成于芯片层的表面,所述芯片层包括垂直互联结构以及水平互联亚层,处于所述边缘区的部分所述垂直互联结构存在未与对应的所述水平互联亚层连接的状态。

技术总结

本发明公开了一种避免晶圆边缘电弧放电的钝化层刻蚀方法、结构及应用。所述钝化层刻蚀方法包括:提供晶圆,晶圆包括衬底以及芯片层,芯片层表面覆盖有钝化层,且衬底的边缘凸出于芯片层的边缘;在钝化层的表面覆盖负性光刻胶层,且负性光刻胶层还覆盖边缘的侧壁;在芯片区进行图案化曝光,未被曝光的部分负性光刻胶层能够被显影去除;对边缘区进行边缘曝光;对经过图案化曝光和边缘曝光的负性光刻胶层进行显影,形成图案化开口;利用图案化开口,对钝化层进行等离子体刻蚀。本发明利用边缘的光刻胶层和钝化层保护晶圆边缘的部分未良好电连接的导电结构,防止边缘电弧放电的发生,从而显著提高了晶圆钝化层刻蚀时的良率,具有极佳的应用前景。

技术研发人员:赵勇

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!