芯片封装结构及封装芯片的制作方法

本申请涉及芯片封装,具体涉及一种芯片封装结构及封装芯片。

背景技术:

1、目前,在芯片封装领域,制作扇出型板级封装(fan out panel level packaging,foplp)时,一般采用塑封工艺来完成封装,并在塑封材料基础上制作其他功能层;但塑封工艺中采用塑封材料需要通过热压工艺成型,并且受到基板、芯片的约束,产生局部热应力,使得整个封装件发生翘曲问题,不仅使后续制程工艺难度变大,而且容易产生器件失效等问题。

技术实现思路

1、本申请实施例提供了一种芯片封装结构及封装芯片,在芯片单元底部设置不同高度的垫层,以改善芯片封装中出现的局部热应力问题,抑制塑封层热压后冷却时产生的翘曲问题。

2、一方面,根据本申请实施例提供一种芯片封装结构,包括:载板,包括第一表面;垫层,垫层包括至少一个垫片部;芯片层,包括至少一个芯片单元,至少一个芯片单元设置于垫片部远离载板的一侧;塑封层,盖覆于芯片层。

3、根据本申请实施例的一个方面,垫层为图案化膜层,垫片部呈阵列分布;优选的,多个芯片单元中的一部分的芯片单元一对一对应设置于垫片部远离载板的一侧,另一部分的芯片单元与第一表面之间未设置垫片部。

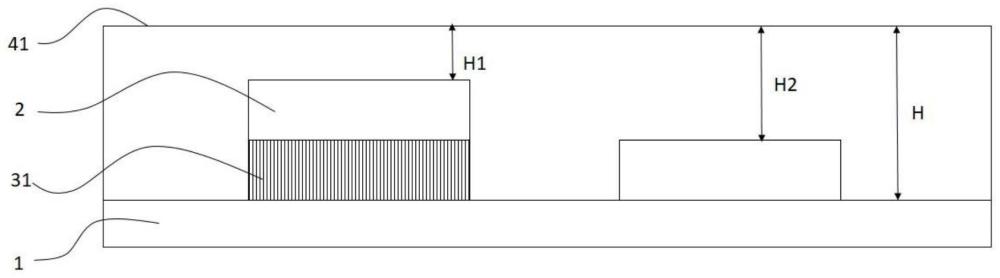

4、根据本申请实施例的一个方面,塑封层远离载板的表面与第一表面之间的最小间距h、设置于垫片部的芯片单元的远离载板的表面至塑封层远离载板的表面的最小间距h1与另一部分的芯片单元的远离载板的表面至塑封层远离载板的表面的最小间距h2满足关系h1<h2<h。

5、根据本申请实施例的一个方面,第一表面包括中部区域和边缘区域,边缘区域围绕中部区域分布,多个垫片部在边缘区域相互间隔设置。

6、根据本申请实施例的一个方面,相邻两个垫片部由第一表面延伸厚度相异。

7、根据本申请实施例的一个方面,第一表面包括多个芯片组定位区域,各芯片组定位区域分布有至少三个芯片单元,第二芯片单元位于第一芯片单元与第三芯片单元之间,第一芯片单元与第一表面之间未设置垫片部,第二芯片单元和第三芯片单元设置于垫片部远离载板的一侧。

8、根据本申请实施例的一个方面,第二芯片单元下方的垫片部的厚度d2与第三芯片单元下方的垫片部的厚度d3不相等。

9、根据本申请实施例的一个方面,芯片单元在第一表面的正投影面积sd与垫片部在第一表面的正投影面积s满足关系sd<s。

10、根据本申请实施例的一个方面,垫片部在第一表面的正投影面积s随垫片部的厚度增加呈递增趋势。

11、又一方面,根据本申请实施例提供一种封装芯片,包括:垫层,垫层包括至少一个垫片部;芯片层,包括至少一个芯片单元,至少一个所述芯片单元设置于垫片部的一侧;塑封层,盖覆于芯片单元;金属布线层,设于塑封层,金属布线层包括引脚和过孔连接部,引脚通过过孔连接部与芯片单元电相连;保护层,盖覆于金属布线层,引脚通过金属布线层露出。

12、本申请实施例提供的芯片封装结构及封装芯片,通过在芯片单元底部设置高度各异的垫层结构,防止翘曲形变量在局部位置朝向同一方向积累,抑制出现影响后续制程工艺,使得器件失效的严重翘曲问题。

技术特征:

1.一种芯片封装结构,其特征在于,包括:

2.根据权利要求1所述的芯片封装结构,其特征在于,所述垫层为图案化膜层,所述垫片部呈阵列分布;

3.根据权利要求1所述的芯片封装结构,其特征在于,所述塑封层远离所述载板的表面与所述第一表面之间的最小间距h、所述设置于所述垫片部的所述芯片单元的远离所述载板的表面至所述塑封层远离所述载板的表面的最小间距h1与所述另一部分的芯片单元的远离所述载板的表面至所述塑封层远离所述载板的表面的最小间距h2满足关系h1<h2<h。

4.根据权利要求1所述的芯片封装结构,其特征在于,所述第一表面包括中部区域和边缘区域,所述边缘区域围绕所述中部区域分布,所述多个垫片部在所述边缘区域相互间隔设置。

5.根据权利要求1所述的芯片封装结构,其特征在于,相邻两个所述垫片部厚度相异。

6.根据权利要求1所述的芯片封装结构,其特征在于,所述第一表面包括多个芯片组定位区域,各所述芯片组定位区域分布有至少三个所述芯片单元,所述第二芯片单元位于所述第一芯片单元与所述第三芯片单元之间,所述第一芯片单元与所述第一表面之间未设置所述垫片部,所述第二芯片单元和第三芯片单元设置于所述垫片部远离所述载板的一侧。

7.根据权利要求6所述的芯片封装结构,其特征在于,所述第二芯片单元下方的所述垫片部的厚度d2与所述第三芯片单元下方的所述垫片部的厚度d3不相等。

8.根据权利要求1所述的芯片封装结构,其特征在于,所述芯片单元在所述第一表面的正投影面积sd与所述垫片部在所述第一表面的正投影面积s满足关系sd<s。

9.根据权利要求8所述的芯片封装结构,其特征在于,所述垫片部在所述第一表面的正投影面积s随所述垫片部的厚度增加呈递增趋势。

10.一种封装芯片,其特征在于,包括:

技术总结

本申请公开了一种芯片封装结构及封装芯片,芯片封装结构包括:载板,包括第一表面;垫层,垫层包括至少一个垫片部;芯片层,包括至少一个芯片单元,至少一个芯片单元设置于垫片部远离载板的一侧;塑封层,盖覆于芯片层。本申请实施例提供的芯片封装结构及封装芯片,通过在芯片单元底部设置高度各异的垫层结构,防止翘曲形变量在局部位置朝向同一方向积累,抑制出现影响后续制程工艺,使得器件失效的严重翘曲问题。

技术研发人员:张文斌,吕奎,周衍旭

受保护的技术使用者:昆山国显光电有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!