一种扇出型封装结构的制造方法及封装结构与流程

本发明属于半导体集成电路制造,具体涉及一种扇出型封装结构的制造方法及封装结构。

背景技术:

1、随着电子技术的发展以及高性能计算、大数据、5g和人工智能应用的快速兴起,对集成电路功能、性能和功耗的要求不断提高,相应的半导体技术集成电路的规模和复杂程度日益增加。延续传统摩尔定律,追求先进技术节点,不断缩小晶体管尺寸的发展路线的技术难度和成本也极大提高。与此同时,在现有技术节点上依托先进封装技术,实现多芯片异质集成的系统级封装(sip)成为当前延续摩尔定律的重要途径,2.5d/3d封装技术将成为先进封装领域的技术高地。

2、重布线层(rdl)是先进封装技术的要素之一,高密度的扇出型封装结构离不开多层rdl的堆叠和临时键合工艺。当rdl的堆叠层数过多时,制程中反复的热处理和湿法工艺对临时键合层的耐候性是一个严峻的考验,工艺良率和成本将是不得不考虑的问题。

3、异质集成结构中,器件的耐候性和对互连工艺的需求都存在显著差异,统一采用高节点工艺完成布线的思路从良率和成本方面考虑都是不明智的,因此,亟需探索新的封装结构和工艺路线,采用有针对性的分级集成可能是解决上述问题的有效途径。

技术实现思路

1、为解决现有技术中存在的技术问题,本发明的目的在于提供一种扇出型封装结构的制造方法及封装结构。

2、为实现上述目的,达到上述技术效果,本发明采用的技术方案为:

3、一种扇出型封装结构的制造方法,包括以下步骤:

4、在载板上贴装基板;

5、在基板上进行一级集成;

6、对基板和一级集成进行塑封;

7、将基板与载板解键合;

8、在塑封形成的塑封体正面制备重布线层,所述重布线层上设置二级集成;

9、在重布线层上完成植球、回流、电性检测和激光打标,再切分成单颗产品,检测合格后包装出货;

10、在将基板与载板解键合之后、在制备重布线层之前进行二级集成,或在进行一级集成的同时进行二级集成。

11、进一步的,在载板上贴装基板的步骤包括:

12、先在载板上制备临时键合层,再将若干个基板逐一贴装至临时键合层上,所述基板为有机基板,所述基板内含多层金属布线且表面带有焊盘;

13、在基板上进行一级集成的步骤包括:

14、将若干芯片或若干芯片和若干无源器件贴装到基板上,并确保芯片和无源器件分别与基板上对应的焊盘形成有效电气连接;

15、进行二级集成的步骤包括:

16、在将基板与载板解键合之后、在制备重布线层之前,或在进行一级集成的同时将芯片贴装至能够与基板解键合的载板上。

17、进一步的,本发明公开了其中一个实施例的一种扇出型封装结构的制造方法,包括以下步骤:

18、第一步,来料晶圆的预处理

19、在来料晶圆上制备用于倒装焊接的芯片,所述芯片包括pillar结构和/或bga结构;

20、第二步,在载板ⅰ上制备临时键合层ⅰ;

21、第三步,将若干个基板逐一贴装至临时键合层ⅰ上;

22、第四步,芯片倒装贴装与回流焊

23、将第一步预处理过的芯片倒装贴装到基板上,通过回流焊后将芯片与基板上对应的焊盘形成有效电气连接;

24、第五步,进行倒装的芯片的底填充,完成一级集成;

25、第六步,一次塑封

26、采用塑封料ⅰ通过压模塑封将芯片和基板整体包覆;

27、第七步,塑封料ⅰ背部或塑封料ⅰ背部和芯片同步减薄;

28、第八步,将基板与载板ⅰ解键合;

29、第九步,将第八步所得半成品以基板为单位切分成单颗;

30、第十步,芯片正面朝下贴装

31、将待封装的芯片以及第九步切割后的产品,面朝下贴装到带有临时键合层ⅱ的载板ⅱ上,完成二级集成;

32、第十一步,二次塑封

33、采用塑封料ⅱ通过压模塑封将第十步贴装的芯片以及第九步切割后的产品整体包覆;

34、第十二步,将载板ⅱ与基板解键合;

35、第十三步,在采用塑封料ⅱ形成的塑封体的正面制备重布线层ⅰ;

36、第十四步,完成植球、回流、电性检测和激光打标;

37、第十五步,将第十四步所得产品切分成单颗产品,检测合格后包装出货。

38、进一步的,第五步中,采用底填充胶ⅰ对芯片进行底填充;底填充分为键合后底填充和键合前底填充两大类;其中,采用键合后底填充路线时,需要将液态胶水点涂至芯片指定位置,然后通过毛细作用力完成填充,随后加热固化;采用键合前底填充路线时,本步骤应当提前至芯片倒装贴装之前,键合前底填充采用液态的无流动底填料或固态的绝缘胶膜作为底填充胶,在芯片倒装贴装前通过点胶或贴膜的方式铺设到指定位置,然后进行芯片倒装贴装,底填充胶材在热处理中完成固化;

39、第六步中,若选用具有底填充功能的液态塑封料进行一次塑封,则省略第五步。

40、进一步的,第八步中,所述基板与载板ⅰ之间通过uv减黏、激光烧蚀界面层或热发泡减黏进行解键合,若基板与载板ⅰ之间通过uv减黏或激光烧蚀界面层进行解键合,则要求载板ⅰ在uv波段或激光工作波段透明。

41、进一步的,第十二步中,所述基板与载板ⅱ之间通过uv减黏、激光烧蚀界面层或热发泡减黏进行解键合,若基板与载板ⅱ之间通过uv减黏或激光烧蚀界面层进行解键合,则要求载板ⅱ在uv波段或激光工作波段透明。

42、进一步的,本发明还公开了其中一个实施例的一种扇出型封装结构的制造方法,包括以下步骤:

43、第一步,来料晶圆的预处理

44、在来料晶圆上制备用于倒装焊接的芯片,所述芯片包括pillar结构和/或bga结构;

45、第二步,在载板ⅰ上制备临时键合层ⅰ;

46、第三步,将若干个基板逐一贴装至临时键合层ⅰ上;

47、第四步,将第一步预处理过的芯片和无源器件倒装贴装到基板上,将待贴装的芯片贴装至临时键合层ⅰ上,通过回流焊后将芯片和无源器件分别与基板上对应的焊盘形成有效电气连接;

48、第五步,进行倒装的芯片和无源器件的底填充,完成一级集成和二级集成;

49、第六步,采用塑封料ⅲ通过压模塑封将芯片、无源器件和基板整体包覆;

50、第七步,将基板与载板ⅰ解键合;

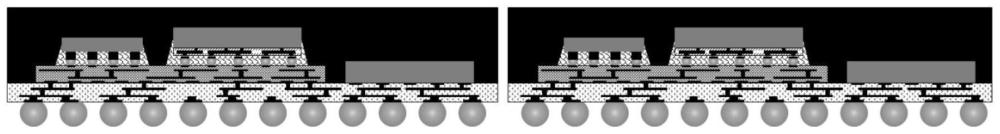

51、第八步,在采用塑封料ⅲ形成的塑封体的正面制备重布线层ⅱ;

52、第九步,完成植球、回流、电性检测和激光打标;

53、第十步,将第九步所得半成品切分成单颗产品,检测合格后包装出货。

54、进一步的,第七步中,所述基板与载板ⅰ之间通过uv减黏、激光烧蚀界面层或热发泡减黏进行解键合,若基板与载板ⅰ之间通过uv减黏或激光烧蚀界面层进行解键合,则要求载板ⅰ在uv波段或激光工作波段透明。

55、进一步的,第五步中,采用底填充胶ⅱ对基板上的芯片和无源器件进行底填充;底填充分为键合后底填充和键合前底填充两大类;其中,采用键合后底填充路线时,需要将液态胶水点涂至芯片和无源器件指定位置,然后通过毛细作用力完成填充,随后加热固化;采用键合前底填充路线时,本步骤应当提前至芯片和无源器件倒装贴装之前,键合前底填充采用液态的无流动底填料或固态的绝缘胶膜作为底填充胶ⅱ,在芯片和无源器件倒装贴装前通过点胶或贴膜的方式铺设到指定位置,然后再进行芯片和无源器件的倒装贴装,底填充胶材在进一步的热处理中完成固化;

56、若第六步选用具有底填充功能的液态塑封料进行塑封,则第五步省略。

57、本发明还公开了一种扇出型封装结构,采用如上所述的一种扇出型封装结构的制造方法制备得到,所述封装结构包括基板,所述基板上设置有一级集成,所述一级集成包括若干芯片或若干芯片和若干无源器件,所述芯片和无源器件与基板上对应的焊盘形成有效电气连接,所述基板、芯片和无源器件塑封于塑封体内,所述塑封体正面设置重布线层,所述重布线层上植球,所述重布线层上设置二级集成。

58、与现有技术相比,本发明的有益效果为:

59、本发明公开了一种扇出型封装结构的制造方法及封装结构,该方法包括以下步骤:在载板上贴装基板;在基板上进行一级集成;对基板和一级集成进行塑封;将基板与载板解键合;在塑封形成的塑封体正面制备重布线层,所述重布线层上设置二级集成;在重布线层上完成植球、回流、电性检测和激光打标,再切分成单颗产品,检测合格后包装出货;在将基板与载板解键合之后、在制备重布线层之前进行二级集成,或在进行一级集成的同时进行二级集成。本发明提供的扇出型封装结构的制造方法及封装结构,将若干芯片或若干芯片和若干无源器件贴装到基板上后,若载板上已贴装芯片,则对芯片、无源器件、基板进行塑封,再将基板与载板解键合,并在塑封形成的塑封体正面制备重布线层,在重布线层上完成植球、回流、电性检测和激光打标,切分成单颗产品,检测合格后包装出货,若载板上未贴装芯片,则需经过两次塑封,直至将所有芯片、无源器件、基板进行塑封,再将基板与载板解键合,并在塑封形成的塑封体正面制备重布线层,在重布线层上完成植球、回流、电性检测和激光打标,切分成单颗产品,检测合格后包装出货;本发明可应对高密度集成、多级别集成,可实现有源和无源器件的异质集成,面向更复杂的应用场景,可分级集成,满足不同器件的集成需求,降低工艺难度和材料要求,提高生产良率,可兼容晶圆级和大板级扇出型封装技术,适合进行工业化推广使用。

- 还没有人留言评论。精彩留言会获得点赞!