半导体结构的制作方法

本申请涉及半导体制造领域,尤其涉及一种半导体结构。

背景技术:

1、随着功率mosfet技术的不断发展,出现了沟槽型mosfet(trench mosfet)。沟槽型mosfet的最大优点在于其能够增加平面器件的沟道密度,以提高器件的电流处理能力。然而,目前的沟槽型mosfet的栅极结构底部承受较高的电场,且栅漏电荷(qgd)较大。

技术实现思路

1、本申请要解决的技术问题是如何降低栅极结构底部的电场,并减少栅漏电荷。

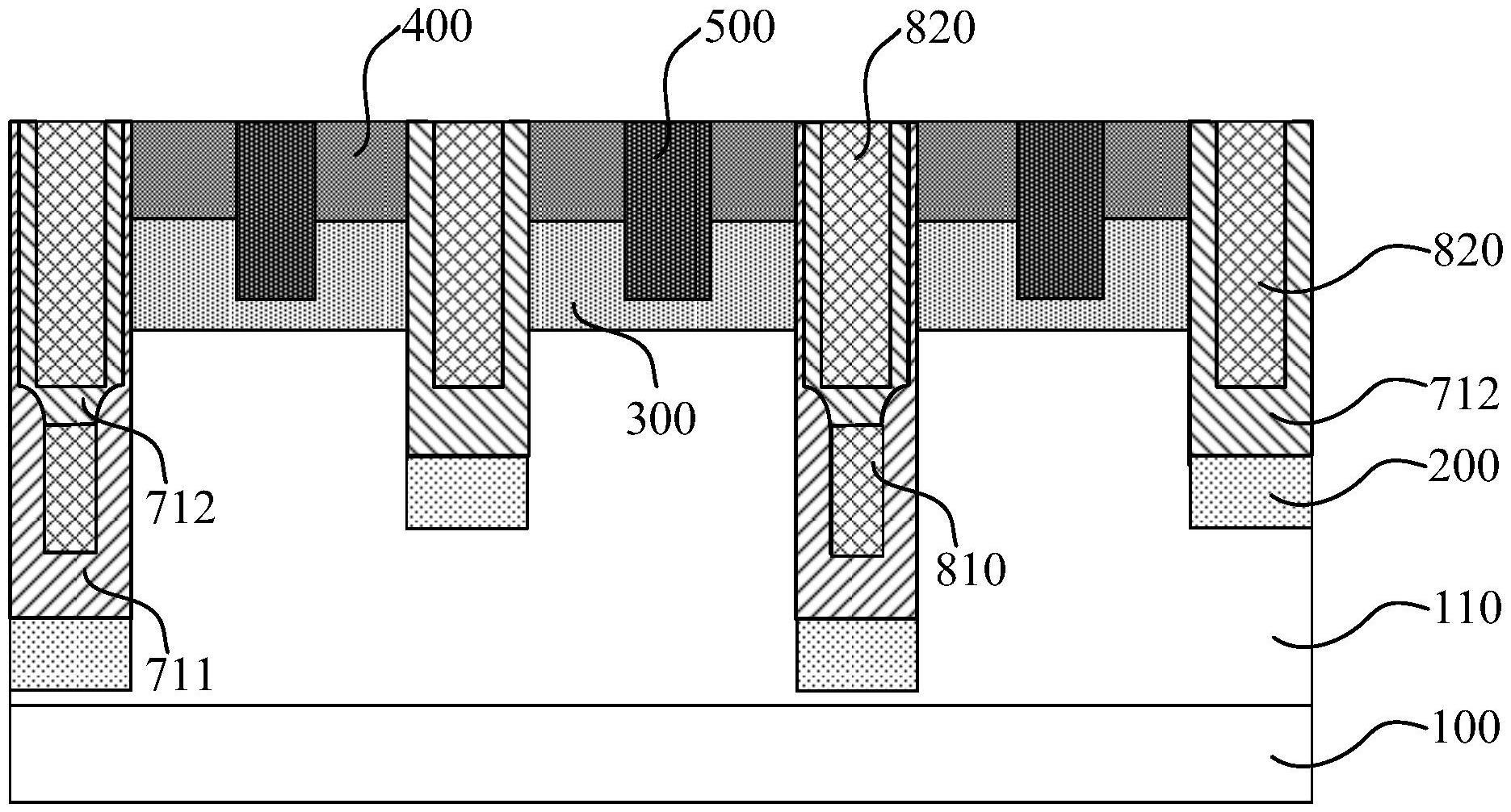

2、为解决上述技术问题,本申请提供了一种半导体结构,包括:衬底,所述衬底上包括外延层;第一掺杂区,位于所述外延层中,且所述第一掺杂区呈高低错落分布;阱区,自所述外延层的表面延伸至所述外延层中;源区,分立的自所述阱区的表面延伸至阱区中;第二掺杂区,位于相邻所述源区间,且自所述阱区表面延伸至所述阱区中,或者延伸出所述阱区;第一栅极结构和第二栅极结构,交替分布于所述源极、所述阱区及所述外延层中,其中所述第一栅极结构位于较低位置的所述第一掺杂区的表面,所述第二栅极结构位于较高位置的所述第一掺杂区的表面,且所述第一栅极结构和所述第二栅极结构均包括栅极,其中所述第一栅极结构还包括位于所述栅极下方的伪栅,所述栅极和所述伪栅的侧壁和底部覆盖有栅介质层。

3、在本申请的一些实施例中,所述第一栅极结构的宽度为0.6μm~3.0μm,深度为1.5μm~3.0μm,且在所述第一栅极结构中,所述伪栅侧壁的所述栅介质层的厚度为50nm~300nm,所述伪栅和所述栅极之间的所述栅介质层的厚度为50nm~300nm,所述伪栅底部的所述栅介质层的厚度为100nm~500nm,所述栅极侧壁的所述栅介质层的厚度为15nm~150nm,所述伪栅的高度为0.5μm~1.0μm,所述栅极的高度为0.6μm~1.8μm。

4、在本申请的一些实施例中,所述第二栅极结构的宽度为0.6μm~3.0μm,深度为1.0μm~2.0μm,且在所述第二栅极结构中,所述栅极的高度为0.6μm~1.8μm,所述栅极侧壁的所述栅介质层的厚度为15nm~150nm,所述栅极底部的所述栅介质层的厚度为100nm~500nm。

5、在本申请的一些实施例中,相邻所述第一栅极结构和所述第二栅极结构之间的间距为0.6μm~3.0μm。

6、在本申请的一些实施例中,所述栅极和所述伪栅的材料包括多晶硅,所述栅介质层的材料包括high-k材料和/或二氧化硅。

7、在本申请的一些实施例中,所述第一掺杂区的高度为0.2μm~1.5μm。

8、在本申请的一些实施例中,所述源区的深度为0.2μm~0.8μm,所述第二掺杂区的深度为0.3μm~1.8μm,所述第二掺杂区的宽度为0.2μm~1.5μm,所述阱区的深度为0.5μm~1.5μm。

9、在本申请的一些实施例中,所述外延层和所述源区具有第一掺杂类型,所述第一掺杂区、所述阱区、所述第二掺杂区具有第二掺杂类型,且所述第一掺杂类型和所述第二掺杂类型相反。

10、在本申请的一些实施例中,所述第一栅极结构和所述第二栅极结构及部分所述源区的表面还包括绝缘层,所述绝缘层的厚度为100nm~500nm。

11、在本申请的一些实施例中,所述半导体结构还包括源极金属,且所述源极金属位于其余所述源区、所述第二掺杂区及所述绝缘层的表面。

12、与现有技术相比,本申请技术方案的半导体结构具有如下有益效果:

13、所述半导体结构在源极、阱区及外延层中第一栅极结构和第二栅极结构,且所述第一栅极结构和所述第二栅极结构均包括栅极,该栅极作为mos管的栅极部分,所述第一栅极结构还包括伪栅,所述伪栅位于所述第一栅极结构的栅极下方,可以作为场板,提供电场夹持效应。同时,所述第一栅极结构和第二栅极结构交替分布,能够相对增加mos管的密度。

14、所述第一栅极结构和所述第二栅极结构下方还设置第一掺杂区,所述第一掺杂区可以降低栅介质层的电场,从而提高栅介质层的可靠性,减少栅漏电荷。同时,所述第一掺杂区还能够阻止基面错位缺陷的扩散,改善导电性。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第一栅极结构的宽度为0.6μm~3.0μm,深度为1.5μm~3.0μm,且在所述第一栅极结构中,所述伪栅侧壁的所述栅介质层的厚度为50nm~300nm,所述伪栅和所述栅极之间的所述栅介质层的厚度为50nm~300nm,所述伪栅底部的所述栅介质层的厚度为100nm~500nm,所述栅极侧壁的所述栅介质层的厚度为15nm~150nm,所述伪栅的高度为0.5μm~1.0μm,所述栅极的高度为0.6μm~1.8μm。

3.根据权利要求1所述的半导体结构,其特征在于,所述第二栅极结构的宽度为0.6μm~3.0μm,深度为1.0μm~2.0μm,且在所述第二栅极结构中,所述栅极的高度为0.6μm~1.8μm,所述栅极侧壁的所述栅介质层的厚度为15nm~150nm,所述栅极底部的所述栅介质层的厚度为100nm~500nm。

4.根据权利要求1所述的半导体结构,其特征在于,相邻所述第一栅极结构和所述第二栅极结构之间的间距为0.6μm~3.0μm。

5.根据权利要求1所述的半导体结构,其特征在于,所述栅极和所述伪栅的材料包括多晶硅,所述栅介质层的材料包括high-k材料和/或二氧化硅。

6.根据权利要求1所述的半导体结构,其特征在于,所述第一掺杂区的高度为0.2μm~1.5μm。

7.根据权利要求1所述的半导体结构,其特征在于,所述源区的深度为0.2μm~0.8μm,所述第二掺杂区的深度为0.3μm~1.8μm,所述第二掺杂区的宽度为0.2μm~1.5μm,所述阱区的深度为0.5μm~1.5μm。

8.根据权利要求1所述的半导体结构,其特征在于,所述外延层和所述源区具有第一掺杂类型,所述第一掺杂区、所述阱区、所述第二掺杂区具有第二掺杂类型,且所述第一掺杂类型和所述第二掺杂类型相反。

9.根据权利要求1所述的半导体结构,其特征在于,所述第一栅极结构和所述第二栅极结构及部分所述源区的表面还包括绝缘层,所述绝缘层的厚度为100nm~500nm。

10.根据权利要求9所述的半导体结构,其特征在于,所述半导体结构还包括源极金属,且所述源极金属位于其余所述源区、所述第二掺杂区及所述绝缘层的表面。

技术总结

本申请技术方案提供一种半导体结构,其中所述半导体结构包括:衬底,所述衬底上包括外延层;第一掺杂区,位于所述外延层中,且所述第一掺杂区呈高低错落分布;阱区,自所述外延层的表面延伸至所述外延层中;源区,分立的自所述阱区的表面延伸至阱区中;第二掺杂区,位于相邻所述源区间,且自所述阱区表面延伸至所述阱区中,或者延伸出所述阱区;第一栅极结构和第二栅极结构,交替分布于所述源极、所述阱区及所述外延层中,且所述第一栅极结构和所述第二栅极结构均包括栅极,其中所述第一栅极结构还包括位于所述栅极下方的伪栅。本申请技术方案的半导体结构可以降低栅极结构底部的电场,并减少栅漏电荷。

技术研发人员:张永杰,李浩南,彭定康,周永昌,三重野文健,黄晓辉,董琪琪

受保护的技术使用者:飞锃半导体(上海)有限公司

技术研发日:20230117

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!