用于屏蔽栅型MOSFET的测试结构和晶圆的制作方法

本技术涉及半导体,具体涉及一种用于屏蔽栅型mosfet的测试结构和晶圆。

背景技术:

1、mosfet(metal-oxide-semiconductor field-effect transistor,金属-氧化物-半导体场效应晶体管)作为集成电路中的重要组成部分,被广泛应用于电源、负载驱动等多个领域。屏蔽栅型mosfet(shield gate trench mosfet,sgt mosfet)是由传统沟槽型mosfet发展而来,在中低电压领域保留了传统沟槽型mosfe的低导通阻抗rds(on)的优点,因具备更快的开关速度和更低的开关损耗等优点得到了广泛的应用。

2、屏蔽栅型mosfet包括位于沟槽内的屏蔽栅和沟道栅。根据屏蔽栅和沟道栅的相对位置关系不同,屏蔽栅型mosfet又可进一步分为不同的类型,如上下分离栅结构和左右分离栅结构。一种典型上下分离栅结构的屏蔽栅型mosfet中,沟道栅位于屏蔽栅的上方且二者之间通过介质层(inter poly oxide,ipo)分隔。

3、现有屏蔽栅型mosfet的制作工艺,大致可包括如下步骤:s1、在外延片上形成沟槽,在沟槽侧壁以及外延层表面生长介质层如氧化层,然后在沟槽内填充多晶硅,且多晶硅层也覆盖于外延层表面的氧化层上,随后对多晶硅进行平坦化处理;s2、在对源区进行保护前提下,对位于栅区的多晶硅进行部分刻蚀,使外延层表面的多晶硅被刻蚀完全,沟槽内多晶硅的表面低于沟槽的顶部;s3、对栅区沟槽内的氧化层进行部分腐蚀,仅保留沟槽内多晶硅下方及侧方的氧化层;s4、在多晶硅顶部以及沟槽侧壁形成介质层如氧化层,其中栅区沟槽内多晶硅顶部形成的氧化层即为ipo,栅区沟槽侧壁的氧化层作为栅氧化层;s5、再次生长多晶硅,使位于栅区的沟槽被多晶硅填充完全,此外外延层和源区表面也会生长一层多晶硅;s6、对多晶硅进行平坦化处理(如化学机械研磨cmp或多晶硅回刻);s7、生长层间介质层(ild)并进行接触孔光刻与刻蚀,将栅极多晶硅与源极多晶硅分别引出,其中源极多晶硅与器件源极通过金属互联。由于源极多晶硅与栅极多晶硅需分别引出,所以源极多晶硅与栅极多晶硅之间的隔离结构即ipo层的隔离质量是器件制作过程中需要重点监控的关键。

4、因此,需要设计一种屏蔽栅型mosfet的测试结构,以对ipo层的制程进行监测。

技术实现思路

1、鉴于上述问题,本实用新型的目的在于提供一种用于屏蔽栅型mosfet的测试结构,以对ipo层进行监测。本实用新型的目的还在于提供一种晶圆,包括上述测试结构以及屏蔽栅型mosfet的管芯。

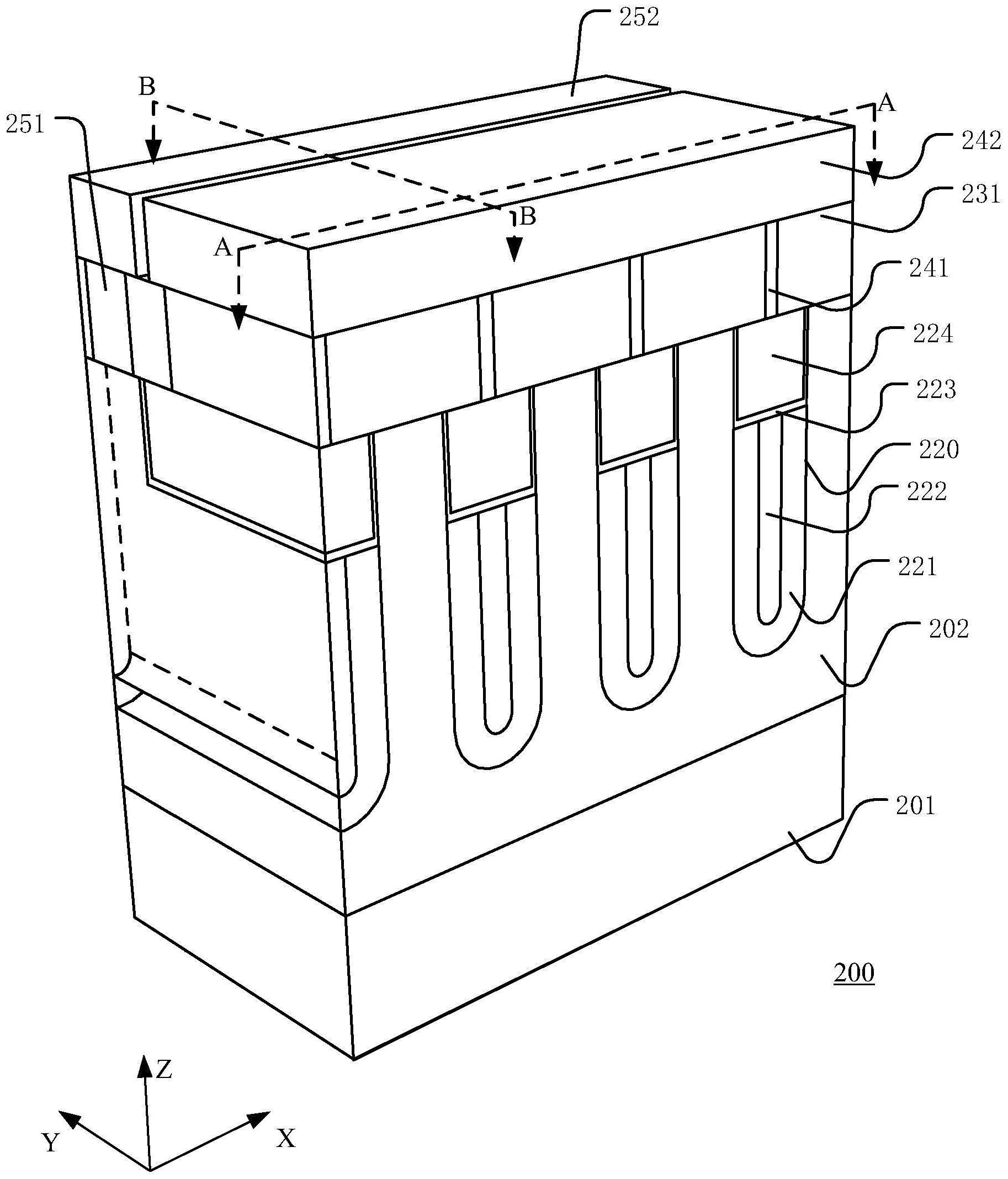

2、根据本实用新型的一方面,提供一种用于屏蔽栅型mosfet的测试结构,与屏蔽栅型mosfet位于同一晶圆中,该测试结构包括:

3、至少一个沟槽;

4、位于沟槽中的第一多晶硅层和第二多晶硅层,以及隔离第一多晶硅层和第二多晶硅层的氧化层;

5、第一导电柱,与第一多晶硅层电连接;

6、第二导电柱,与第二多晶硅层电连接;

7、其中,第一多晶硅层为屏蔽栅型mosfet中屏蔽栅的模拟结构,第二多晶硅层为屏蔽栅型mosfet中沟道栅的模拟结构;第一多晶硅层、氧化层和第二多晶硅层构成电容结构。

8、可选地,第二多晶硅层的底端和部分侧部被第一多晶硅层包围。

9、可选地,第一多晶硅层的顶端与第二多晶硅层的顶端平齐。

10、可选地,还包括:第一电极,与第一导电柱电连接;第二电极,与第二导电柱电连接。

11、可选地,该测试结构位于晶圆的划片槽;或者,该测试结构位于晶圆管芯区域的无效区域。

12、可选地,晶圆包括衬底以及位于衬底上的外延层,沟槽位于衬底和外延层形成的叠层结构中。

13、可选地,还包括:绝缘层,位于第一多晶硅层与叠层结构之间。

14、可选地,前述氧化层包围第二多晶硅层并位于叠层结构中。

15、可选地,测试结构的沟槽与屏蔽栅型mosfet中的沟槽的深度相等。

16、根据本实用新型的另一方面,提供一种晶圆,包括管芯区域和相邻管芯区域之间的划片槽,管芯区域包括屏蔽栅型mosfet,该晶圆还包括如前所述的测试结构,该测试结构位于划片槽或位于管芯区域中的无效区域。

17、本申请提供的用于屏蔽栅型mosfet的测试结构,其中的第一多晶硅层、氧化层以及第二多晶硅层构成一个电容器,两个多晶硅层分别作为电容的上、下极板,氧化层作为电容的层间介质层。通过测量电容器两个电极引出端之间的电连接关系并周期性的监测两个电极引出端之间的电容值,即可判断氧化层的质量是否出现波动。

18、具体而言,若屏蔽栅型mosfet的制造工艺稳定,特别是ipo的形成工艺稳定,则任意时间、不同批次的屏蔽栅型mosfet中,因为对应的测试结构相同,所以其测试数值也应相同或在允许的范围内,由此通过监测该测试结构的电容值是否发生变化,可以间接监测屏蔽栅型mosfet中氧化层的质量。

19、进一步地,基于该测试结构的测试手段简单可行,结果准确。并且由于该测试结构与屏蔽栅型mosfet器件的沟槽同步形成,不增加屏蔽栅型mosfet的制程,并且提升了屏蔽栅型mosfet的可靠性和生产效率,降低了生产成本。

20、本申请提供的晶圆,由于包括上述屏蔽栅型mosfet以及上述用于屏蔽栅型mosfet的测试结构,因而在晶圆加工制程中,可以对屏蔽栅型mosfet的ipo层的质量进行监控,从而可以保证晶圆的加工质量。

技术特征:

1.一种用于屏蔽栅型mosfet的测试结构,与所述屏蔽栅型mosfet位于同一晶圆中,其特征在于,所述测试结构包括:

2.根据权利要求1所述的测试结构,其特征在于,所述第二多晶硅层的底端和部分侧部被所述第一多晶硅层包围。

3.根据权利要求2所述的测试结构,其特征在于,所述第一多晶硅层的顶端与所述第二多晶硅层的顶端平齐。

4.根据权利要求1所述的测试结构,其特征在于,还包括:

5.根据权利要求1-4任一项所述的测试结构,其特征在于,所述测试结构位于所述晶圆的划片槽;或者,所述测试结构位于所述晶圆管芯区域的无效区域。

6.根据权利要求1-4任一项所述的测试结构,其特征在于,所述晶圆包括衬底以及位于所述衬底上的外延层,所述沟槽位于所述衬底和所述外延层形成的叠层结构中。

7.根据权利要求6所述的测试结构,其特征在于,还包括:绝缘层,位于所述第一多晶硅层与所述叠层结构之间。

8.根据权利要求7所述的测试结构,其特征在于,所述氧化层包围第二多晶硅层并位于所述叠层结构中。

9.根据权利要求1所述的测试结构,其特征在于,所述测试结构的沟槽与所述屏蔽栅型mosfet中的沟槽的深度相等。

10.一种晶圆,包括管芯区域和相邻管芯区域之间的划片槽,所述管芯区域包括屏蔽栅型mosfet,其特征在于,还包括如权利要求1-9中任一项所述的测试结构,所述测试结构位于所述划片槽或位于所述管芯区域中的无效区域。

技术总结

本技术公开了一种用于屏蔽栅型MOSFET的测试结构和晶圆,测试结构与屏蔽栅型MOSFET位于同一晶圆中,测试结构包括:至少一个沟槽;位于沟槽中的第一多晶硅层和第二多晶硅层,以及隔离第一多晶硅层和第二多晶硅层的氧化层;第一导电柱,与第一多晶硅层电连接;第二导电柱,与第二多晶硅层电连接;其中,第一多晶硅层为屏蔽栅型MOSFET中屏蔽栅的模拟结构,第二多晶硅层为屏蔽栅型MOSFET中沟道栅的模拟结构;第一多晶硅层、氧化层和第二多晶硅层构成电容结构。该测试结构,通过第一多晶硅层、氧化层与第二多晶硅层组成的电容结构,可以对氧化层进行监测,进而提升屏蔽栅型MOSFET的可靠性和生产效率,降低生产成本。

技术研发人员:朱林迪,陈丽颖,胡磊,王超,常东旭,李静怡

受保护的技术使用者:北京燕东微电子科技有限公司

技术研发日:20230420

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!