半导体结构的制作方法

本技术的实施例涉及半导体结构。

背景技术:

1、存储器内运算(compute-in-memory,cim)及近存储器运算(compute-near-memory,cnm)架构正在兴起,以推动边缘加速器的高能效计算。然而,典型的单片三维集成电路(three-dimensional integrated circuit,3dic)对于此种存储器架构实施方案而言可能是不可行的。具体而言,二维(two-dimensional,2d)系统芯片(system on chip,soc)设计及cim架构的实施方案可能遭受非易失性存储器(non-volatile memory,nvm)功能区块与控制逻辑区块的装置节点不匹配的挑战。此外,采用微凸块(microbump,μbump)技术的三维(3d)堆叠芯片可能无法满足cim架构分区及重新整合的内连线密度要求。

技术实现思路

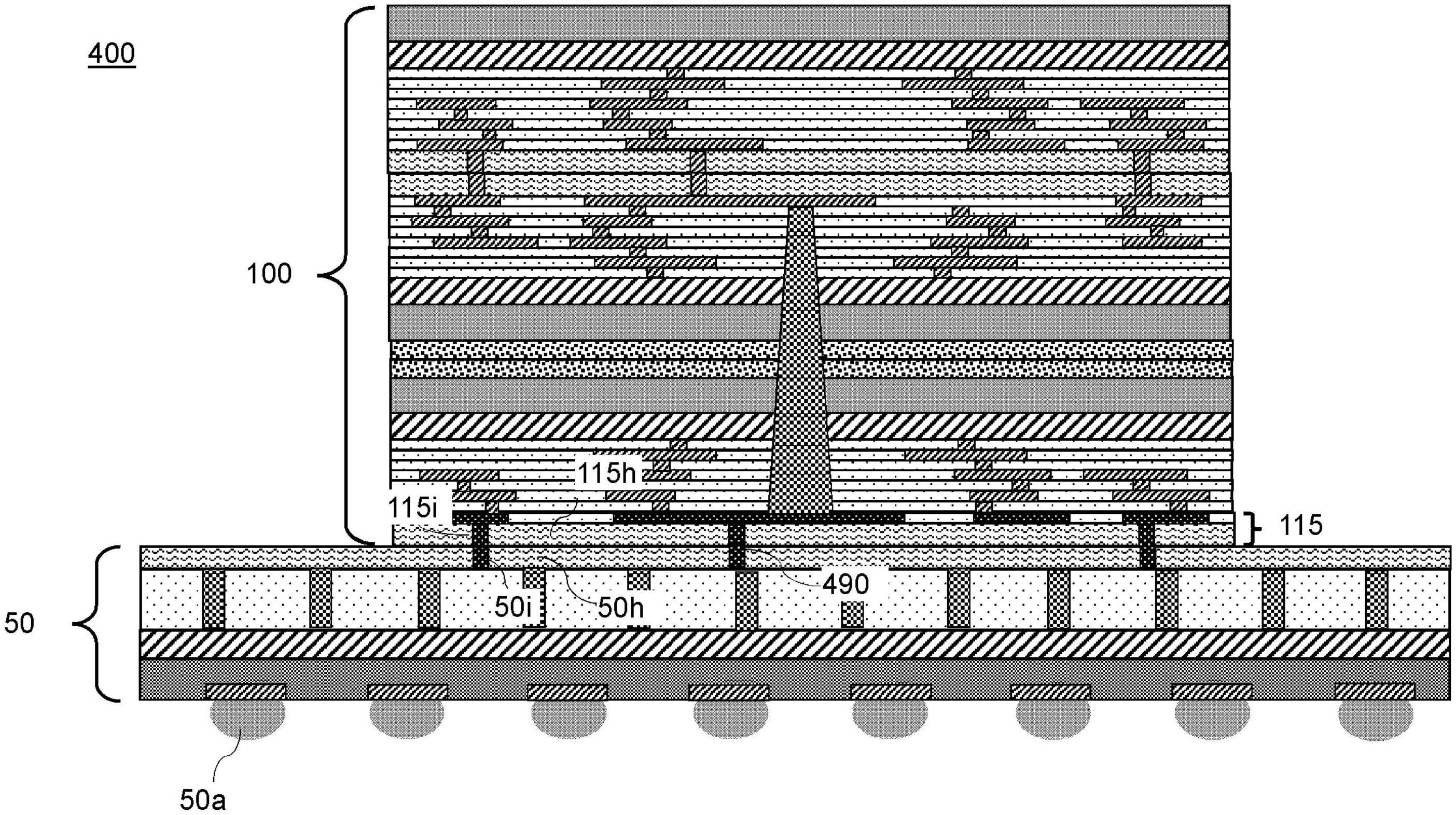

1、本实用新型实施例提供一种半导体结构,包括逻辑管芯;存储器管芯堆叠,藉由第一氧化物结合件结合至所述逻辑管芯,且包括藉由第一直接结合件结合于一起的第一对存储器管芯;以及第一硅穿孔(tsv),位于所述逻辑管芯中且延伸穿过所述第一氧化物结合件且将所述逻辑管芯电性连接至所述第一对存储器管芯。

2、本实用新型实施例提供一种半导体结构,包括基础管芯小芯片;以及顶部管芯小芯片,结合至所述基础管芯小芯片,所述顶部管芯小芯片包括:逻辑管芯;存储器管芯堆叠,藉由第一氧化物结合件结合至所述逻辑管芯,且包括藉由第一直接结合件结合于一起的第一对存储器管芯;以及第一硅穿孔(tsv),位于所述逻辑管芯中且延伸穿过所述第一氧化物结合件且将所述逻辑管芯电性连接至所述第一对存储器管芯。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第一对存储器管芯包括第一存储器管芯及第二存储器管芯,所述第二存储器管芯藉由所述第一直接结合件结合至所述第一存储器管芯且藉由所述第一氧化物结合件结合至所述逻辑管芯。

3.根据权利要求2所述的半导体结构,其特征在于,所述第一硅穿孔将所述逻辑管芯中的金属层连接至所述第二存储器管芯中的金属层。

4.根据权利要求2所述的半导体结构,其特征在于,位于所述第一存储器管芯与所述第二存储器管芯之间的所述第一直接结合件包括面对面结合件,且位于所述逻辑管芯与所述第二存储器管芯之间的所述第一氧化物结合件包括背对背氧化物结合件。

5.根据权利要求2所述的半导体结构,其特征在于,满足以下中的至少一者:

6.根据权利要求1所述的半导体结构,其特征在于,所述存储器管芯堆叠包括:

7.根据权利要求1所述的半导体结构,其特征在于,所述存储器管芯堆叠包括:

8.一种半导体结构,其特征在于,包括:

9.根据权利要求8所述的半导体结构,其特征在于,所述顶部管芯小芯片还包括位于所述逻辑管芯上的连接结构,所述连接结构将所述逻辑管芯电性连接至所述第一硅穿孔且将所述顶部管芯小芯片电性连接至所述基础管芯小芯片。

10.根据权利要求9所述的半导体结构,其特征在于,所述顶部管芯小芯片藉由直接结合件结合至所述基础管芯小芯片,且结合接垫内连线延伸穿过所述直接结合件且将所述顶部管芯小芯片电性连接至所述基础管芯小芯片。

技术总结

一种半导体结构包括:逻辑管芯;存储器管芯堆叠,藉由第一氧化物结合件结合至逻辑管芯,且包括藉由第一直接结合件结合于一起的第一对存储器管芯;以及第一硅穿孔(TSV),位于逻辑管芯中且延伸穿过第一氧化物结合件且将逻辑管芯电性连接至第一对存储器管芯。

技术研发人员:陈颉彦,谢政宪,王垂堂,余振华

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230524

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!